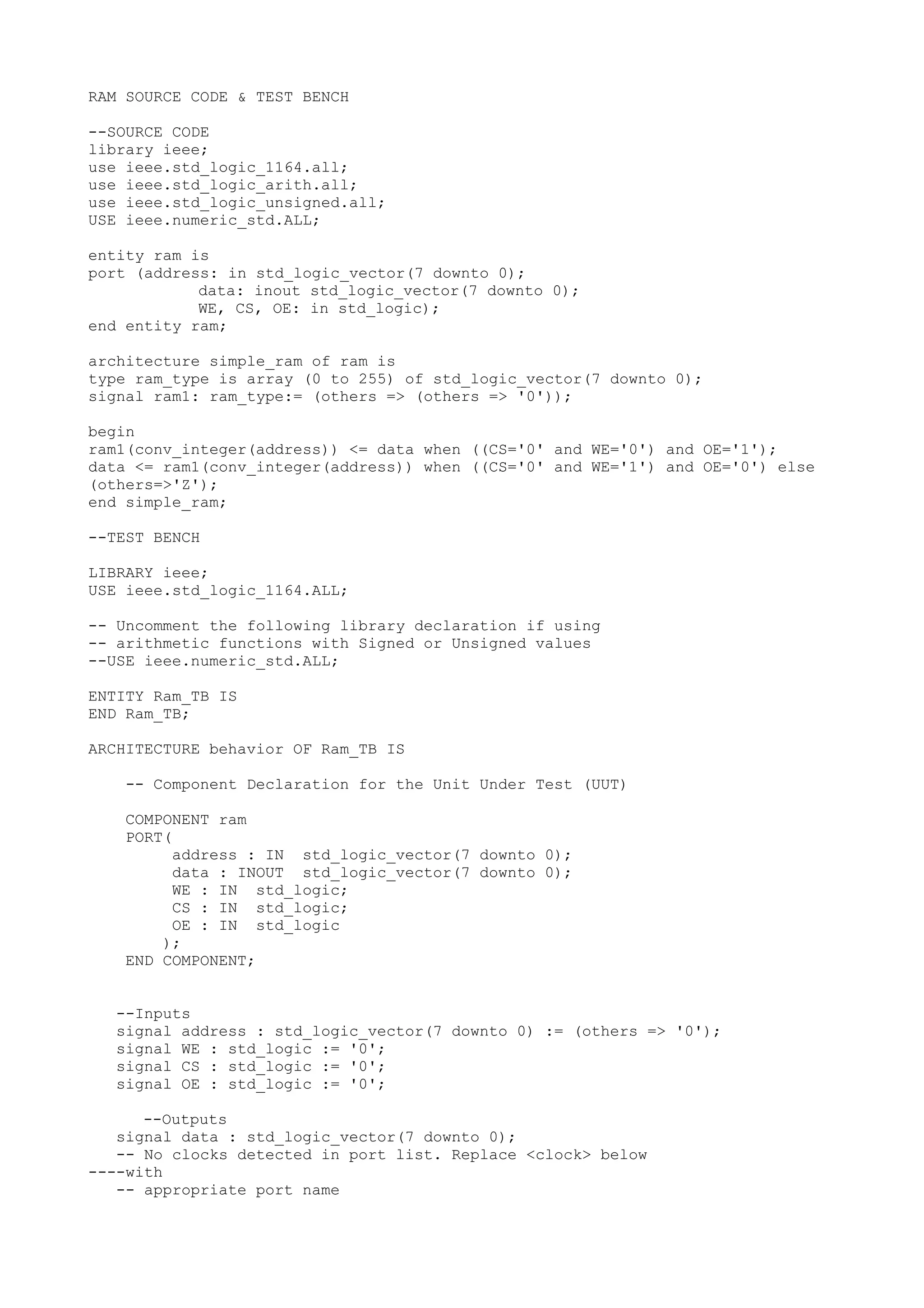

This document contains the source code and test bench for a RAM module. The source code defines an entity for a RAM with an 8-bit address and 8-bit data ports, as well as write enable, chip select, and output enable ports. The architecture defines an 8-bit signal to store the 256 memory locations. The test bench instantiates the RAM entity and applies a stimulus of writing 8 bytes of data to addresses and then reading back the values.