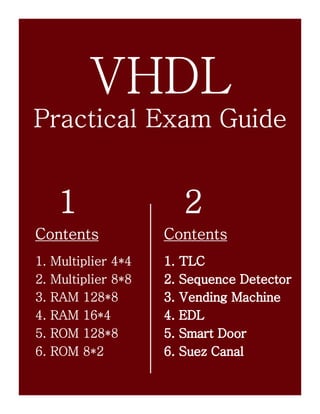

VHDL Practical Exam Guide

- 1. VHDL Practical Exam Guide 1 2 Contents Contents 1. Multiplier 4*4 1. TLC 2. Multiplier 8*8 2. Sequence Detector 3. RAM 128*8 3. Vending Machine 4. RAM 16*4 4. EDL 5. ROM 128*8 5. Smart Door 6. ROM 8*2 6. Suez Canal

- 3. 1 Contents 1. Multiplier 4*4 2. Multiplier 8*8 3. RAM 128*8 4. RAM 16*4 5. ROM 128*8 6. ROM 8*2

- 4. Multiplier 4 bit * 4 bit

- 5. C:FPGAdv52LibrariesSsrc@mult@r@t@l.vhd 11/03/11 13:45:45 -- hds header_start -- -- VHDL Architecture S.Mult.RTL -- -- Created: -- by - Pharaoh.UNKNOWN (S) -- at - 13:07:36 11/03/2011 -- -- Generated by Mentor Graphics' HDL Designer(TM) 2001.5 (Build 170) -- -- hds header_end LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY Mult IS -- Declarations Port ( x,y : In STD_Logic_Vector ( 3 downto 0 ); z : Out STD_Logic_Vector (7 downto 0)); END Mult ; -- hds interface_end ARCHITECTURE RTL OF Mult IS signal pp1: unsigned (3 downto 0); signal pp2: unsigned (4 downto 0); signal pp3: unsigned (5 downto 0); signal pp4: unsigned (6 downto 0); signal ppp1: unsigned (5 downto 0); signal ppp2: unsigned (7 downto 0); signal pppp1: unsigned (7 downto 0); BEGIN pp1 <= unsigned (x) when y(0)='1' else (others => '0'); pp2 <= unsigned (x&'0') when y(1)='1' else (others => '0'); pp3 <= unsigned (x&"00") when y(2)='1' else (others => '0'); pp4 <= unsigned (x&"000") when y(3)='1' else (others => '0'); ppp1 <= ("00"&pp1) + ('0'&pp2); ppp2 <= ("00"&pp3) + ('0'&pp4); pppp1 <= ("00"&ppp1) + ppp2; z <= STD_Logic_Vector(pppp1); END RTL; Page: 1

- 6. Mult 4.4 Simulation Code force -freeze sim:/mult/x 1111 0 force -freeze sim:/mult/y 1010 0 add wave sim:/mult/* run run run run run Page 1

- 7. /mult/x 15 /mult/y 10 /mult/z 150 /mult/pp1 0000 /mult/pp2 11110 /mult/pp3 000000 /mult/pp4 1111000 /mult/ppp1 011110 /mult/ppp2 01111000 /mult/pppp1 10010110 0 100 200 300 400 500 600 700 800 900 1 us Entity:mult Architecture:rtl Date: Fri Dec 30 13:45:41 HDS 2011 Row: 1 Page: 1

- 8. Multiplier 8 bit * 8 bit

- 9. C:FPGAdv52LibrariesSsrc@mult_8@r@t@l.vhd 12/30/11 13:55:20 -- hds header_start -- -- VHDL Architecture S.Mult_8.RTL -- -- Created: -- by - Pharaoh.UNKNOWN (S) -- at - 14:09:52 11/16/2011 -- -- Generated by Mentor Graphics' HDL Designer(TM) 2001.5 (Build 170) -- -- hds header_end LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY Mult_8 IS -- Declarations PORT ( x,y : IN STD_Logic_Vector (7 Downto 0); z : OUT STD_Logic_Vector (15 Downto 0)); END Mult_8 ; -- hds interface_end ARCHITECTURE RTL OF Mult_8 IS Signal p1: unsigned (7 Downto 0); Signal p2: unsigned (8 Downto 0); Signal p3: unsigned (9 Downto 0); Signal p4: unsigned (10 Downto 0); Signal p5: unsigned (11 Downto 0); Signal p6: unsigned (12 Downto 0); Signal p7: unsigned (13 Downto 0); Signal p8: unsigned (14 Downto 0); Signal pp1: unsigned (9 Downto 0); Signal pp2: unsigned (11 Downto 0); Signal pp3: unsigned (13 Downto 0); Signal pp4: unsigned (15 Downto 0); Signal ppp1: unsigned (11 Downto 0); Signal ppp2: unsigned (15 Downto 0); Signal pppp1: unsigned (15 Downto 0); BEGIN p1 <= unsigned (x) when y(0) = '1' else (others => '0'); p2 <= unsigned ( x & '0') when y(1) = '1' else (others => '0'); p3 <= unsigned ( x & "00") when y(2) = '1' else (others => '0'); p4 <= unsigned ( x & "000") when y(3) = '1' else (others => '0'); p5 <= unsigned ( x & "0000") when y(4) = '1' else (others => '0'); p6 <= unsigned ( x & "00000") when y(5) = '1' else (others => '0'); p7 <= unsigned ( x & "000000") when y(6) = '1' else (others => '0'); p8 <= unsigned ( x & "0000000") when y(7) = '1' else (others => '0'); pp1 <= ("00" & p1) + ('0' & p2); pp2 <= ("00" & p3) + ('0' & p4); pp3 <= ("00" & p5) + ('0' & p6); pp4 <= ("00" & p7) + ('0' & p8); ppp1 <= ("00" & pp1) + pp2; ppp2 <= ("00" & pp3) + pp4; pppp1 <= ("0000" & ppp1) + ppp2; z <= STD_Logic_Vector(pppp1); END RTL; Page: 1

- 10. Mult 8.8 Simulation Code force -freeze sim:/mult_8/x 01100100 0 force -freeze sim:/mult_8/y 00001100 0 add wave sim:/mult_8/* run run run run run run Page 1

- 11. /mult_8/x 100 /mult_8/y 12 /mult_8/z 1200 /mult_8/p1 00000000 /mult_8/p2 000000000 /mult_8/p3 0110010000 /mult_8/p4 01100100000 /mult_8/p5 000000000000 /mult_8/p6 0000000000000 /mult_8/p7 00000000000000 /mult_8/p8 000000000000000 /mult_8/pp1 0000000000 /mult_8/pp2 010010110000 /mult_8/pp3 00000000000000 /mult_8/pp4 0000000000000000 /mult_8/ppp1 010010110000 /mult_8/ppp2 0000000000000000 /mult_8/pppp1 0000010010110000 0 500 1 us 1500 2 us Entity:mult_8 Architecture:rtl Date: Fri Dec 30 13:56:15 HDS 2011 Row: 1 Page: 1

- 12. RAM 128 * 8 1024 bit 128 Byte

- 13. C:FPGAdv52LibrariesSsrc@r@a@m_128_8rtl.vhd 12/30/11 12:10:54 -- hds header_start -- -- VHDL Architecture S.RAM_128_8.rtl -- -- Created: -- by - Pharaoh.UNKNOWN (S) -- at - 11:42:32 12/30/2011 -- -- Generated by Mentor Graphics' HDL Designer(TM) 2001.5 (Build 170) -- -- hds header_end LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY RAM_128_8 IS -- Declarations PORT (din: IN STD_Logic_Vector (7 downto 0); dout: OUT STD_Logic_Vector (7 downto 0); addr: IN STD_Logic_Vector ( 6 downto 0); wr,clk: IN STD_Logic); END RAM_128_8 ; -- hds interface_end ARCHITECTURE rtl OF RAM_128_8 IS type mem_type is array (0 to 127) of STD_Logic_vector (7 downto 0); signal mem: mem_type; BEGIN Process (clk) begin if(rising_edge(clk)) then if(wr='1') then mem(conv_integer(unsigned(addr))) <= din; end if; end if; End Process; dout <= mem(conv_integer(unsigned(addr))); END rtl; Page: 1

- 14. RAM 128.8 Simulation Code force -freeze sim:/ram_128_8/clk 1 0, 0 {50 ns} -r 100 force -freeze sim:/ram_128_8/wr 1 0 force -freeze sim:/ram_128_8/addr 0000000 0 force -freeze sim:/ram_128_8/din 00000000 0 force -freeze sim:/ram_128_8/addr 0000000 100 force -freeze sim:/ram_128_8/addr 0000001 200 force -freeze sim:/ram_128_8/addr 0000010 300 force -freeze sim:/ram_128_8/addr 0000011 400 force -freeze sim:/ram_128_8/addr 0000100 500 force -freeze sim:/ram_128_8/addr 0000101 600 force -freeze sim:/ram_128_8/addr 0000110 700 force -freeze sim:/ram_128_8/addr 0000111 800 force -freeze sim:/ram_128_8/addr 0001000 900 force -freeze sim:/ram_128_8/addr 0001001 1000 force -freeze sim:/ram_128_8/din 01100100 100 force -freeze sim:/ram_128_8/din 01100101 200 force -freeze sim:/ram_128_8/din 01100110 300 force -freeze sim:/ram_128_8/din 01100111 400 force -freeze sim:/ram_128_8/din 01101000 500 force -freeze sim:/ram_128_8/din 01101001 600 force -freeze sim:/ram_128_8/din 01101010 700 force -freeze sim:/ram_128_8/din 01101011 800 force -freeze sim:/ram_128_8/din 01101100 900 force -freeze sim:/ram_128_8/din 01101101 1000 force -freeze sim:/ram_128_8/wr 0 1100 force -freeze sim:/ram_128_8/addr 0000000 1200 force -freeze sim:/ram_128_8/addr 0000001 1300 force -freeze sim:/ram_128_8/addr 0000010 1400 force -freeze sim:/ram_128_8/addr 0000011 1500 force -freeze sim:/ram_128_8/addr 0000100 1600 force -freeze sim:/ram_128_8/addr 0000101 1700 force -freeze sim:/ram_128_8/addr 0000110 1800 Page 1

- 15. RAM 128.8 Simulation Code force -freeze sim:/ram_128_8/addr 0000111 1900 force -freeze sim:/ram_128_8/addr 0001000 2000 force -freeze sim:/ram_128_8/addr 0001001 2100 add wave sim:/ram_128_8/* run run run run run run run run run run run run run run run run run run run run run run run Page 2

- 16. /ram_128_8/din 0 100 101 102 103 104 105 106 107 108 109 /ram_128_8/dout X 100 101 102 103 104 105 106 107 108 109 100 101 102 103 104 105 106 107 108 109 /ram_128_8/addr 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 /ram_128_8/wr /ram_128_8/clk /ram_128_8/mem 0 500 1 us 1500 2 us Entity:ram_128_8 Architecture:rtl Date: Fri Dec 30 12:17:46 HDS 2011 Row: 1 Page: 1

- 17. RAM 16 * 4 64 bit 8 Byte

- 18. C:FPGAdv52LibrariesSsrc@r@a@m_16_4@r@t@l.vhd 12/30/11 12:19:28 -- hds header_start -- -- VHDL Architecture S.RAM_16_4.RTL -- -- Created: -- by - Pharaoh.UNKNOWN (S) -- at - 17:25:54 11/16/2011 -- -- Generated by Mentor Graphics' HDL Designer(TM) 2001.5 (Build 170) -- -- hds header_end LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY RAM_16_4 IS -- Declarations PORT (addr,din: IN STD_Logic_Vector (3 downto 0); dout: OUT STD_Logic_Vector (3 downto 0); wr,clk: IN STD_Logic); END RAM_16_4 ; -- hds interface_end ARCHITECTURE RTL OF RAM_16_4 IS type mem_type is array (0 to 15) of STD_Logic_vector (3 downto 0); signal mem: mem_type; BEGIN Process (clk) begin if(rising_edge(clk)) then if(wr='1') then mem(conv_integer(unsigned(addr))) <= din; end if; end if; End Process; dout <= mem(conv_integer(unsigned(addr))); END RTL; Page: 1

- 19. RAM 16.4 Simulation Code force -freeze sim:/ram_16_4/clk 1 0, 0 {50 ns} -r 100 force -freeze sim:/ram_16_4/wr 1 0 force -freeze sim:/ram_16_4/addr 0000 0 force -freeze sim:/ram_16_4/din 0000 0 force -freeze sim:/ram_16_4/addr 0000 100 force -freeze sim:/ram_16_4/addr 0001 200 force -freeze sim:/ram_16_4/addr 0010 300 force -freeze sim:/ram_16_4/addr 0011 400 force -freeze sim:/ram_16_4/addr 0100 500 force -freeze sim:/ram_16_4/addr 0101 600 force -freeze sim:/ram_16_4/addr 0110 700 force -freeze sim:/ram_16_4/addr 0111 800 force -freeze sim:/ram_16_4/addr 1000 900 force -freeze sim:/ram_16_4/addr 1001 1000 force -freeze sim:/ram_16_4/addr 1010 1100 force -freeze sim:/ram_16_4/addr 1011 1200 force -freeze sim:/ram_16_4/addr 1100 1300 force -freeze sim:/ram_16_4/addr 1101 1400 force -freeze sim:/ram_16_4/addr 1110 1500 force -freeze sim:/ram_16_4/addr 1111 1600 force -freeze sim:/ram_16_4/din 1111 100 force -freeze sim:/ram_16_4/din 1110 200 force -freeze sim:/ram_16_4/din 1101 300 force -freeze sim:/ram_16_4/din 1100 400 force -freeze sim:/ram_16_4/din 1011 500 force -freeze sim:/ram_16_4/din 1010 600 force -freeze sim:/ram_16_4/din 1001 700 force -freeze sim:/ram_16_4/din 1000 800 force -freeze sim:/ram_16_4/din 0111 900 force -freeze sim:/ram_16_4/din 0110 1000 force -freeze sim:/ram_16_4/din 0101 1100 force -freeze sim:/ram_16_4/din 0100 1200 force -freeze sim:/ram_16_4/din 0011 1300 Page 1

- 20. RAM 16.4 Simulation Code force -freeze sim:/ram_16_4/din 0010 1400 force -freeze sim:/ram_16_4/din 0001 1500 force -freeze sim:/ram_16_4/din 0000 1600 force -freeze sim:/ram_16_4/wr 0 1700 force -freeze sim:/ram_16_4/addr 0000 1800 force -freeze sim:/ram_16_4/addr 0001 1900 force -freeze sim:/ram_16_4/addr 0010 2000 force -freeze sim:/ram_16_4/addr 0011 2100 force -freeze sim:/ram_16_4/addr 0100 2200 force -freeze sim:/ram_16_4/addr 0101 2300 force -freeze sim:/ram_16_4/addr 0110 2400 force -freeze sim:/ram_16_4/addr 0111 2500 force -freeze sim:/ram_16_4/addr 1000 2600 force -freeze sim:/ram_16_4/addr 1001 2700 force -freeze sim:/ram_16_4/addr 1010 2800 force -freeze sim:/ram_16_4/addr 1011 2900 force -freeze sim:/ram_16_4/addr 1100 3000 force -freeze sim:/ram_16_4/addr 1101 3100 force -freeze sim:/ram_16_4/addr 1110 3200 force -freeze sim:/ram_16_4/addr 1111 3300 add wave sim:/ram_16_4/* run run run run run run run run run run run Page 2

- 21. RAM 16.4 Simulation Code run run run run run run run run run run run run run run run run run run run run run run run run run Page 3

- 22. /ram_16_4/addr 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 /ram_16_4/din 0 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 /ram_16_4/dout X 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 /ram_16_4/wr /ram_16_4/clk /ram_16_4/mem {1111 1110 1101 1100 1011 1010 1001 1000 0111 0110 0101 0100 0011 0010 0001 0000} 0 500 1 us 1500 2 us 2500 3 us 3500 4 us 4500 Entity:ram_16_4 Architecture:rtl Date: Fri Dec 30 13:27:44 HDS 2011 Row: 1 Page: 1

- 23. ROM 128 * 8 1024 bit 128 Byte

- 24. C:FPGAdv52LibrariesSsrc@r@o@m_128_8@r@t@l.vhd 12/30/11 12:19:53 -- hds header_start -- -- VHDL Architecture S.ROM_128_8.RTL -- -- Created: -- by - Pharaoh.UNKNOWN (S) -- at - 16:39:55 11/16/2011 -- -- Generated by Mentor Graphics' HDL Designer(TM) 2001.5 (Build 170) -- -- hds header_end LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY ROM_128_8 IS -- Declarations PORT (addr: IN STD_Logic_Vector (6 downto 0); dout: OUT STD_Logic_Vector (7 downto 0); clk: IN STD_Logic); END ROM_128_8 ; -- hds interface_end ARCHITECTURE RTL OF ROM_128_8 IS type rom_type is array (0 to 127) of STD_Logic_Vector(7 downto 0); constant rom: rom_type:= ("00000001","00000010","00000011","00000100", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "10101010","10101010","10101010","10101010","10101010","10101010","10101010","10101010", "00000001","00000010","00000011","00000100"); BEGIN Process (clk) Begin if (rising_edge(clk)) then dout <= rom(conv_integer(unsigned(addr))); end if; End Process; END RTL; Page: 1

- 25. ROM 128.8 Simulation Code force -freeze sim:/rom_128_8/clk 1 0, 0 {50 ns} -r 100 force -freeze sim:/rom_128_8/addr 0000000 0 force -freeze sim:/rom_128_8/addr 0000001 200 force -freeze sim:/rom_128_8/addr 0000010 400 force -freeze sim:/rom_128_8/addr 0000011 600 force -freeze sim:/rom_128_8/addr 0000100 800 force -freeze sim:/rom_128_8/addr 1111011 1000 force -freeze sim:/rom_128_8/addr 1111100 1200 force -freeze sim:/rom_128_8/addr 1111101 1400 force -freeze sim:/rom_128_8/addr 1111110 1600 force -freeze sim:/rom_128_8/addr 1111111 1800 add wave sim:/rom_128_8/* run run run run run run run run run run run run run run run run run run run Page 1

- 26. /rom_128_8/addr 0000000 0000001 0000010 0000011 0000100 1111011 1111100 1111101 1111110 1111111 /rom_128_8/dout XXXXXXXX 00000001 00000010 00000011 00000100 10101010 00000001 00000010 00000011 00000100 /rom_128_8/clk 0 500 1 us 1500 2 us Entity:rom_128_8 Architecture:rtl Date: Fri Dec 30 13:34:57 HDS 2011 Row: 1 Page: 1

- 27. ROM 8*2 16 bit 2 Byte

- 28. C:FPGAdv52LibrariesSsrc@r@o@m_8_2rtl.vhd 12/30/11 13:38:58 -- hds header_start -- -- VHDL Architecture s.ROM_8_2.rtl -- -- Created: -- by - Pharaoh.UNKNOWN (S) -- at - 13:38:41 12/30/2011 -- -- Generated by Mentor Graphics' HDL Designer(TM) 2001.5 (Build 170) -- -- hds header_end LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY ROM_8_2 IS -- Declarations PORT (addr: IN STD_Logic_Vector (2 downto 0); dout: OUT STD_Logic_Vector (1 downto 0); clk: IN STD_Logic); END ROM_8_2 ; -- hds interface_end ARCHITECTURE rtl OF ROM_8_2 IS type rom_type is array (0 to 7) of STD_Logic_Vector(1 downto 0); constant rom: rom_type:= ("00","01","10","11","00","01","10","11"); BEGIN Process (clk) Begin if (rising_edge(clk)) then dout <= rom(conv_integer(unsigned(addr))); End if; End Process; END rtl; Page: 1

- 29. ROM 8.2 Simulatin Code force -freeze sim:/rom_8_2/clk 1 0, 0 {50 ns} -r 100 force -freeze sim:/rom_8_2/addr 000 0 force -freeze sim:/rom_8_2/addr 001 200 force -freeze sim:/rom_8_2/addr 010 300 force -freeze sim:/rom_8_2/addr 011 400 force -freeze sim:/rom_8_2/addr 100 500 force -freeze sim:/rom_8_2/addr 101 600 force -freeze sim:/rom_8_2/addr 110 700 force -freeze sim:/rom_8_2/addr 111 800 add wave sim:/rom_8_2/* run run run run run run run run run run run Page 1

- 30. /rom_8_2/addr 000 001 010 011 100 101 110 111 /rom_8_2/dout UU 00 01 10 11 00 01 10 11 /rom_8_2/clk 0 500 1 us 1500 2 us Entity:rom_8_2 Architecture:rtl Date: Fri Dec 30 13:41:54 HDS 2011 Row: 1 Page: 1

- 32. 2 Contents 1. TLC 2. Sequence Detector 3. Vending Machine 4. EDL 5. Smart Door 6. Suez Canal

- 33. TLC

- 34. S_TLCTLCstruct Package List Declarations LIBRARY ieee; Ports: USE ieee.std_logic_1164.all; Start : std_logic USE ieee.std_logic_arith.all; clk : std_logic rst : std_logic Green : std_logic Red : std_logic Yellow : std_logic Diagram Signals: SIGNAL finish_r : std_logic SIGNAL finish_y : std_logic <company name> Project: <enter project name here> Title: <enter diagram title here> <enter comments here> Path: S_TLC/TLC/struct Edited: by Pharaoh on 16 Dec 2011 rst Green rst Green S_TLC clk TLC_FSM clk I2 Yellow Yellow Start Start finish_y Red Red finish_r clk finish_y clk finish_r clk S_TLC q clk S_TLC q Yellow Red en Counter_2bit en Counter_4bit rst rst I0 rst rst I1 Printed by Pharaoh on 12/29/2011 at 05:12:47 PM Page 1 of 1

- 35. S_TLCTLC_FSMfsm ['machine0'] Global Actions Concurrent Statements Architecture Declarations Signals Status State Register Statements Process Declarations SIGNAL SCOPE DEFAULT RESET STATUS Green OUT '0' COMB Package List Red OUT '0' COMB LIBRARY ieee; Yellow OUT '0' COMB USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; <company name> Project: <enter project name here> Title: <enter diagram title here> <enter comments here> Path: S_TLC/TLC_FSM/fsm Edited: by Pharaoh on 16 Dec 2011 Green <= '1'; s0 Yellow <= '0'; Red <= '0'; finish_r = '1' Start = '1' Green <= '0'; Green <= '0'; Yellow <= '0'; finish_y = '1' s1 Yellow <= '1'; s2 Red <= '1'; Red <= '0'; Printed by Pharaoh on 12/29/2011 at 05:13:23 PM Page 1 of 1

- 36. Simulation view signals # .signals force -freeze sim:/tlc/clk 1 0, 0 {50 ns} -r 100 force -freeze sim:/tlc/rst 1 0 force -freeze sim:/tlc/rst 0 200 force -freeze sim:/tlc/start 0 0 force -freeze sim:/tlc/start 1 300 force -freeze sim:/tlc/start 0 400 add wave sim:/tlc/* run run run run run run run run run run run run run run run run run run run run run run run run run run run run run Page 1

- 38. Simulation run run run run run run run Page 3

- 39. /tlc/start /tlc/clk /tlc/rst /tlc/green /tlc/red /tlc/yellow /tlc/finish_r /tlc/finish_y /tlc/yellow_internal /tlc/red_internal 0 1 us 2 us 3 us 4 us 5 us 6 us 7 us 8 us 9 us Entity:tlc Architecture:struct Date: Fri Dec 16 20:17:15 HDS 2011 Row: 1 Page: 1

- 41. C:FPGAdv52LibrariesS_TLCsrc@counter_2bitrtl.vhd 12/16/11 18:20:57 -- hds header_start -- -- VHDL Architecture S_TLC.Counter_2bit.rtl -- -- Created: -- by - Pharaoh.UNKNOWN (S) -- at - 18:12:46 12/16/2011 -- -- Generated by Mentor Graphics' HDL Designer(TM) 2001.5 (Build 170) -- -- hds header_end LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY Counter_2bit IS -- Declarations PORT (rst, en, clk: IN Std_Logic; q : OUT Std_Logic); END Counter_2bit ; -- hds interface_end ARCHITECTURE rtl OF Counter_2bit IS Signal count_sig: unsigned (1 downto 0); BEGIN Process(rst,clk) Begin if (rst ='1') then count_sig <= (Others => '0'); elsif (rising_edge(clk)) then if (en = '1') then count_sig <= count_sig +1; end if; end if; end process; q <= count_sig(0) and count_sig(1); END rtl; Page: 1

- 42. Simulation 2bit view signals # .signals force -freeze sim:/counter_2bit/rst 1 0 force -freeze sim:/counter_2bit/rst 0 200 force -freeze sim:/counter_2bit/en 0 0 force -freeze sim:/counter_2bit/en 1 400 force -freeze sim:/counter_2bit/clk 1 0, 0 {50 ns} -r 100 add wave sim:/counter_2bit/* run run run run run run run run run run run run run run run run run run run run run run Page 1

- 43. /counter_2bit/rst /counter_2bit/en /counter_2bit/clk /counter_2bit/q /counter_2bit/count_sig 00 01 10 11 00 01 10 11 00 01 10 11 00 01 10 11 00 01 10 0 500 1 us 1500 2 us Entity:counter_2bit Architecture:rtl Date: Fri Dec 16 18:25:50 HDS 2011 Row: 1 Page: 1

- 44. C:FPGAdv52LibrariesS_TLCsrc@counter_4bitrtl.vhd 12/16/11 18:28:19 -- hds header_start -- -- VHDL Architecture S_TLC.Counter_4bit.rtl -- -- Created: -- by - Pharaoh.UNKNOWN (S) -- at - 18:27:22 12/16/2011 -- -- Generated by Mentor Graphics' HDL Designer(TM) 2001.5 (Build 170) -- -- hds header_end LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY Counter_4bit IS -- Declarations port(clk,en,rst:IN Std_Logic; q:OUT Std_Logic); END Counter_4bit ; -- hds interface_end ARCHITECTURE rtl OF Counter_4bit IS signal count_sig:unsigned(3 downto 0); BEGIN process(rst,clk) begin if(rst='1') then count_sig<=(others=>'0'); elsif(rising_edge(clk)) then if (en='1') then count_sig<=count_sig+1; end if; end if; end process; q<=count_sig(0) and count_sig(1) and count_sig(2) and count_sig(3); END rtl; Page: 1

- 45. Simulation 4bit view signals # .signals # .signals force -freeze sim:/counter_4bit/rst 1 0 force -freeze sim:/counter_4bit/rst 0 200 force -freeze sim:/counter_4bit/en 0 0 force -freeze sim:/counter_4bit/en 1 400 force -freeze sim:/counter_4bit/clk 1 0, 0 {50 ns} -r 100 add wave sim:/counter_4bit/* run run run run run run run run run run run run run run run run run run run run run run run run run run run Page 1

- 46. /counter_4bit/clk /counter_4bit/en /counter_4bit/rst /counter_4bit/q /counter_4bit/count_sig 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 0000 0001 0010 0011 0100 0101 0 500 1 us 1500 2 us Entity:counter_4bit Architecture:rtl Date: Fri Dec 16 18:30:05 HDS 2011 Row: 1 Page: 1

- 47. Sequence Detector Non-Overlapping

- 48. S_Sequence_DetectorSeq_Det_10010struct Package List Declarations LIBRARY ieee; Ports: USE ieee.std_logic_1164.all; Clk : std_logic USE ieee.std_logic_arith.all; Rst : std_logic din : std_logic Seq_Ok : std_logic Diagram Signals: <company name> Project: <enter project name here> Title: <enter diagram title here> <enter comments here> Path: <<-- more -->> Edited: by Pharaoh on 17 Dec 2011 Clk Clk S_Sequence_Detector Rst Seq_Ok Rst Seq_Det_FSM_10010 Seq_Ok I2 din din Printed by Pharaoh on 12/19/2011 at 12:35:28 PM Page 1 of 1

- 49. S_Sequence_DetectorSeq_Det_FSM_10010fsm ['machine0'] Global Actions Concurrent Statements Architecture Declarations Signals Status State Register Statements Process Declarations SIGNAL SCOPE DEFAULT RESET STATUS Package List Seq_Ok OUT '0' COMB LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; <company name> Project: <enter project name here> Title: <enter diagram title here> <enter comments here> Path: <<-- more -->> Edited: by Pharaoh on 17 Dec 2011 s0 din = '0' din = '1' 1 Seq_Ok <= '1'; s5 s1 2 din = '1' din = '0' din = '0' din = '0' din = '1' 2 din = '1' 1 1 s4 s2 2 1 din = '0' din = '1' 2 s3 Printed by Pharaoh on 12/19/2011 at 12:35:56 PM Page 1 of 1

- 50. /seq_det_fsm_10010/clk /seq_det_fsm_10010/rst /seq_det_fsm_10010/din /seq_det_fsm_10010/seq_ok /seq_det_fsm_10010/current_state s0 s1 s2 s3 s4 s5 s1 s2 s3 s4 s5 s0 s1 s2 s1 /seq_det_fsm_10010/next_state s0 s1 s2 s3 s4 s5 s1 s2 s3 s4 s5 s0 s1 s2 s1 0 500 1 us 1500 2 us Entity:seq_det_fsm_10010 Architecture:fsm Date: Mon Dec 19 12:49:10 HDS 2011 Row: 1 Page: 1

- 51. Sequence Detector Overlapping

- 52. S_Sequence_DetectorSeq_Det_10010_Ostruct Package List Declarations LIBRARY ieee; Ports: USE ieee.std_logic_1164.all; Clk : std_logic USE ieee.std_logic_arith.all; Rst : std_logic din : std_logic Seq_Ok : std_logic Diagram Signals: <company name> Project: <enter project name here> Title: <enter diagram title here> <enter comments here> Path: <<-- more -->> Edited: by Pharaoh on 17 Dec 2011 Clk Clk S_Sequence_Detector Rst Seq_Ok Rst Seq_Det_FSM_10010_O Seq_Ok I3 din din Printed by Pharaoh on 12/19/2011 at 12:36:22 PM Page 1 of 1

- 53. S_Sequence_DetectorSeq_Det_FSM_10010_Ofsm ['machine0'] Global Actions Concurrent Statements Architecture Declarations Signals Status State Register Statements Process Declarations SIGNAL SCOPE DEFAULT RESET STATUS Package List Seq_Ok OUT '0' COMB LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; <company name> Project: <enter project name here> Title: <enter diagram title here> <enter comments here> Path: <<-- more -->> Edited: by Pharaoh on 17 Dec 2011 s0 din = '1' Seq_Ok <= '1'; s5 s1 2 din = '1' din = '1' 1 din = '0' din = '0' din = '0' din = '1' 2 1 1 din = '0' s4 s2 2 1 din = '0' din = '1' 2 s3 Printed by Pharaoh on 12/19/2011 at 12:36:39 PM Page 1 of 1

- 54. /seq_det_fsm_10010_o/clk /seq_det_fsm_10010_o/rst /seq_det_fsm_10010_o/din /seq_det_fsm_10010_o/seq_ok /seq_det_fsm_10010_o/current_state s0 s1 s2 s3 s4 s5 s1 s2 s3 s4 s5 s3 s4 s5 s1 /seq_det_fsm_10010_o/next_state s0 s1 s2 s3 s4 s5 s1 s2 s3 s4 s5 s3 s4 s5 s1 0 500 1 us 1500 2 us Entity:seq_det_fsm_10010_o Architecture:fsm Date: Mon Dec 19 12:40:35 HDS 2011 Row: 1 Page: 1

- 55. Vending Machine

- 56. S_VMVMstruct Package List Declarations LIBRARY ieee; Ports: USE ieee.std_logic_1164.all; Diagram Signals: SIGNAL Clk : std_logic USE ieee.std_logic_arith.all; SIGNAL Dollar : std_logic SIGNAL Quarter_Dollar : std_logic SIGNAL Return_Request : std_logic SIGNAL Rst : std_logic <company name> SIGNAL Project: Soda <enter : std_logic project name here> SIGNAL Soda_Request : std_logic Title: <enter diagram title here> <enter comments here> SIGNAL The_Return : std_logic Path: S_VM/VM/struct Edited: by Pharaoh on 21 Dec 2011 Clk Rst S_VM VM_FSM Dollar I0 Quarter_Dollar The_Return Soda_Request Soda Return_Request Printed by Pharaoh on 12/21/2011 at 11:36:14 AM Page 1 of 1

- 57. S_VMVM_FSMfsm ['machine0'] Global Actions Concurrent Statements Architecture Declarations Signals Status State Register Statements Process Declarations SIGNAL SCOPE DEFAULT RESET STATUS Package List Soda OUT '0' COMB The_Return OUT '0' COMB LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; <company name> Project: <enter project name here> Title: <enter diagram title here> <enter comments here> Path: S_VM/VM_FSM/fsm Edited: by Pharaoh on 21 Dec 2011 Quarter_Dollar = '1' Quarter_Dollar = '1' s3 s1 s2 2 1 Quarter_Dollar = '1' Soda_Request = '1' 1 Quarter_Dollar = '1' s0 s5 Soda <= '1'; 2 Dollar = '1' s4 s8 The_Return <= '1'; Return_Request = '1' Soda_Request = '1' s7 s6 Soda <= '0'; Soda <= '1'; Printed by Pharaoh on 12/21/2011 at 11:41:17 AM Page 1 of 1

- 58. VM Simulation Code - 3 Quarters force -freeze sim:/vm_fsm/clk 1 0, 0 {50 ns} -r 100 force -freeze sim:/vm_fsm/rst 1 0 force -freeze sim:/vm_fsm/rst 0 50 force -freeze sim:/vm_fsm/dollar 0 0 force -freeze sim:/vm_fsm/quarter_dollar 0 0 force -freeze sim:/vm_fsm/soda_request 0 0 force -freeze sim:/vm_fsm/return_request 0 0 force -freeze sim:/vm_fsm/quarter_dollar 1 200 force -freeze sim:/vm_fsm/quarter_dollar 0 500 force -freeze sim:/vm_fsm/soda_request 1 1200 add wave sim:/vm_fsm/* run run run run run run run run run run run run run run run run run run run run run Page 1

- 59. /vm_fsm/clk /vm_fsm/rst /vm_fsm/dollar /vm_fsm/quarter_dollar /vm_fsm/return_request /vm_fsm/soda_request /vm_fsm/soda /vm_fsm/the_return /vm_fsm/current_state s0 s1 s2 s3 s5 s0 /vm_fsm/next_state s0 s1 s2 s3 s3 s5 s0 0 500 1 us 1500 2 us Entity:vm_fsm Architecture:fsm Date: Wed Dec 21 12:09:48 HDS 2011 Row: 1 Page: 1

- 61. VM Simulation Code - 4 Quarters force -freeze sim:/vm_fsm/clk 1 0, 0 {50 ns} -r 100 force -freeze sim:/vm_fsm/rst 1 0 force -freeze sim:/vm_fsm/rst 0 50 force -freeze sim:/vm_fsm/dollar 0 0 force -freeze sim:/vm_fsm/quarter_dollar 0 0 force -freeze sim:/vm_fsm/soda_request 0 0 force -freeze sim:/vm_fsm/return_request 0 0 force -freeze sim:/vm_fsm/quarter_dollar 1 200 force -freeze sim:/vm_fsm/quarter_dollar 0 600 force -freeze sim:/vm_fsm/soda_request 1 1200 force -freeze sim:/vm_fsm/return_request 1 2000 add wave sim:/vm_fsm/* run run run run run run run run run run run run run run run run run run run run run Page 1

- 62. /vm_fsm/clk /vm_fsm/rst /vm_fsm/dollar /vm_fsm/quarter_dollar /vm_fsm/return_request /vm_fsm/soda_request /vm_fsm/soda /vm_fsm/the_return /vm_fsm/current_state s0 s1 s2 s3 s4 s6 s7 s8 s0 /vm_fsm/next_state s0 s1 s2 s3 s4 s4 s6 s7 s8 s0 0 500 1 us 1500 2 us Entity:vm_fsm Architecture:fsm Date: Wed Dec 21 11:52:56 HDS 2011 Row: 1 Page: 1

- 64. VM Simulation Code - Dollar force -freeze sim:/vm_fsm/clk 1 0, 0 {50 ns} -r 100 force -freeze sim:/vm_fsm/rst 1 0 force -freeze sim:/vm_fsm/rst 0 50 force -freeze sim:/vm_fsm/dollar 0 0 force -freeze sim:/vm_fsm/quarter_dollar 0 0 force -freeze sim:/vm_fsm/soda_request 0 0 force -freeze sim:/vm_fsm/return_request 0 0 force -freeze sim:/vm_fsm/dollar 1 200 force -freeze sim:/vm_fsm/dollar 0 300 force -freeze sim:/vm_fsm/soda_request 1 800 force -freeze sim:/vm_fsm/return_request 1 1600 add wave sim:/vm_fsm/* run run run run run run run run run run run run run run run run run run run run run Page 1

- 65. /vm_fsm/clk /vm_fsm/rst /vm_fsm/dollar /vm_fsm/quarter_dollar /vm_fsm/return_request /vm_fsm/soda_request /vm_fsm/soda /vm_fsm/the_return /vm_fsm/current_state s0 s4 s6 s7 s8 s0 /vm_fsm/next_state s0 s4 s4 s6 s7 s8 s0 0 500 1 us 1500 2 us Entity:vm_fsm Architecture:fsm Date: Wed Dec 21 12:03:18 HDS 2011 Row: 1 Page: 1

- 67. Electronic Door Lock No Interrupt

- 68. ExpTLCstruct Package List Declarations LIBRARY ieee; Ports: USE ieee.std_logic_1164.all; Diagram Signals: USE ieee.std_logic_arith.all; SIGNAL Clk : std_logic SIGNAL Green : std_logic SIGNAL Red : std_logic SIGNAL Rst : std_logic SIGNAL Start : std_logic <company name> Project: SIGNAL Yellow :<enter project name here> std_logic SIGNAL finish_r : Std_Logic Title: <enter diagram title here> <enter comments here> SIGNAL finish_y : Std_Logic Path: Exp/TLC/struct Edited: by Pharaoh on 24 Dec 2011 Clk Green Rst Exp Yellow TLC_FSM I2 Start Red finish_y finish_r Clk finish_y Clk finish_r clk S_TLC q clk S_TLC q Yellow Red en Counter_2bit en Counter_4bit Rst rst I0 Rst rst I1 Printed by Pharaoh on 12/29/2011 at 05:33:30 PM Page 1 of 1

- 69. ExpEDL_FSMfsm ['machine0'] Global Actions Concurrent Statements Architecture Declarations Signals Status State Register Statements Process Declarations SIGNAL SCOPE DEFAULT RESET STATUS Package List Click OUT '0' COMB Open_Door OUT '0' COMB LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; <company name> Project: <enter project name here> Title: <enter diagram title here> <enter comments here> Path: Exp/EDL_FSM/fsm Edited: by Pharaoh on 29 Dec 2011 s0 2 1 Key = "0011" s1 s5 Click <= '1'; 2 Click <= '1'; 1 Key = "1010" s6 s2 Click <= '1'; Click <= '1'; 2 1 Key = "0101" s7 s3 Click <= '1'; Click <= '1'; Key = "1011" s4 Open_Door <= '1'; Click <= '1'; Printed by Pharaoh on 12/29/2011 at 05:35:08 PM Page 1 of 1

- 70. /edl_fsm/clk /edl_fsm/key 0011 1010 0101 1011 /edl_fsm/rst /edl_fsm/click /edl_fsm/open_door /edl_fsm/current_state s0 s1 s2 s3 s4 s0 s5 s6 s7 s0 s5 s6 s7 s0 s5 s6 s7 s0 /edl_fsm/next_state s1 s2 s3 s4 s0 s5 s6 s7 s0 s5 s6 s7 s0 s5 s6 s7 s0 s5 0 500 1 us 1500 2 us Entity:edl_fsm Architecture:fsm Date: Thu Dec 29 17:30:47 HDS 2011 Row: 1 Page: 1

- 71. Simulation Code force -freeze sim:/edl_fsm/clk 1 0, 0 {50 ns} -r 100 force -freeze sim:/edl_fsm/rst 1 0 force -freeze sim:/edl_fsm/rst 0 50 force -freeze sim:/edl_fsm/key 0011 0 force -freeze sim:/edl_fsm/key 1010 100 force -freeze sim:/edl_fsm/key 0101 200 force -freeze sim:/edl_fsm/key 1011 300 add wave sim:/edl_fsm/* run run run run run run run run run run run run run run run run run run Page 1

- 72. Electronic Door Lock With Interrupt

- 73. S_EDLEDLstruct Package List Declarations LIBRARY ieee; Ports: USE ieee.std_logic_1164.all; Clk : std_logic Key : std_logic_vector(3 DOWNTO 0) USE ieee.std_logic_arith.all; Rst : std_logic intr : std_logic door_open : std_logic rdy_bsy : std_logic <company name> Project: Diagram Signals: <enter project name here> Title: <enter diagram title here> <enter comments here> Path: S_EDL/EDL/struct Edited: by Pharaoh on 24 Dec 2011 intr intr Key(3:0) Key : (3:0) S_EDL door_open door_open EDL_FSM Clk Clk I0 rdy_bsy rdy_bsy Rst Rst Printed by Pharaoh on 12/29/2011 at 05:03:50 PM Page 1 of 1

- 74. S_EDLEDL_FSMfsm ['machine0'] Global Actions Concurrent Statements Architecture Declarations Signals Status State Register Statements Process Declarations SIGNAL SCOPE DEFAULT RESET STATUS Package List door_open OUT '0' COMB rdy_bsy OUT '0' COMB LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; <company name> Project: <enter project name here> Title: <enter diagram title here> <enter comments here> Path: S_EDL/EDL_FSM/fsm Edited: by Pharaoh on 24 Dec 2011 s0 door_open <= '0'; rdy_bsy <= '0'; 2 intr = '1' 1 intr = '1' intr = '1' AND Key = "1101" s5 door_open <= '0'; rdy_bsy <= '1'; s1 intr = '1' door_open <= '0'; rdy_bsy <= '1'; 2 intr = '1' intr = '1' 1 intr = '1' AND Key = "0011" s6 door_open <= '0'; rdy_bsy <= '1'; s2 door_open <= '0'; intr = '1' rdy_bsy <= '1'; 2 1 intr = '1' intr = '1' AND Key = "0111" s7 door_open <= '0'; rdy_bsy <= '1'; 2 s3 door_open <= '0'; rdy_bsy <= '1'; 1 intr = '1' AND Key = "1001" s4 door_open <= '1'; rdy_bsy <= '1'; Printed by Pharaoh on 12/29/2011 at 05:04:16 PM Page 1 of 1

- 75. /edl_fsm/clk /edl_fsm/rst /edl_fsm/key 0000 1101 0011 0111 1001 /edl_fsm/intr /edl_fsm/door_open /edl_fsm/rdy_bsy /edl_fsm/current_state s0 s1 s2 s3 s4 s0 /edl_fsm/next_state s0 s1 s1 s2 s2 s3 s3 s4 s0 0 500 1 us 1500 2 us Entity:edl_fsm Architecture:fsm Date: Thu Dec 29 17:42:03 HDS 2011 Row: 1 Page: 1

- 76. Simulation Code force -freeze sim:/edl_fsm/clk 1 0, 0 {50 ns} -r 100 force -freeze sim:/edl_fsm/rst 1 0 force -freeze sim:/edl_fsm/rst 0 50 force -freeze sim:/edl_fsm/key 0000 0 force -freeze sim:/edl_fsm/intr 0 0 force -freeze sim:/edl_fsm/intr 1 200 force -freeze sim:/edl_fsm/intr 1 500 force -freeze sim:/edl_fsm/intr 1 800 force -freeze sim:/edl_fsm/intr 1 1100 force -freeze sim:/edl_fsm/intr 0 300 force -freeze sim:/edl_fsm/intr 0 600 force -freeze sim:/edl_fsm/intr 0 900 force -freeze sim:/edl_fsm/intr 0 1200 force -freeze sim:/edl_fsm/key 1101 200 force -freeze sim:/edl_fsm/key 0011 500 force -freeze sim:/edl_fsm/key 0111 800 force -freeze sim:/edl_fsm/key 1001 1100 add wave sim:/edl_fsm/* run run run run run run run run run run run run run run run run run run run run Page 1

- 77. Simulation Code run run run run Page 2

- 78. Smart Door

- 79. S_SDSDstruct Package List Declarations LIBRARY ieee; Ports: USE ieee.std_logic_1164.all; Diagram Signals: USE ieee.std_logic_arith.all; SIGNAL Clk : std_logic SIGNAL Open_Door : std_logic SIGNAL Rst : std_logic SIGNAL Sensor_1 : std_logic SIGNAL Sensor_2 : std_logic <company name> SIGNAL Project: close <enter project name here> : std_logic SIGNAL <enter comments here> en : std_logic Title: <enter diagram title here> Path: S_SD/SD/struct Edited: by Pharaoh on 21 Dec 2011 Clk Rst Open_Door Sensor_1 Sensor_2 S_SD SD_FSM I0 en Clk close clk S_SD close Rst rst Counter_20sec en I1 Printed by Pharaoh on 12/21/2011 at 02:59:21 PM Page 1 of 1

- 80. S_SDSD_FSMfsm ['machine0'] Architecture Declarations Global Actions Concurrent Statements Process Declarations Package List Signals Status State Register Statements LIBRARY ieee; SIGNAL SCOPE DEFAULT RESET STATUS USE ieee.std_logic_1164.all; Open_Door OUT '0' COMB USE ieee.std_logic_arith.all; en OUT '0' COMB <company name> Project: <enter project name here> Title: Smart Door <enter comments here> Path: S_SD/SD_FSM/fsm Edited: by Pharaoh on 21 Dec 2011 s0 Sensor_1 = '1' OR Sensor_2 = '1' 2 s1 close = '1' s2 Open_Door <= '1'; en <= '0'; en <= '1'; Sensor_1 = '1' OR Sensor_2 = '1' 1 Printed by Pharaoh on 12/21/2011 at 03:05:29 PM Page 1 of 1

- 81. Smart Door - Simulation Code add wave sim:/sd/* force -freeze sim:/sd/clk 1 0, 0 {50 ns} -r 100 force -freeze sim:/sd/rst 1 0 force -freeze sim:/sd/rst 0 50 force -freeze sim:/sd/sensor_2 0 0 force -freeze sim:/sd/sensor_1 0 0 force -freeze sim:/sd/sensor_1 1 900 force -freeze sim:/sd/sensor_1 0 1000 force -freeze sim:/sd/sensor_2 1 3900 force -freeze sim:/sd/sensor_2 0 4000 force -freeze sim:/sd/sensor_2 1 6900 force -freeze sim:/sd/sensor_2 0 7000 run run run run run run run run run run run run run run run run run run run run run run run run run Page 1

- 82. Smart Door - Simulation Code run run run run run run run run run run run run run run run run run run run run run run run run run run run run run run run run run run run run run run Page 2

- 83. Smart Door - Simulation Code run run run run run run run run run run run run run run run run run run run run Page 3

- 86. C:FPGAdv52LibrariesS_SDsrc@counter_20secrtl.vhd 12/21/11 14:58:23 -- hds header_start -- -- VHDL Architecture S_SD.Counter_20sec.rtl -- -- Created: -- by - Pharaoh.UNKNOWN (S) -- at - 12:40:51 12/21/2011 -- -- Generated by Mentor Graphics' HDL Designer(TM) 2001.5 (Build 170) -- -- hds header_end LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY Counter_20sec IS -- Declarations port(rst,clk,en: in std_logic; close: out std_logic); END Counter_20sec ; -- hds interface_end ARCHITECTURE rtl OF Counter_20sec IS signal count: unsigned(4 downto 0); BEGIN process(rst,clk) begin if(rst = '1')then count <= "00010"; close <= '0'; elsif (rising_edge(clk)) then if(en = '1') then if( count < 20 ) then count <= count + 1; close <= '0'; else count <= "00001"; close <= '1'; end if; end if; end if; end process; END rtl; Page: 1

- 87. Suez Canal

- 88. BasmaSuezstruct Package List Declarations LIBRARY ieee; Ports: USE ieee.std_logic_1164.all; Diagram Signals: SIGNAL Clk : Std_Logic USE ieee.std_logic_arith.all; SIGNAL Rst : Std_Logic SIGNAL Start_4 : Std_Logic SIGNAL Start_8 : Std_Logic SIGNAL alarm : Std_Logic SIGNAL finish_4 : Std_Logic SIGNAL finish_8 : Std_Logic SIGNAL gate_closed : Std_Logic SIGNAL green : Std_Logic SIGNAL red : Std_Logic SIGNAL sensor_A : std_logic SIGNAL sensor_B : std_logic SIGNAL sensor_C : std_logic SIGNAL yellow : Std_Logic <company name> Project: <enter project name here> Title: <enter diagram title here> <enter comments here> Path: Basma/Suez/struct Edited: by Pharaoh on 29 Dec 2011 Rst Clk sensor_A alarm gate_closed sensor_B sensor_C green yellow red Basma suez_fsm I0 finish_4 Start_4 finish_8 Start_8 Clk Clk finish_8 clk finish_4 clk Basma q Start_4 q Start_8 en Basma en counter_3bits Rst rst counter_2bits Rst rst I2 I1 Printed by Pharaoh on 12/29/2011 at 04:42:42 PM Page 1 of 1

- 89. Basmasuez_fsmfsm ['machine0'] Global Actions Concurrent Statements Architecture Declarations Signals Status State Register Statements Process Declarations SIGNAL SCOPE DEFAULT RESET STATUS Package List Start_4 OUT '0' COMB Start_8 OUT '0' COMB LIBRARY ieee; alarm OUT '0' COMB USE ieee.std_logic_1164.all; gate_closed OUT '0' COMB USE ieee.std_logic_arith.all; green OUT '0' COMB red OUT '0' COMB yellow OUT '0' <company name> COMB Project: <enter project name here> Title: <enter diagram title here> <enter comments here> Path: Basma/suez_fsm/fsm Edited: by Pharaoh on 29 Dec 2011 sensor_A = '0' AND sensor_B = '0' AND sensor_C = '0' green <= '0'; yellow <= '1'; s5 s0 sensor_A = '1' s1 green <= '1'; red <= '0'; green <= '0'; yellow <= '0'; Start_4 <= '1'; yellow <= '0'; red <= '1'; red <= '0'; sensor_C = '1' finish_4 = '1' green <= '0'; alarm <= '1'; yellow <= '0'; gate_closed <= '1'; s4 sensor_B = '1' s3 finish_8 = '1' s2 red <= '1'; green <= '0'; Start_8 <= '1'; yellow <= '0'; red <= '1'; gate_closed <= '1'; green <= '0'; yellow <= '0'; red <= '1'; Printed by Pharaoh on 12/29/2011 at 04:43:10 PM Page 1 of 1

- 90. Simulation Forces force -freeze sim:/suez/clk 1 0, 0 {50 ns} -r 100 force -freeze sim:/suez/rst 1 0 force -freeze sim:/suez/rst 0 50 force -freeze sim:/suez/sensor_a 0 0 force -freeze sim:/suez/sensor_b 0 0 force -freeze sim:/suez/sensor_c 0 0 force -freeze sim:/suez/sensor_a 1 200 force -freeze sim:/suez/sensor_a 0 300 force -freeze sim:/suez/sensor_b 1 1600 force -freeze sim:/suez/sensor_b 0 1700 force -freeze sim:/suez/sensor_c 1 4000 force -freeze sim:/suez/sensor_c 0 4100 add wave sim:/suez/* run run run run run run run run run run run run run run run run run run run run run run run run run Page 1

- 92. /suez/clk /suez/rst /suez/green /suez/yellow /suez/red /suez/sensor_a /suez/sensor_b /suez/sensor_c /suez/start_4 /suez/finish_4 /suez/start_8 /suez/finish_8 /suez/gate_closed /suez/alarm 0 500 1 us 1500 2 us 2500 3 us 3500 4 us 4500 Entity:suez Architecture:struct Date: Thu Dec 29 16:44:34 HDS 2011 Row: 1 Page: 1

- 94. C:FPGAdv52LibrariesBasmasrccounter_2bitsuntitled.vhd 12/29/11 14:06:48 -- hds header_start -- -- VHDL Architecture Basma.counter_2bits.untitled -- -- Created: -- by - Pharaoh.UNKNOWN (S) -- at - 13:55:37 12/29/2011 -- -- Generated by Mentor Graphics' HDL Designer(TM) 2001.5 (Build 170) -- -- hds header_end LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY counter_2bits IS -- Declarations PORT (rst, en, clk: IN Std_Logic; q : OUT Std_Logic); END counter_2bits ; -- hds interface_end ARCHITECTURE untitled OF counter_2bits IS Signal count_sig: unsigned (1 downto 0); BEGIN Process(rst,clk) Begin if (rst ='1') then count_sig <= (Others => '0'); elsif (rising_edge(clk)) then if (en = '1') then count_sig <= count_sig +1; end if; end if; end process; q <= count_sig(0) and count_sig(1); END untitled; Page: 1

- 95. C:FPGAdv52LibrariesBasmasrccounter_3bitsuntitled.vhd 12/29/11 14:08:12 -- hds header_start -- -- VHDL Architecture Basma.counter_3bits.untitled -- -- Created: -- by - Pharaoh.UNKNOWN (S) -- at - 14:06:22 12/29/2011 -- -- Generated by Mentor Graphics' HDL Designer(TM) 2001.5 (Build 170) -- -- hds header_end LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; ENTITY counter_3bits IS -- Declarations PORT (rst, en, clk: IN Std_Logic; q : OUT Std_Logic); END counter_3bits ; -- hds interface_end ARCHITECTURE untitled OF counter_3bits IS Signal count_sig: unsigned (2 downto 0); BEGIN Process(rst,clk) Begin if (rst ='1') then count_sig <= (Others => '0'); elsif (rising_edge(clk)) then if (en = '1') then count_sig <= count_sig +1; end if; end if; end process; q <= count_sig(0) and count_sig(1) and count_sig(2); END untitled; Page: 1