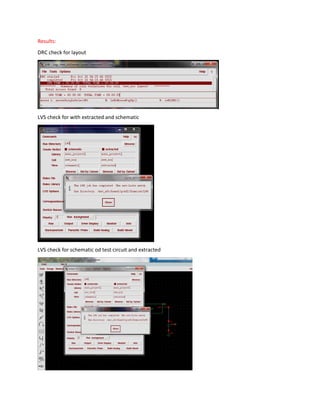

The document describes the design and simulation of a 2-input NOR gate in 0.25um CMOS technology. The goal is to minimize propagation delay and area. Various transistor widths and lengths are analyzed to determine the optimal sizing. Shared diffusion is used to reduce parasitic capacitance and area. The final design has a propagation delay of 0.65ns and passes DRC and LVS checks.