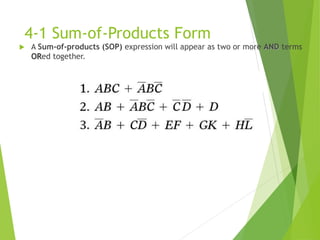

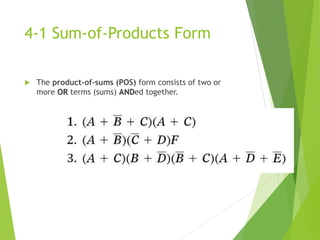

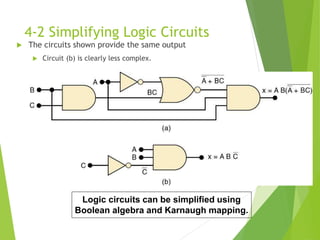

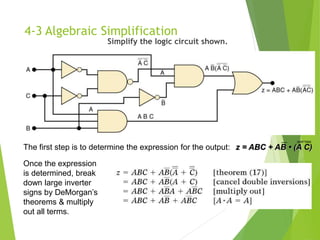

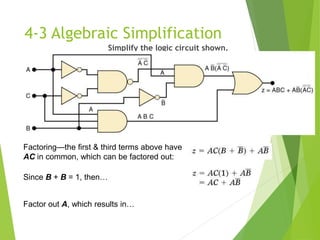

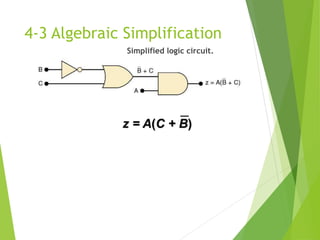

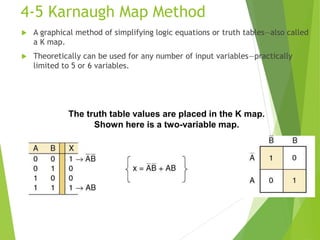

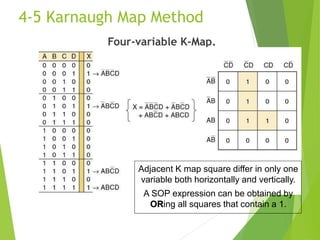

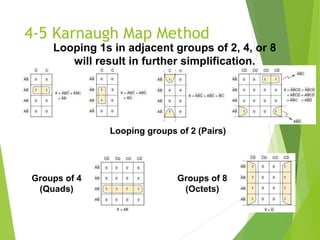

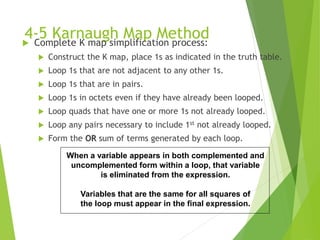

The document discusses digital logic design, focusing on simplifying logic circuits using sum-of-products (SOP) and product-of-sums (POS) forms. It explains algebraic simplification techniques and introduces the Karnaugh map method for visualizing and simplifying logic equations. The simplification process involves grouping terms, applying DeMorgan’s theorems, and eliminating redundant variables to achieve a more efficient circuit design.