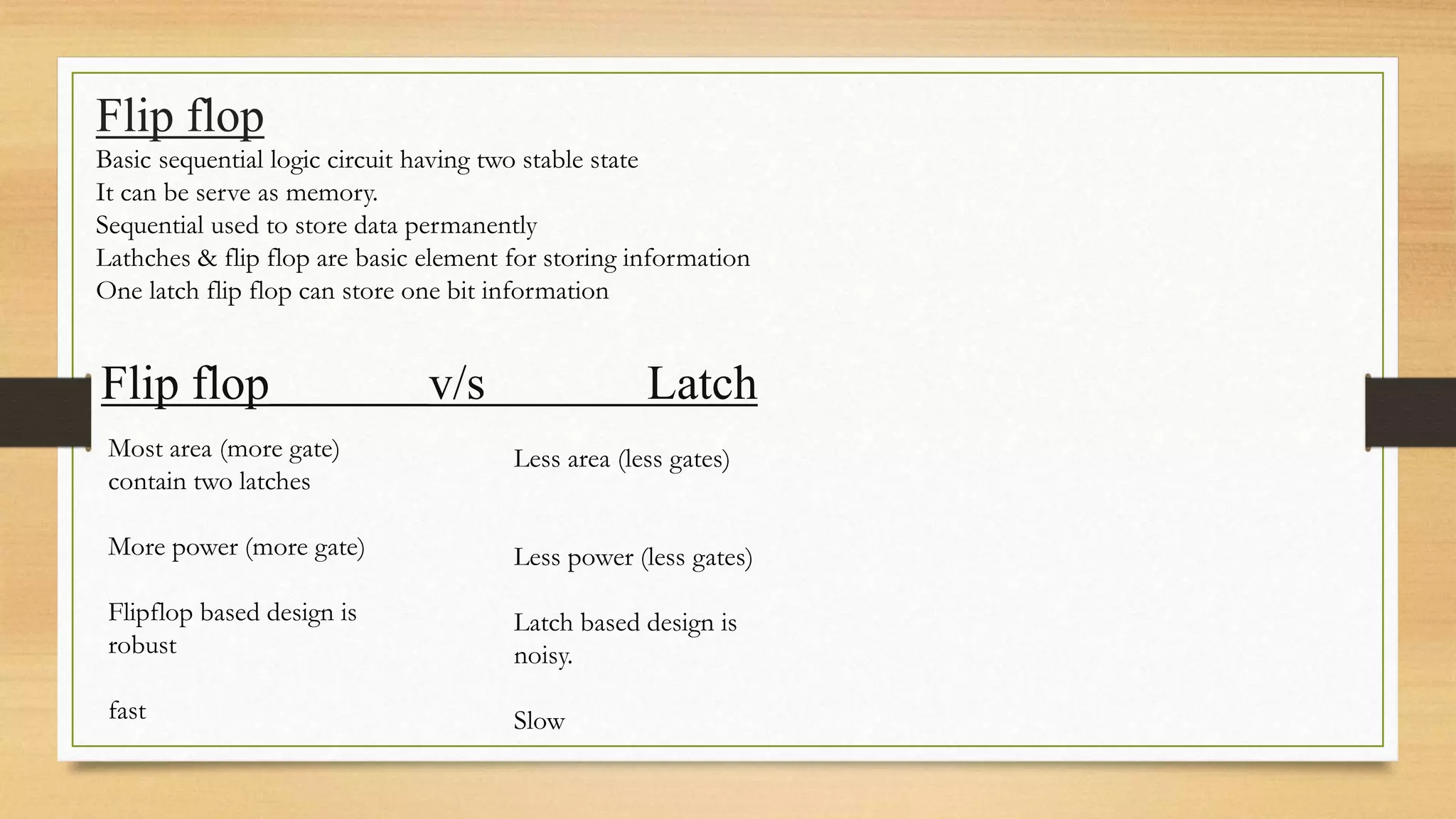

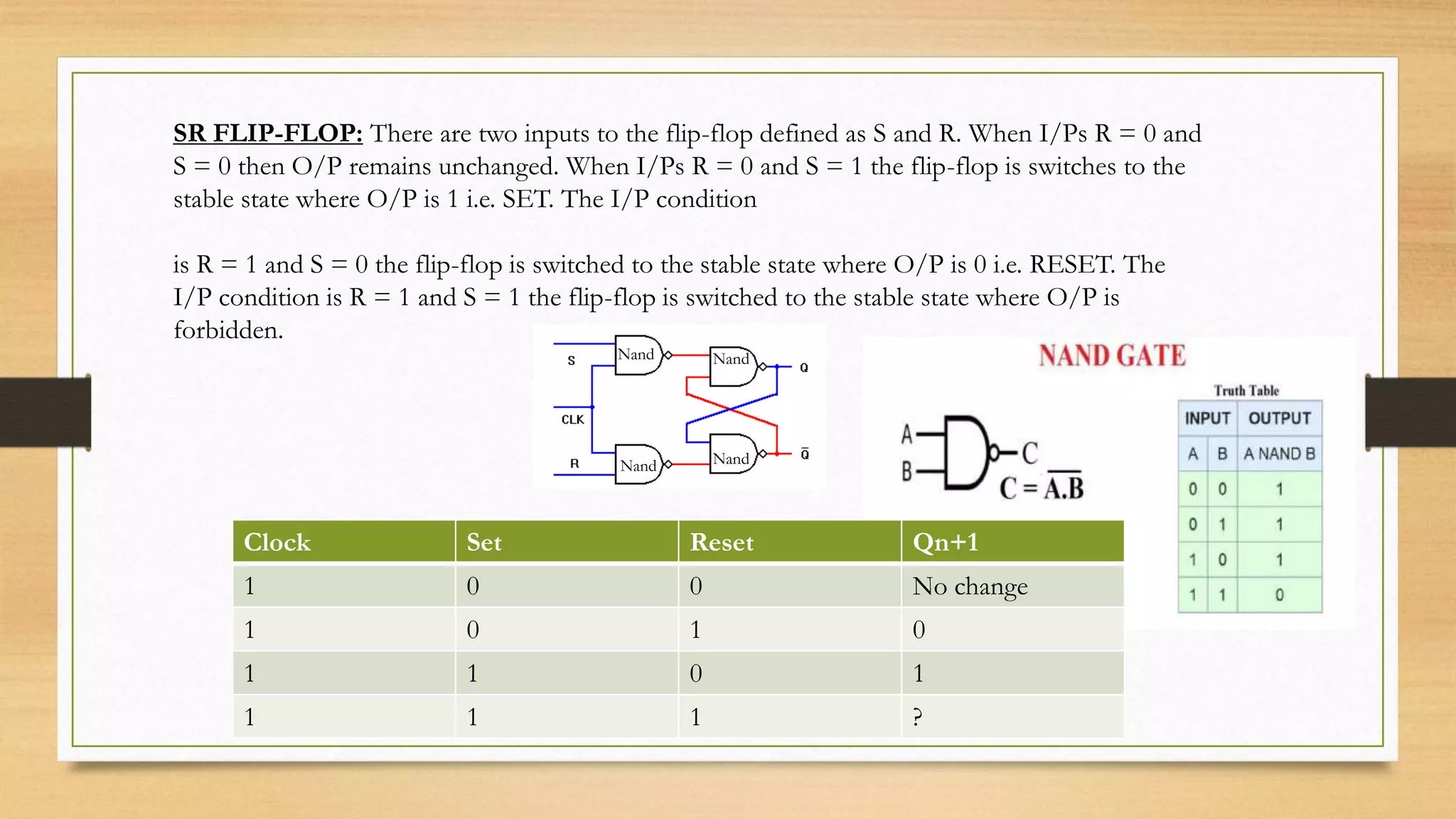

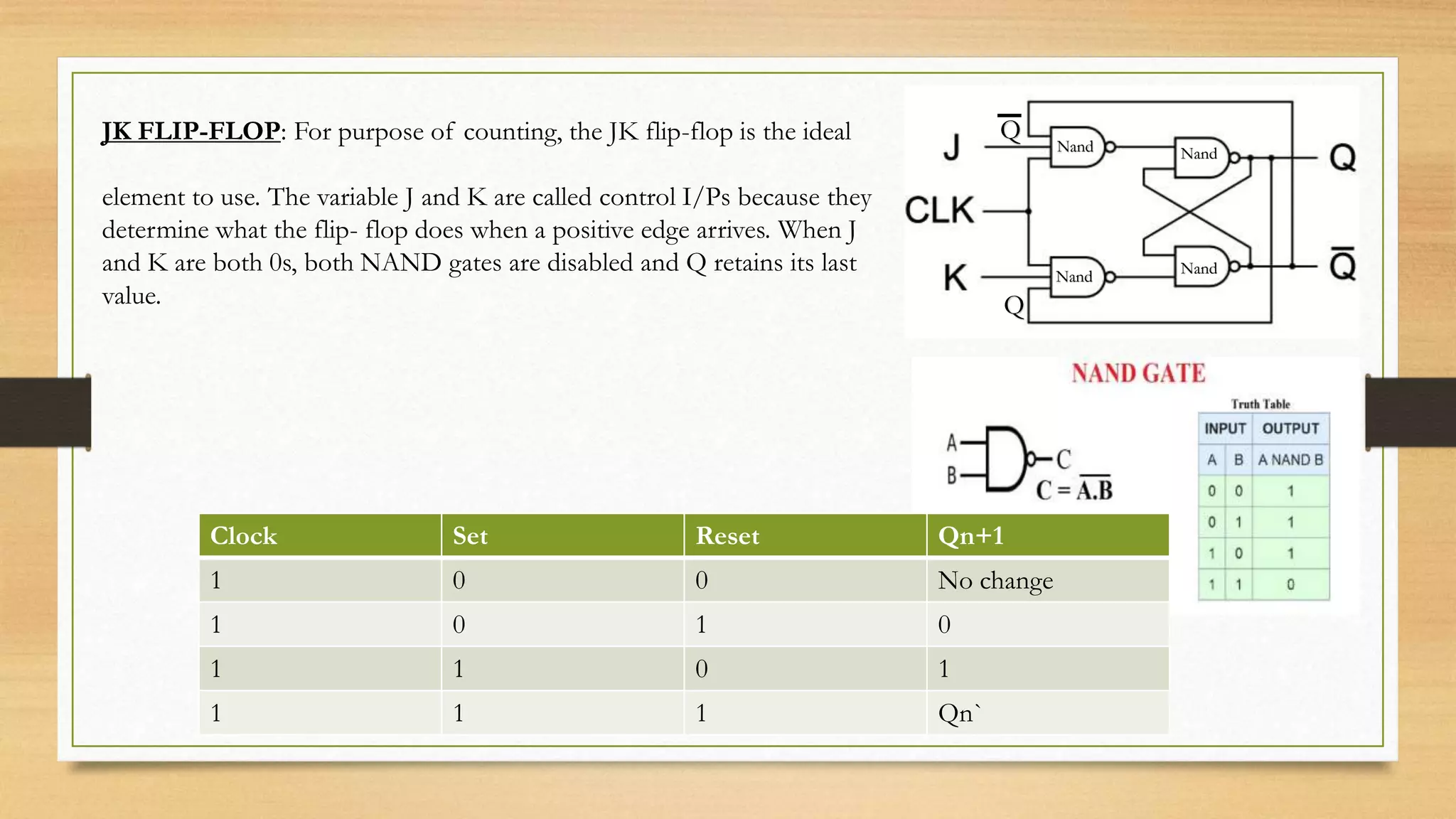

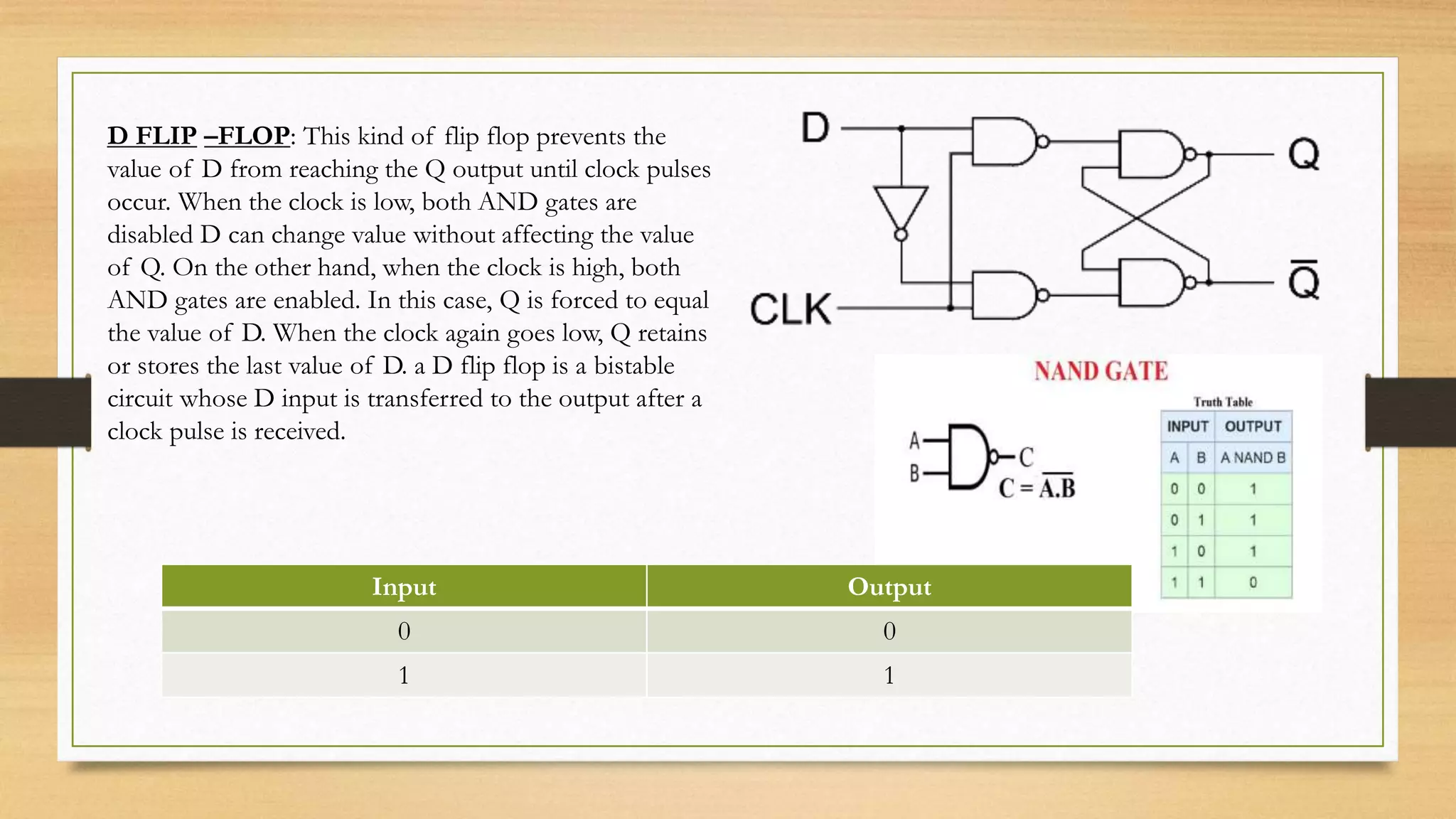

This document discusses different types of flip-flops including SR, JK, D, and T flip-flops. It provides the logic gates used to implement each type of flip-flop and describes their input and output behavior. For example, it states that an SR flip-flop has two inputs, S and R, and it will set the output to 1 if S is 1 and R is 0, or reset the output to 0 if R is 1 and S is 0. The document also compares latches and flip-flops, noting that flip-flops are more robust, faster, and use less area than latches but require more power.