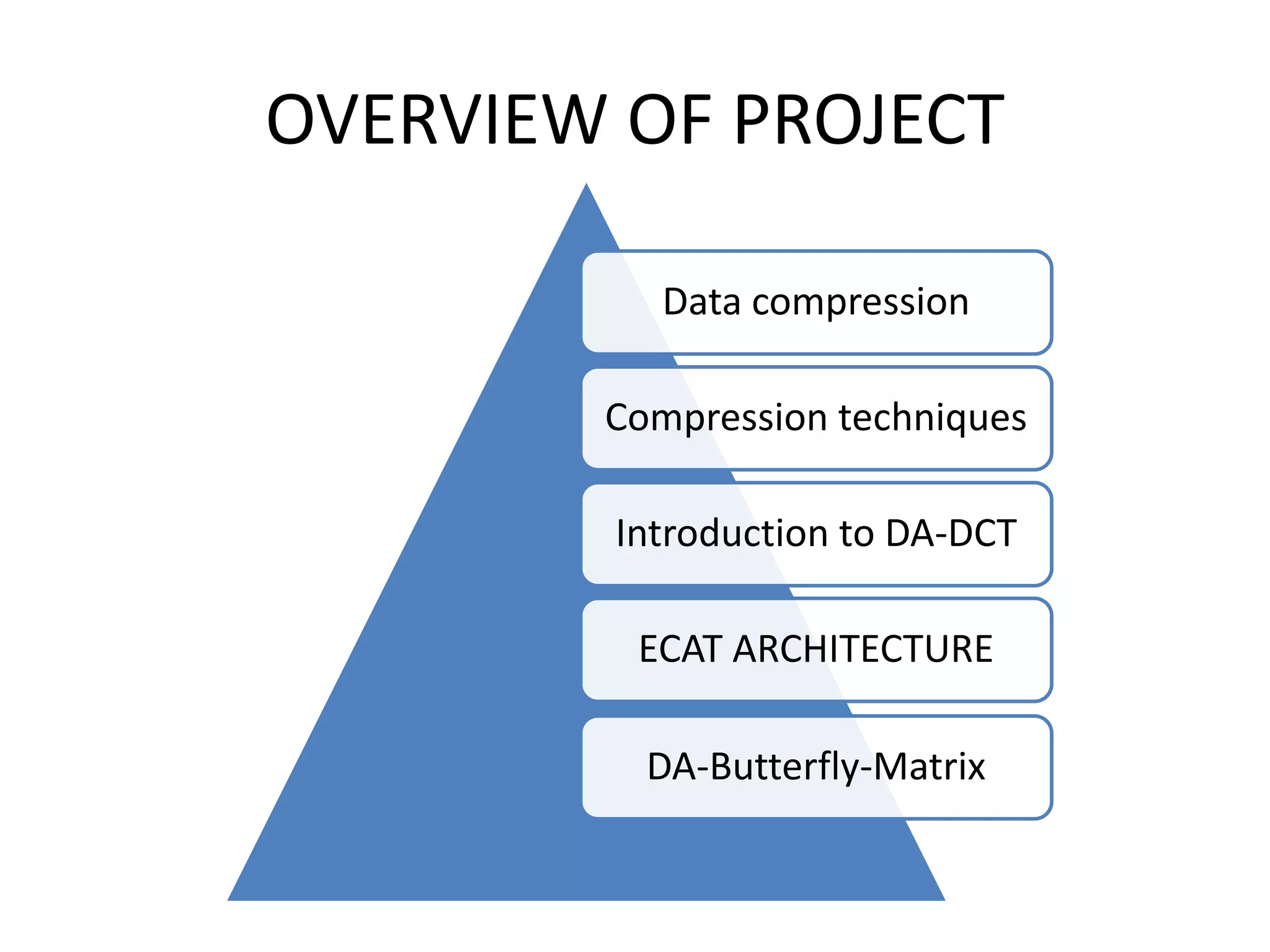

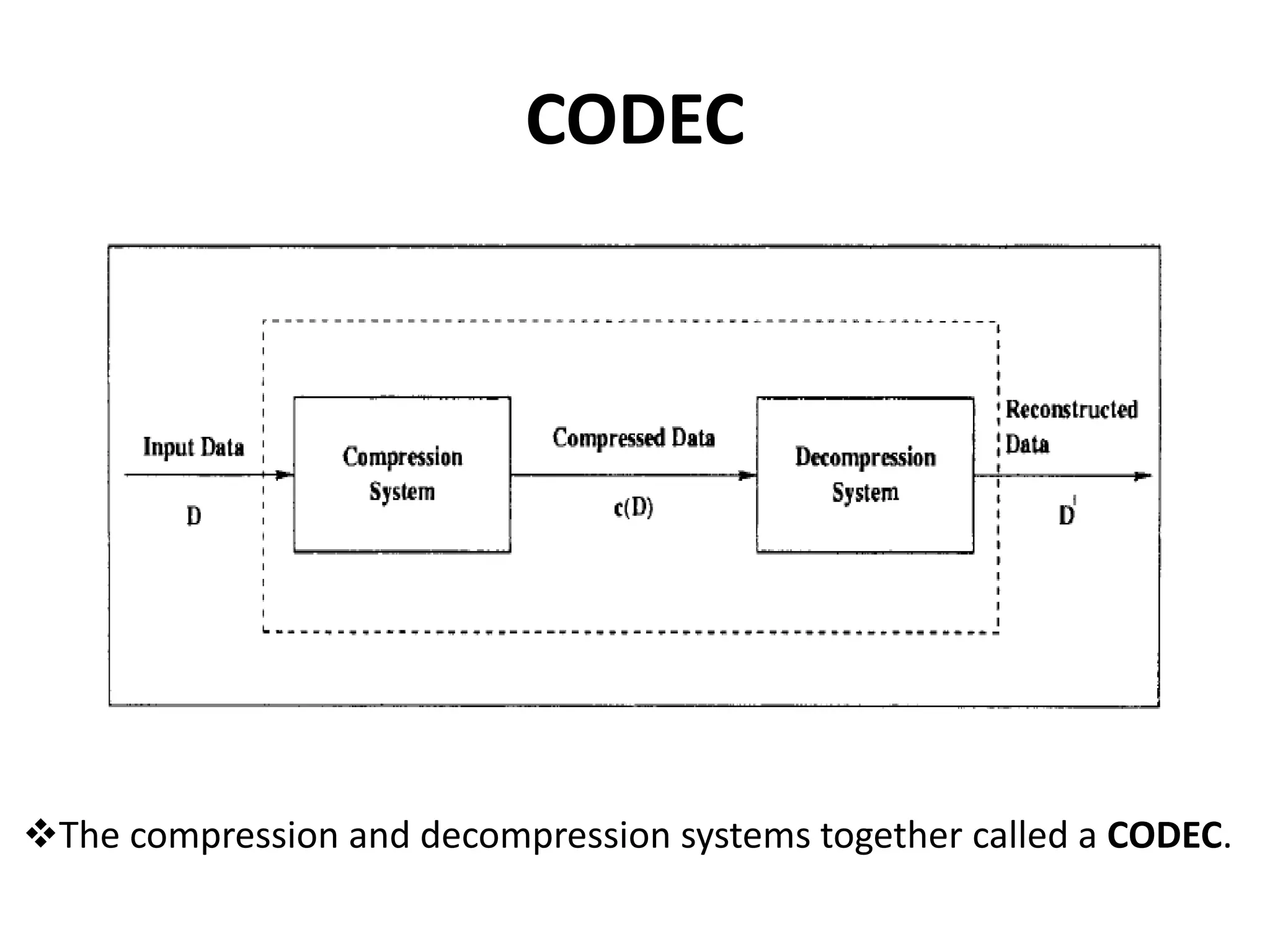

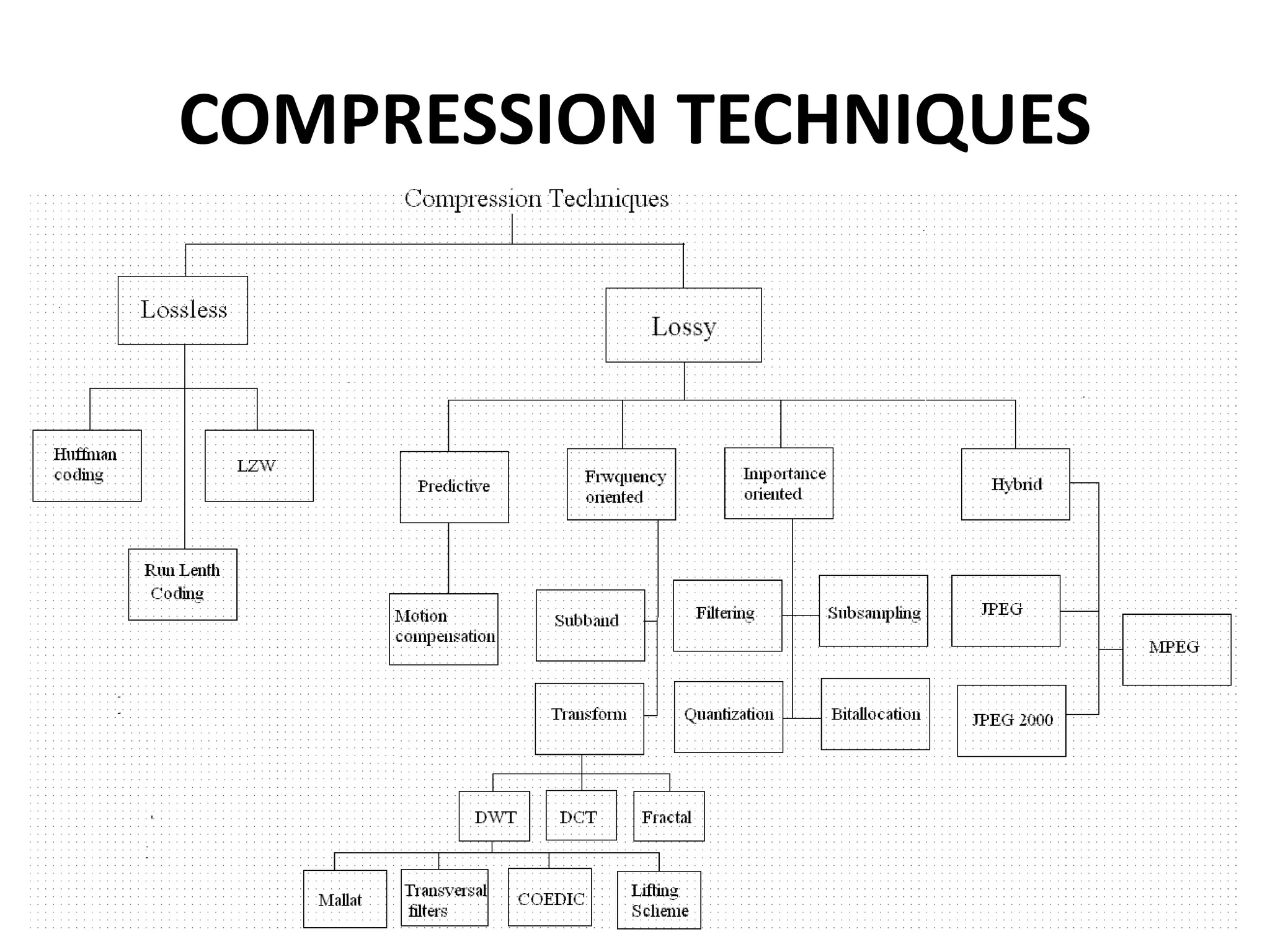

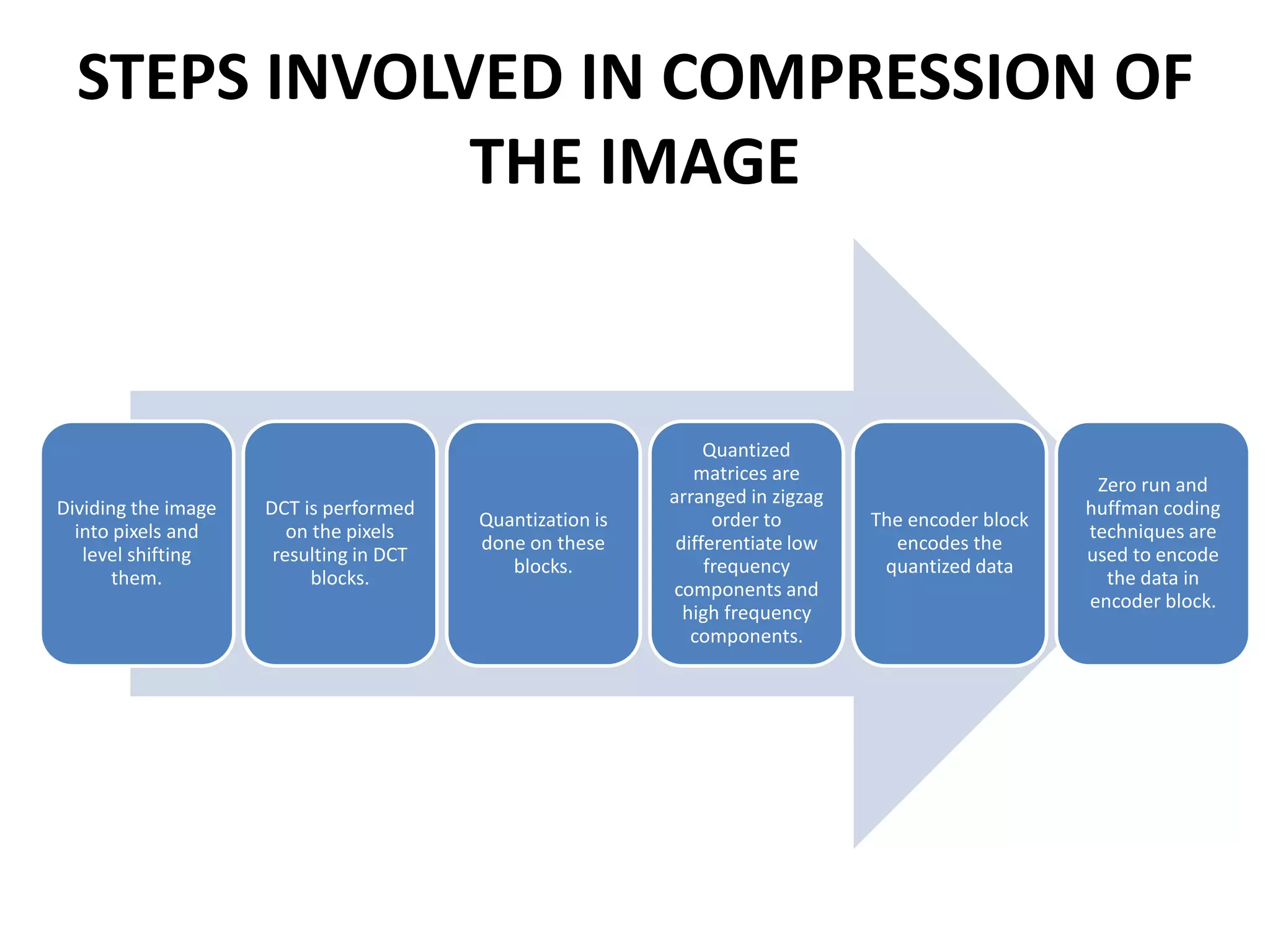

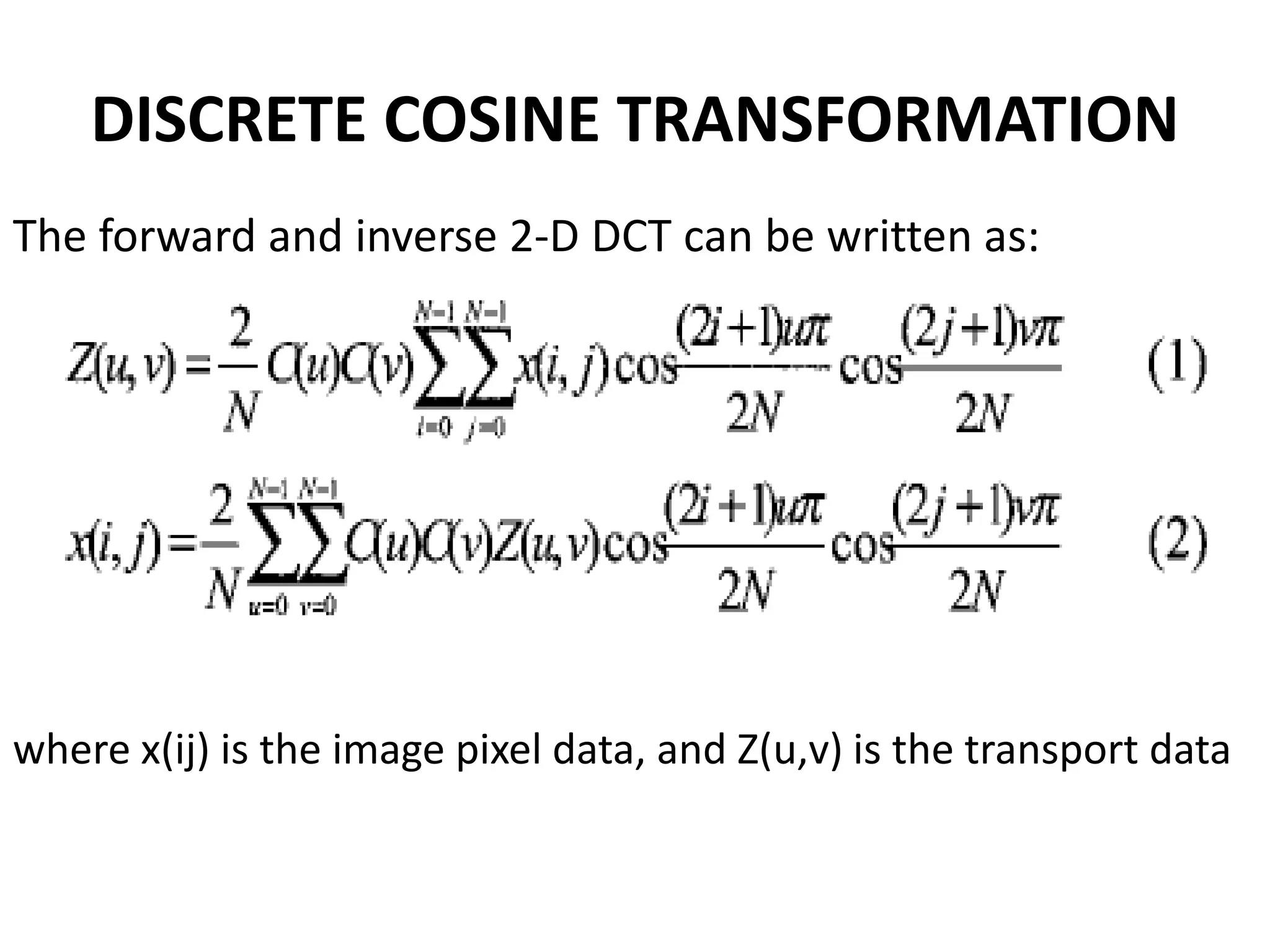

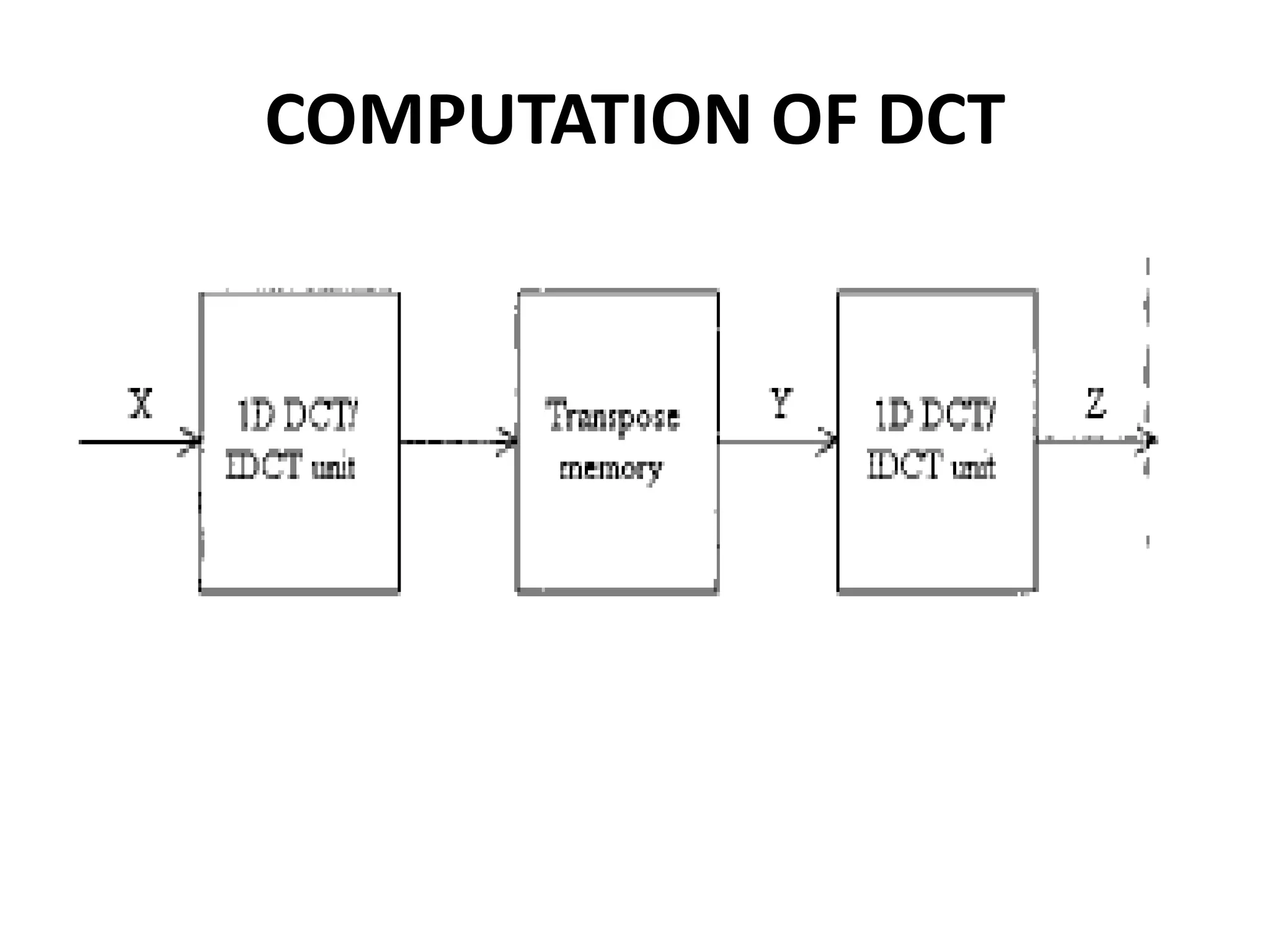

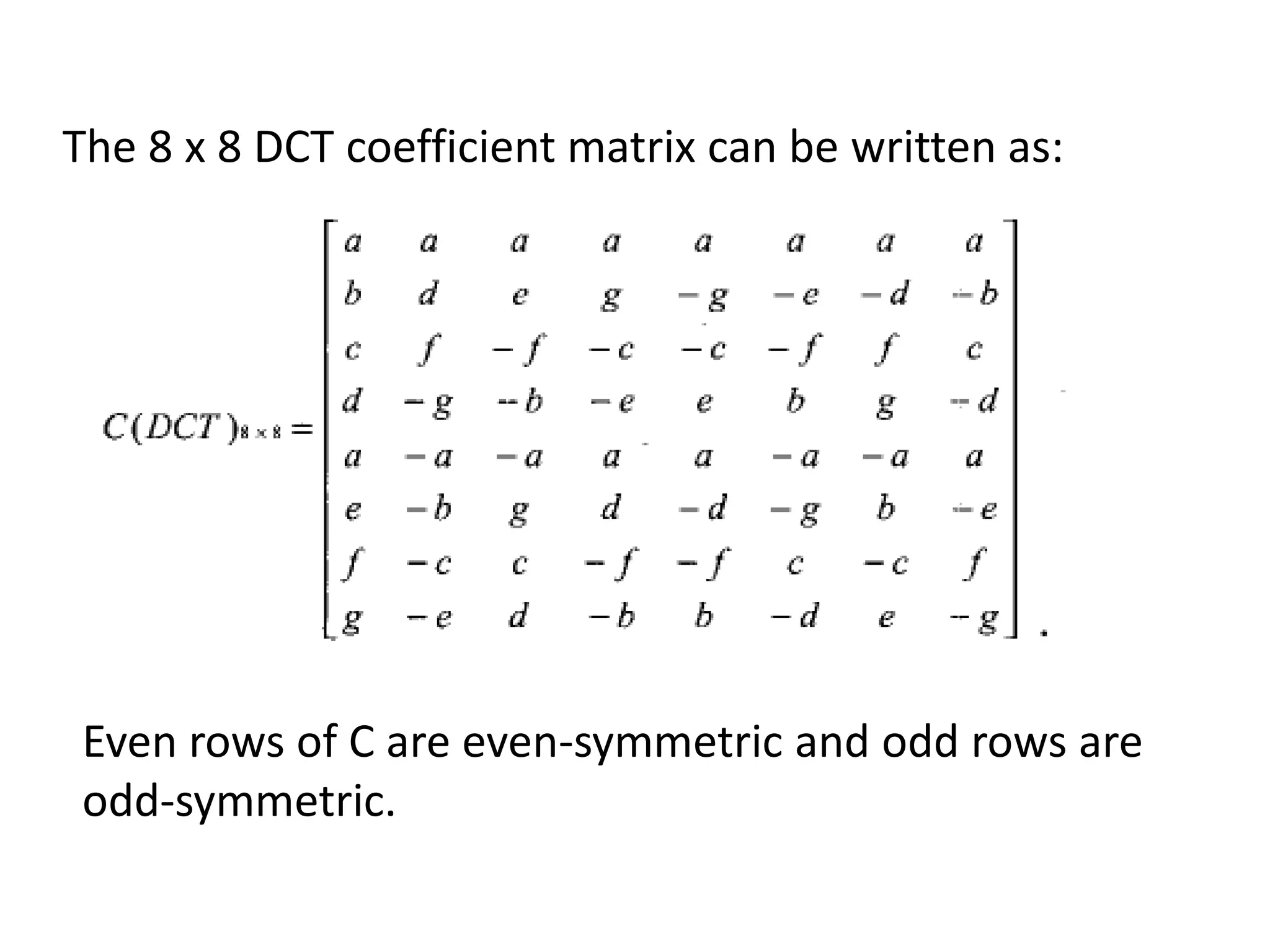

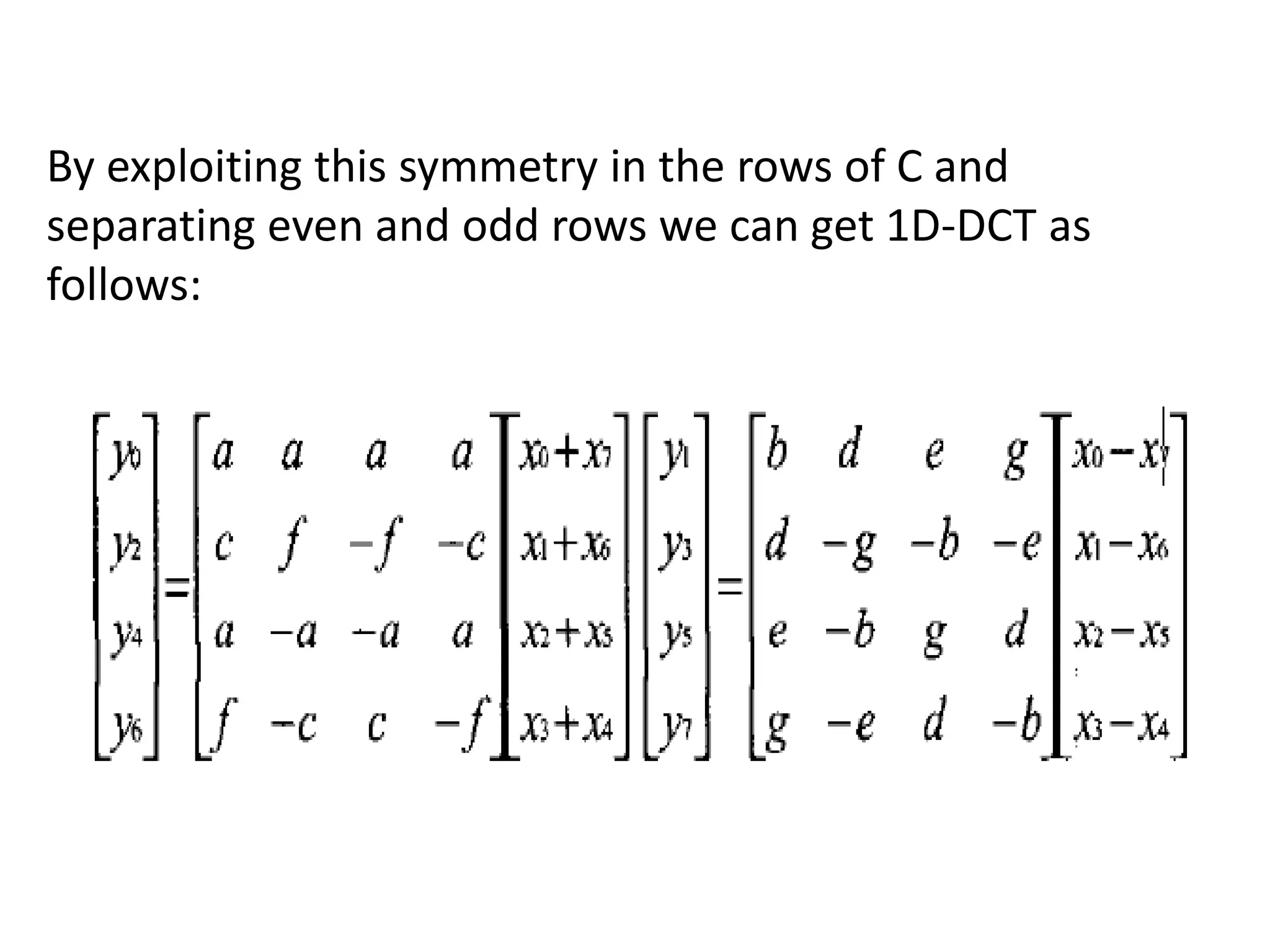

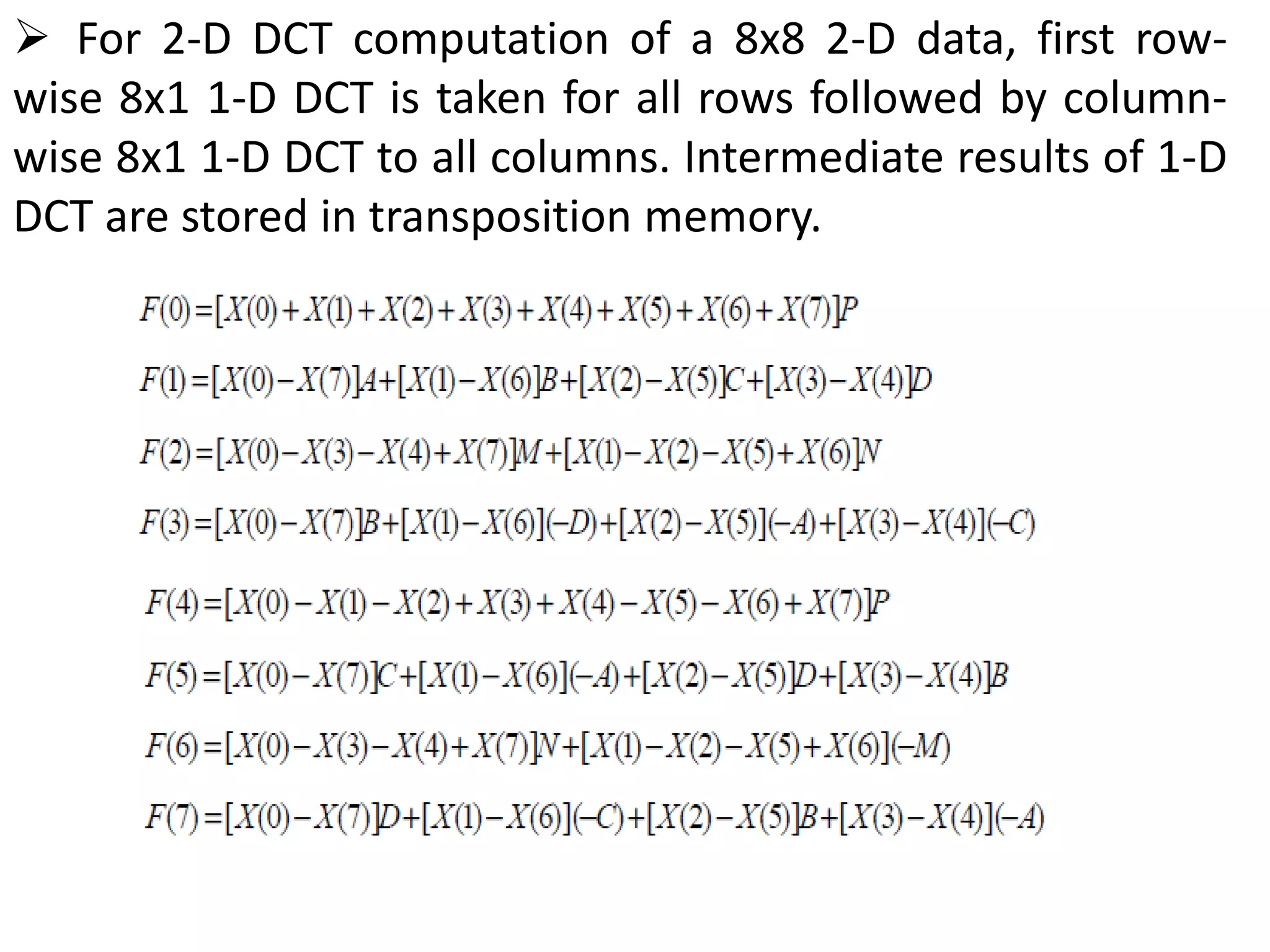

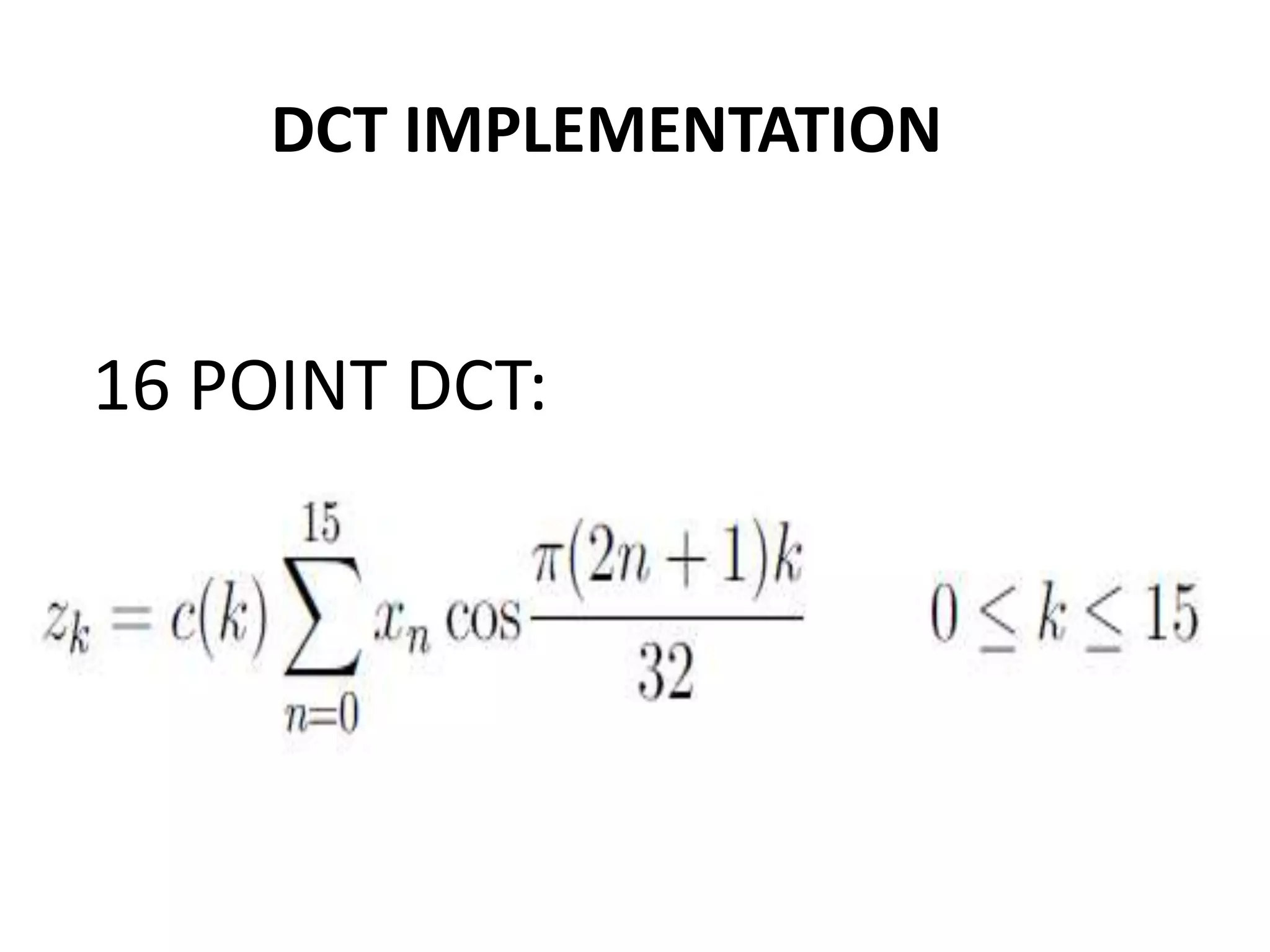

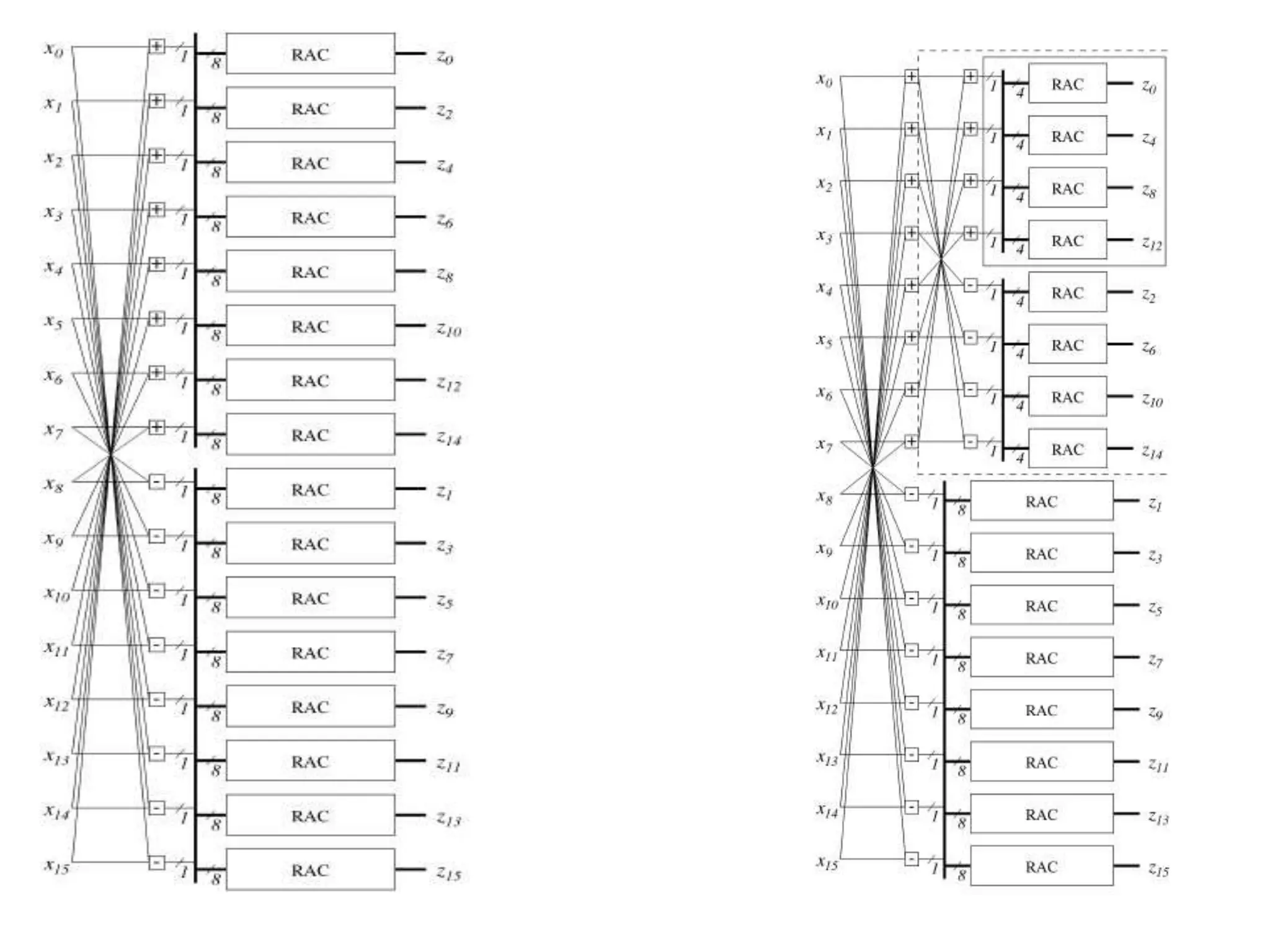

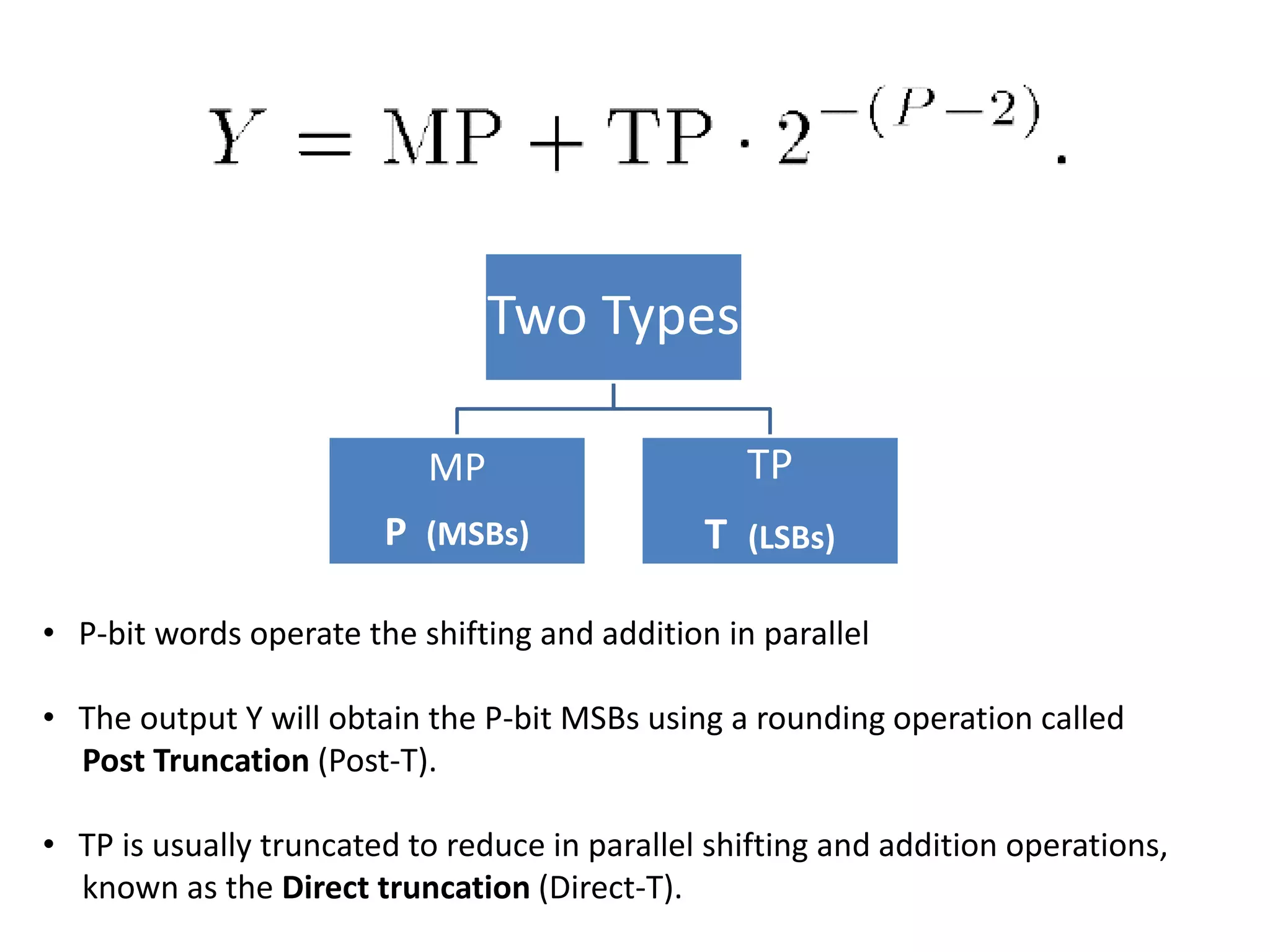

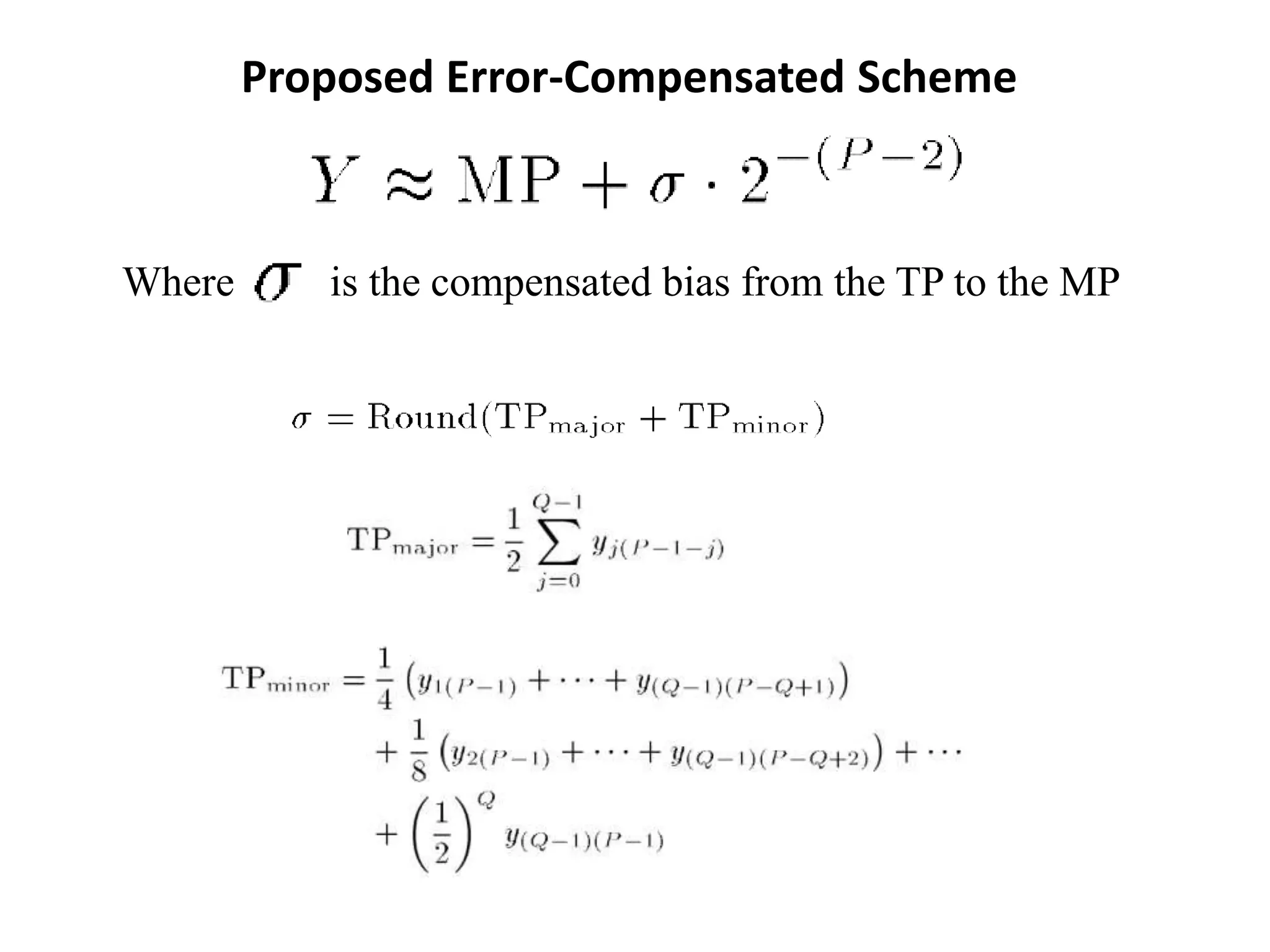

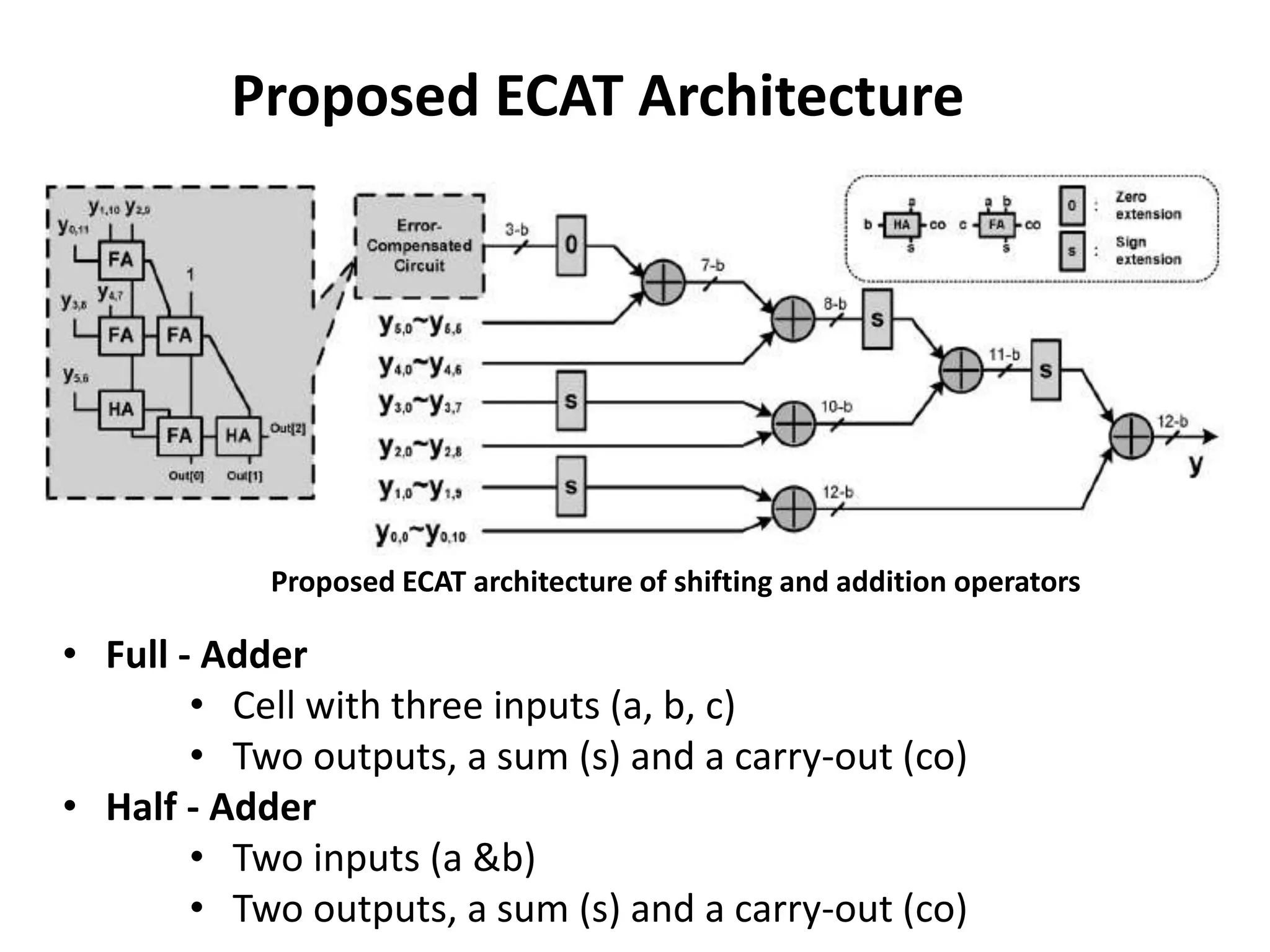

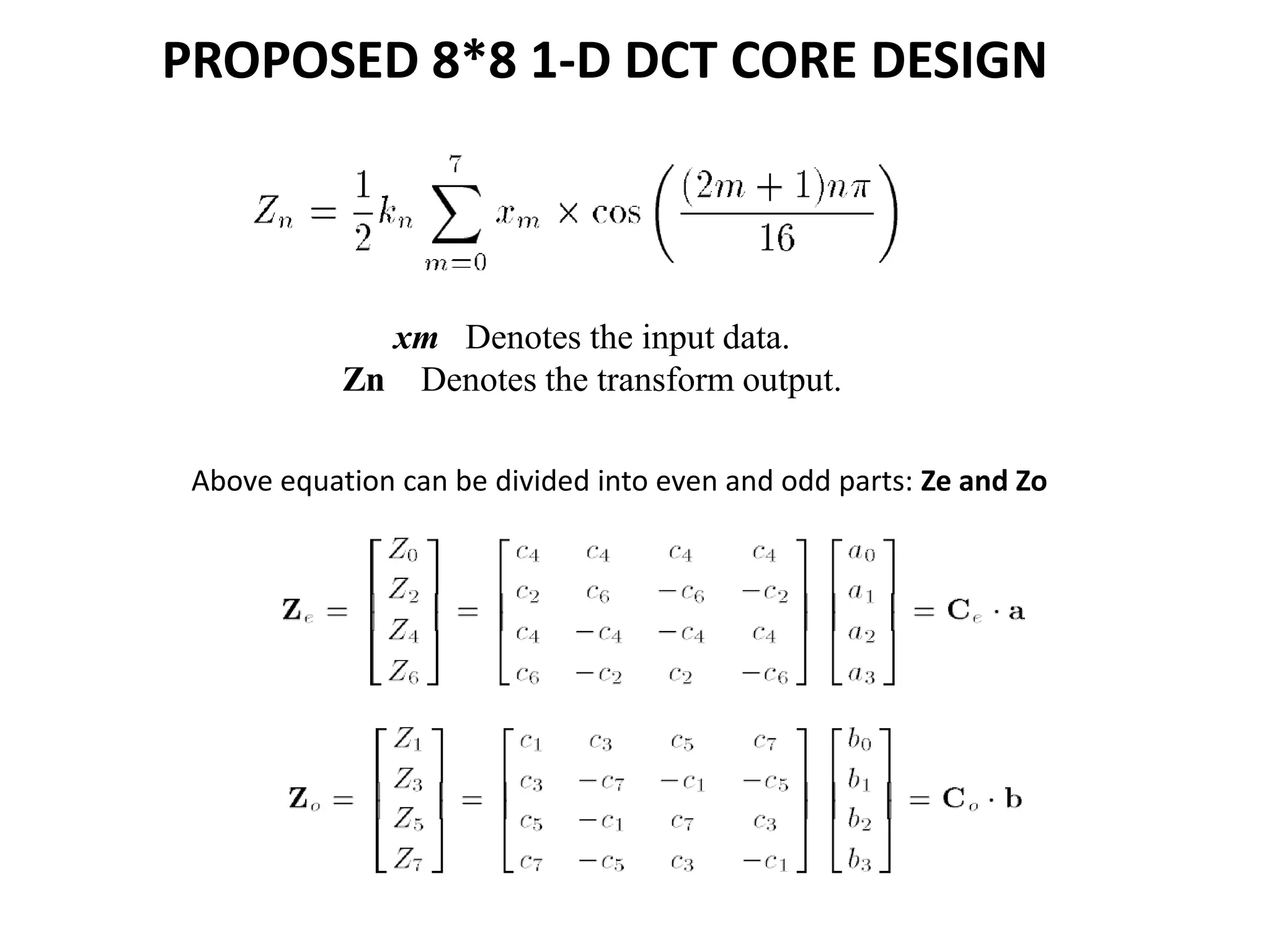

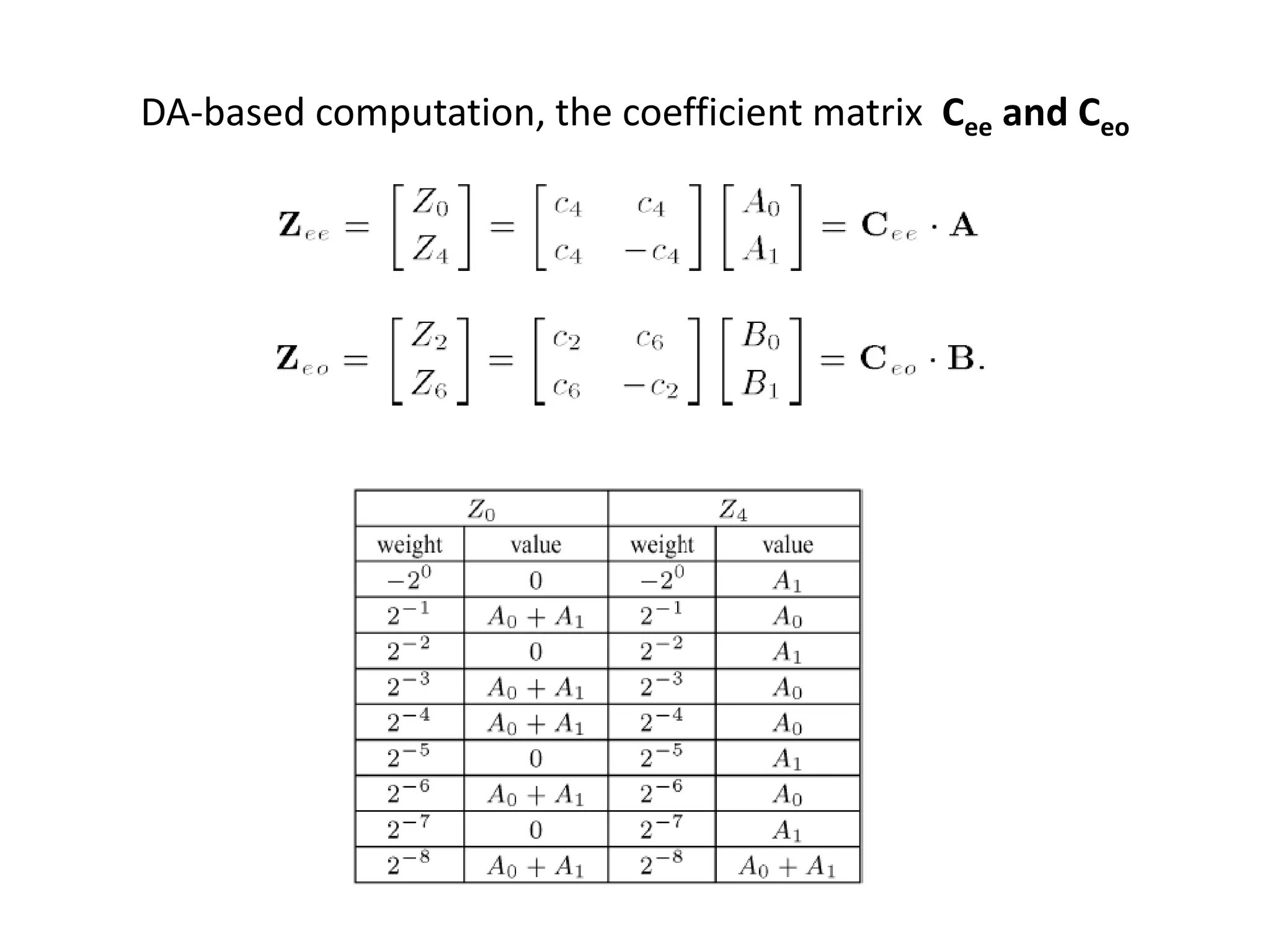

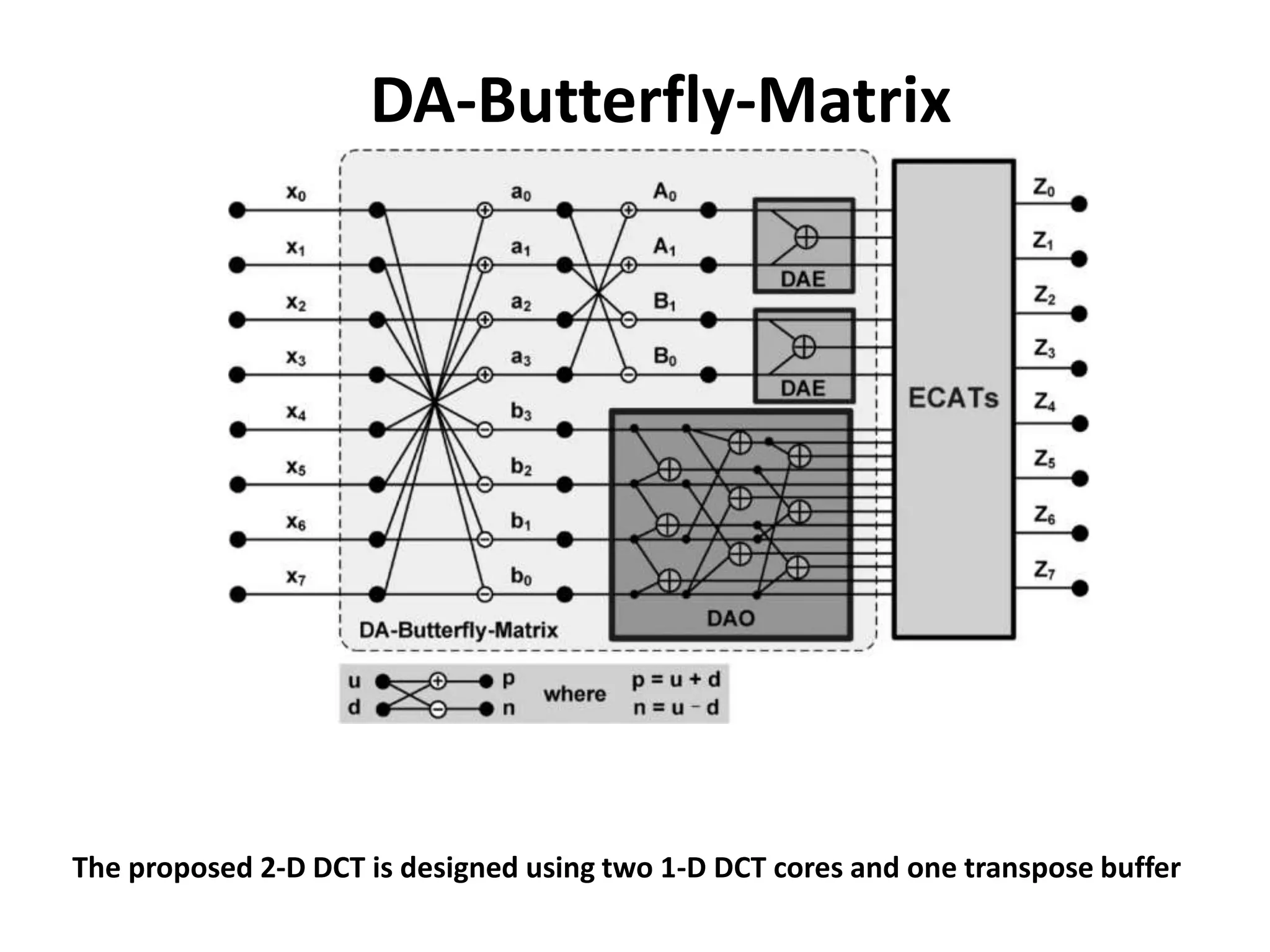

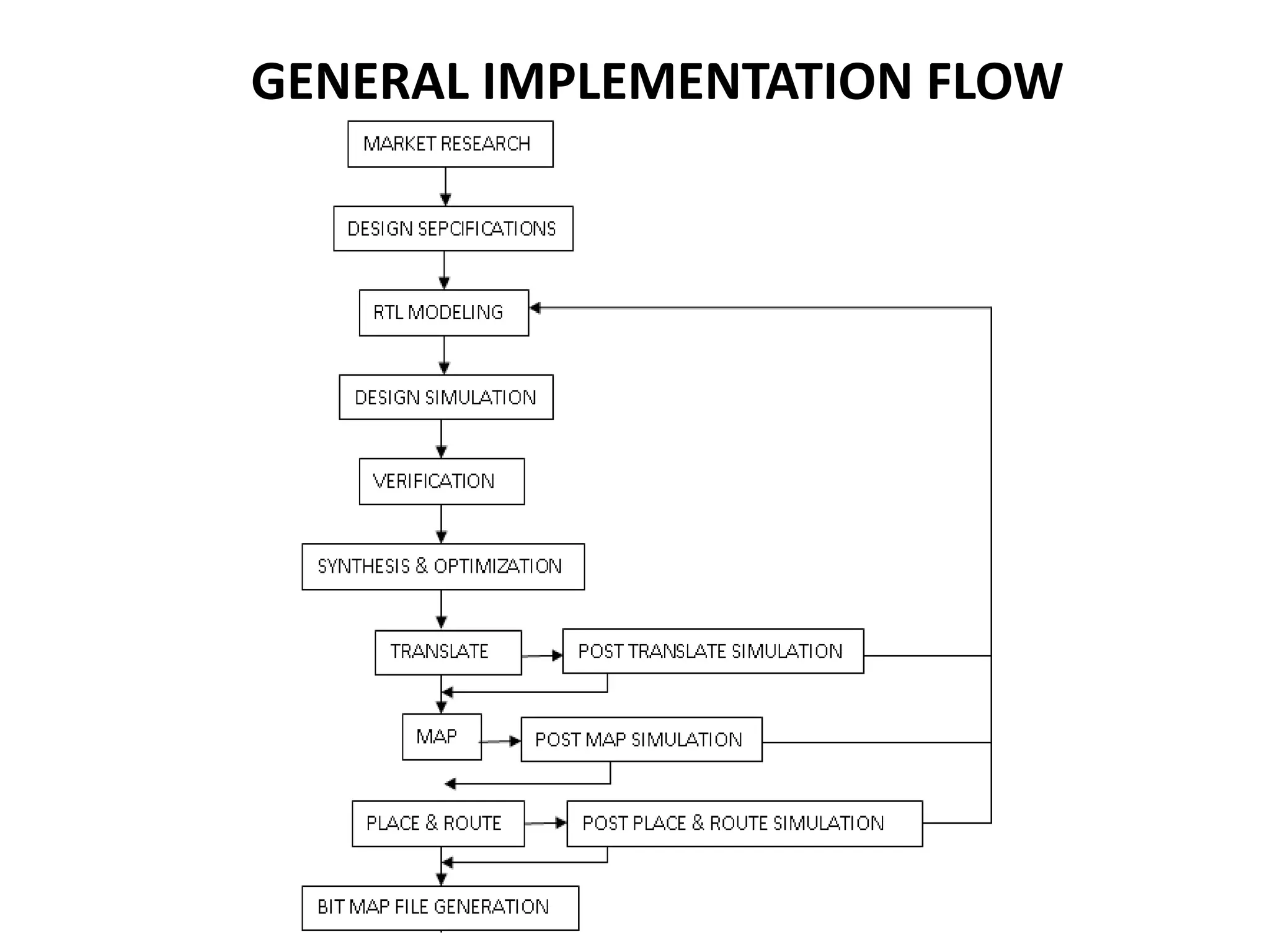

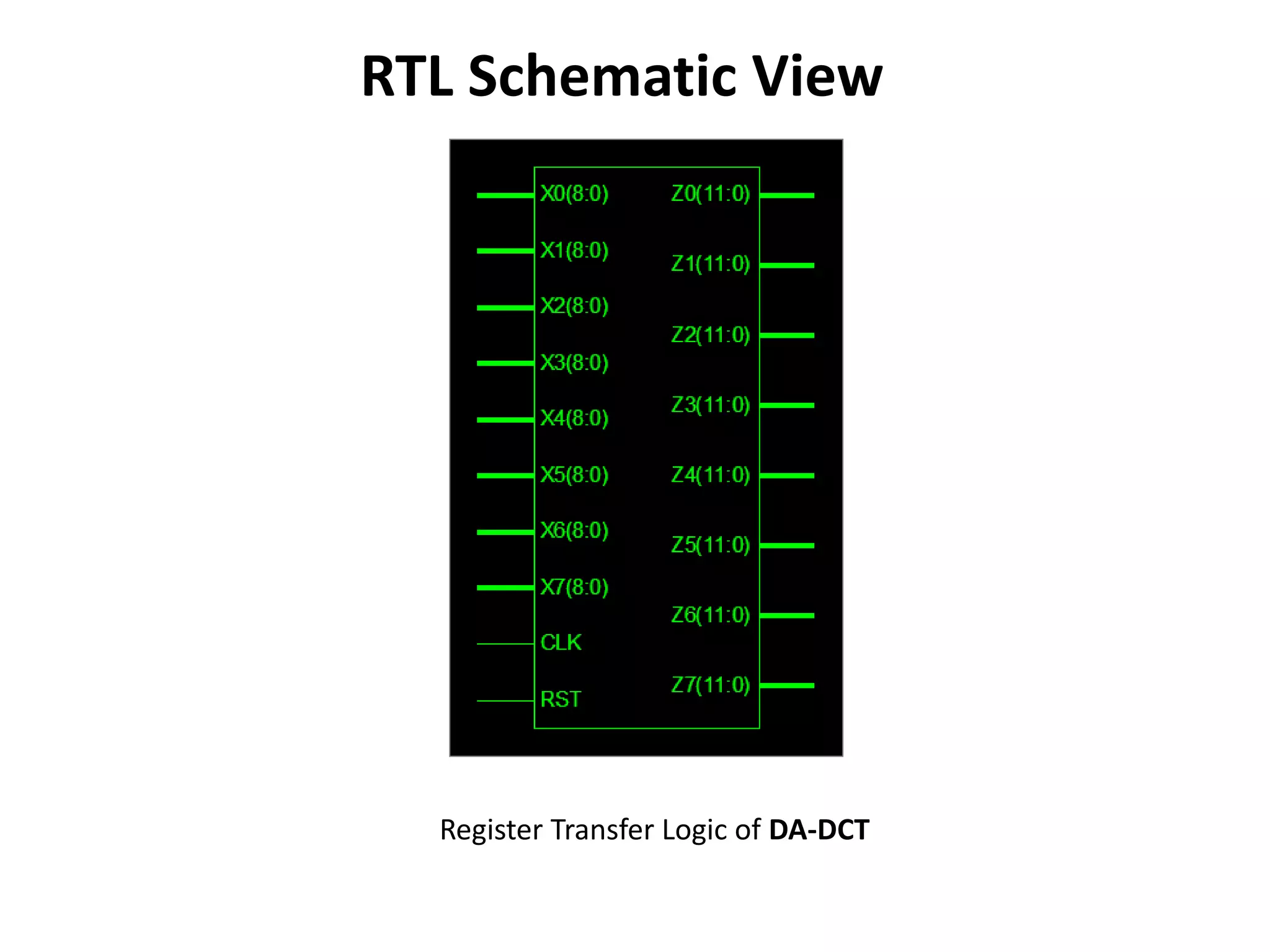

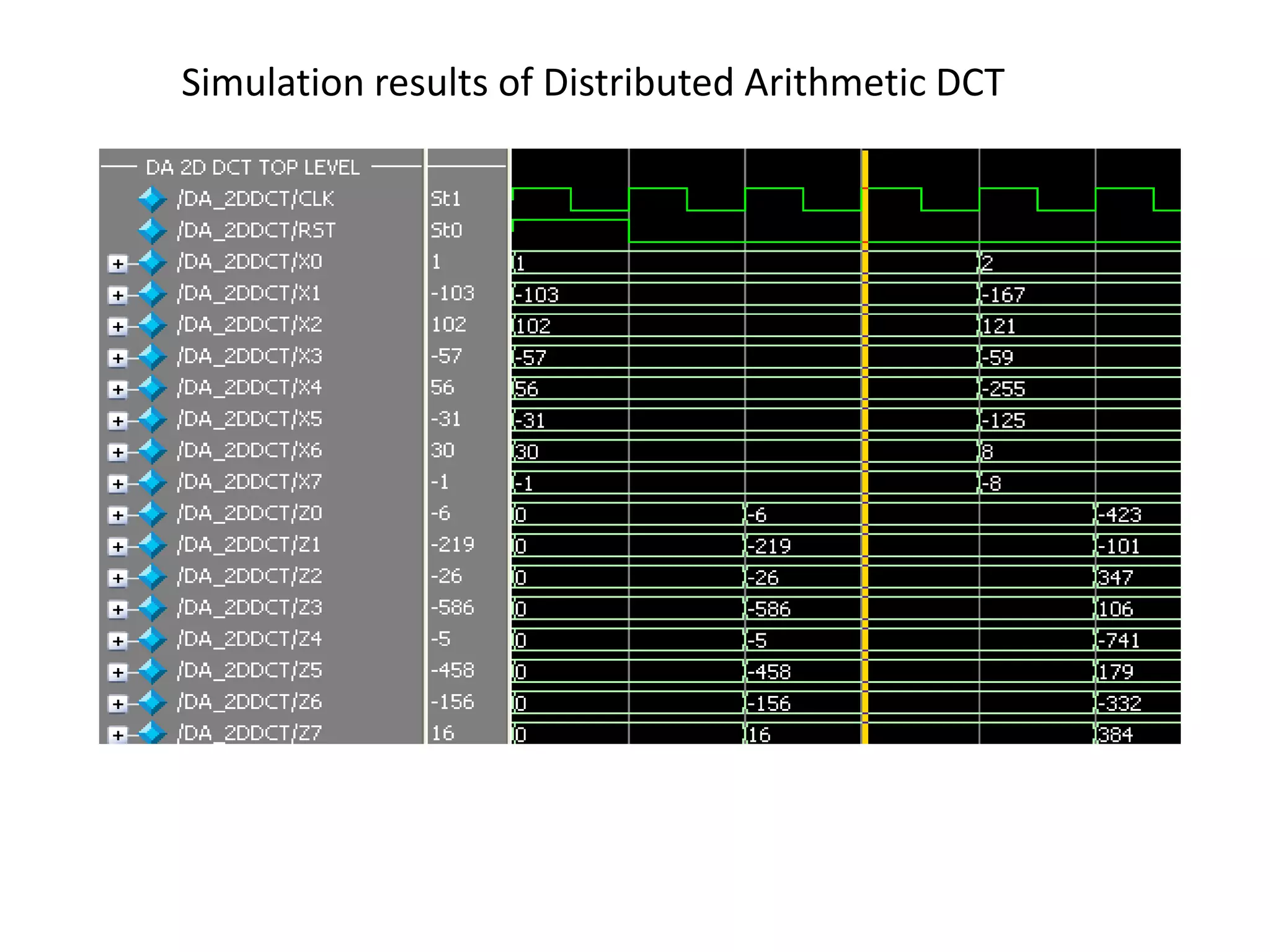

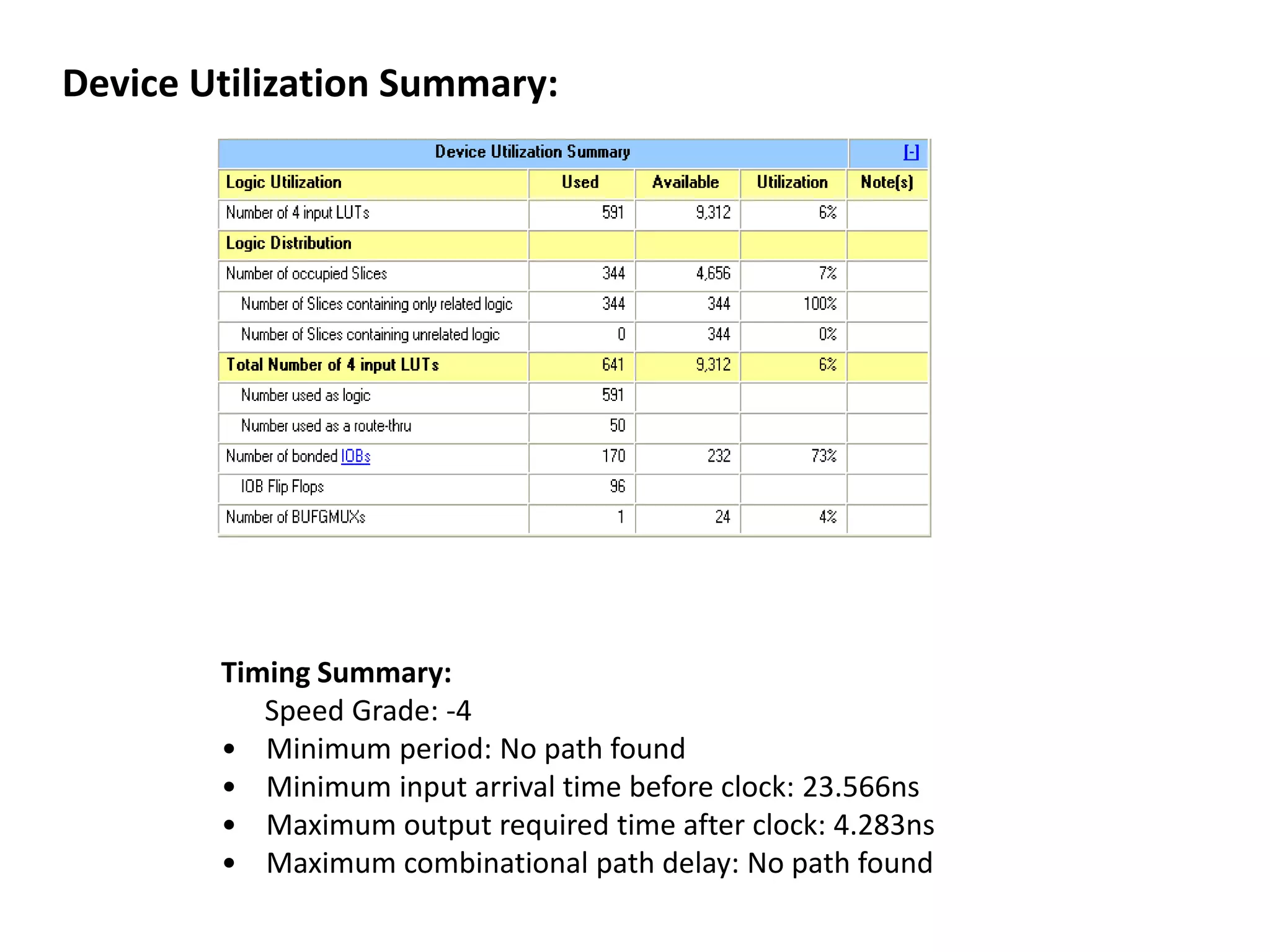

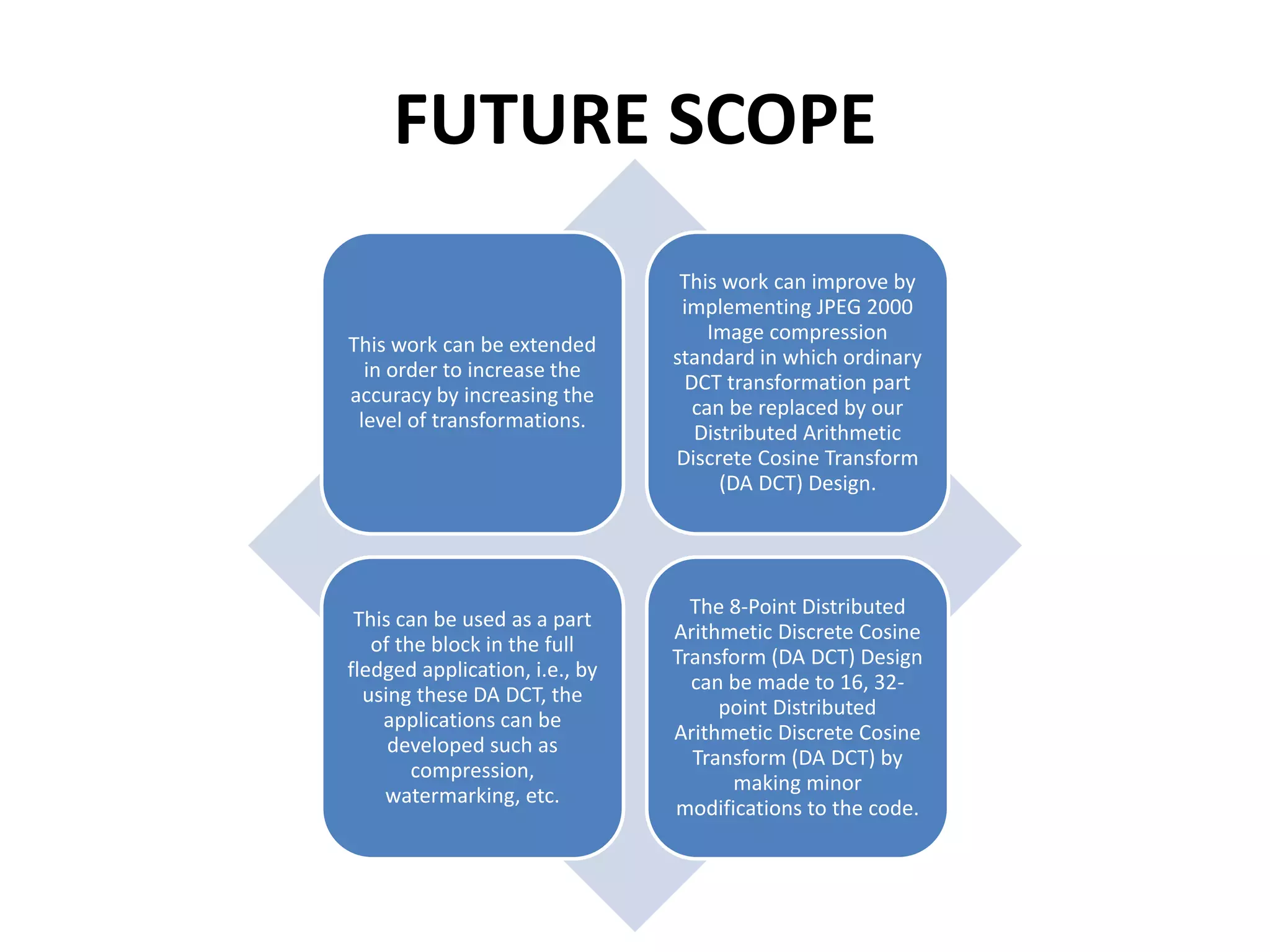

The document discusses the Distributed Arithmetic Discrete Cosine Transform (DA-DCT), detailing its application in VLSI (Very-Large-Scale Integration) design and compression techniques for digital signals. It highlights the importance of HDLs like Verilog and VHDL in electronic circuit design, and outlines the architecture and advantages of the DA-DCT method for efficient data compression. Additionally, future extensions for improving transformation accuracy and the potential for implementing JPEG 2000 standards are outlined.