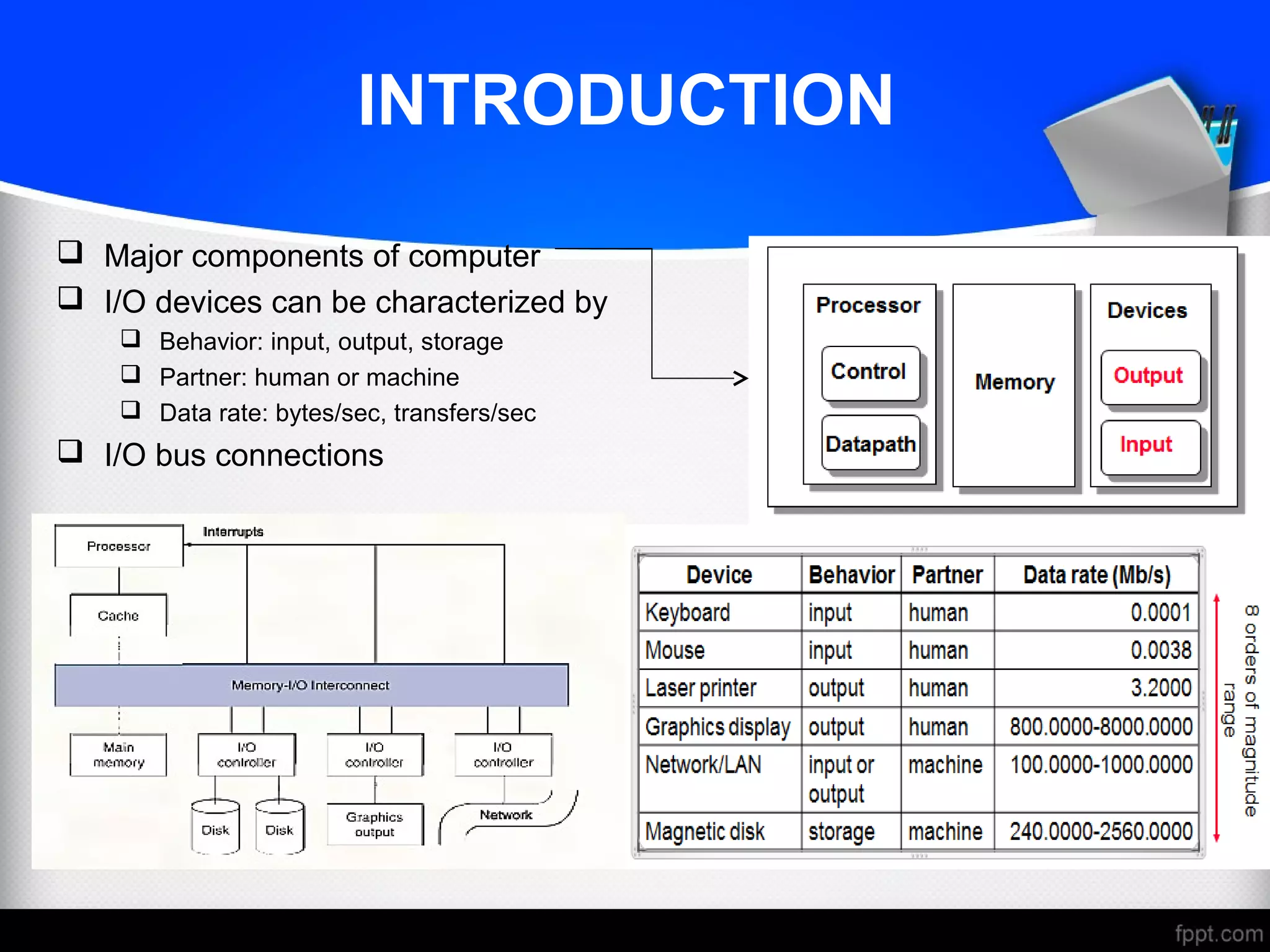

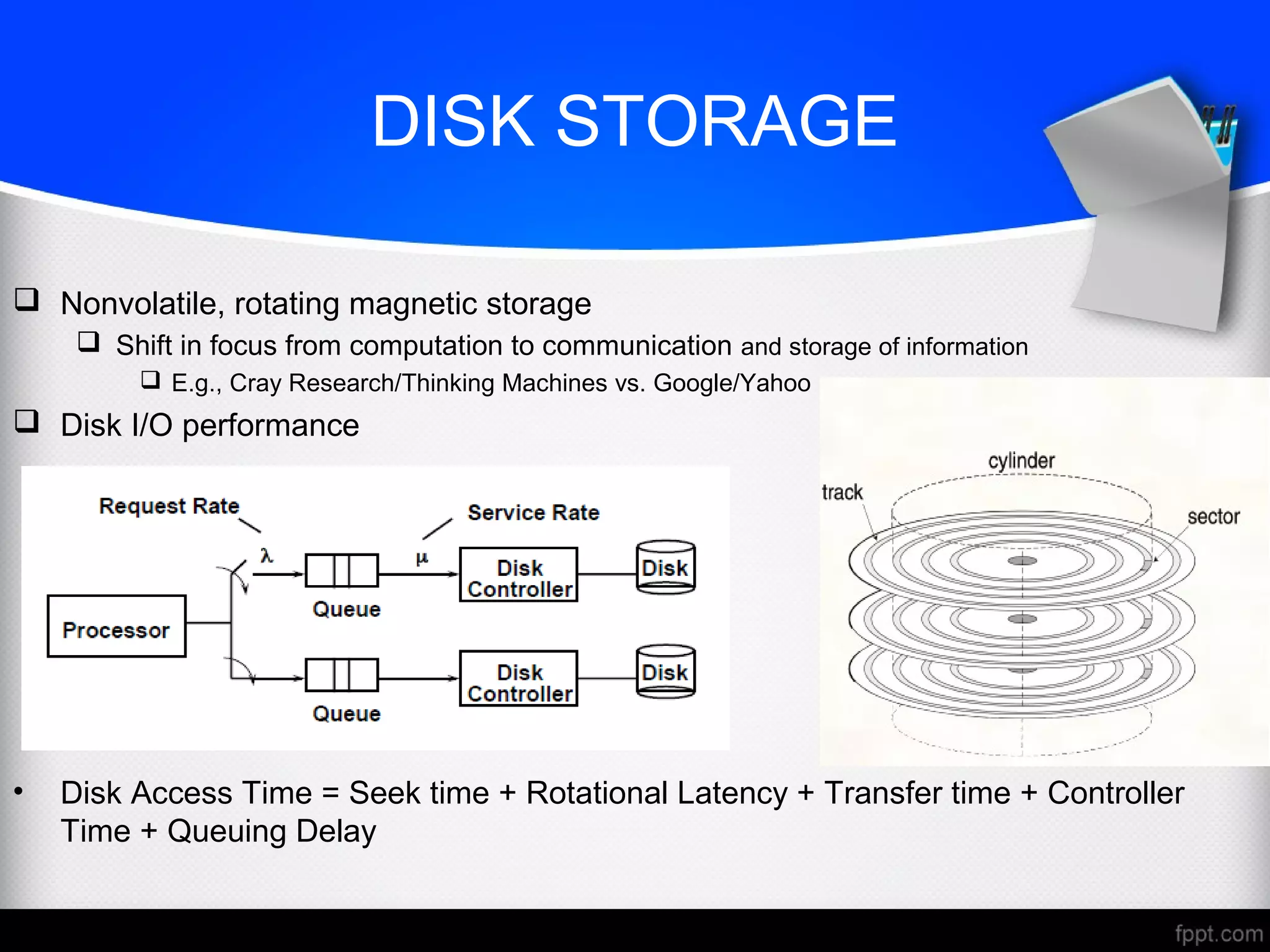

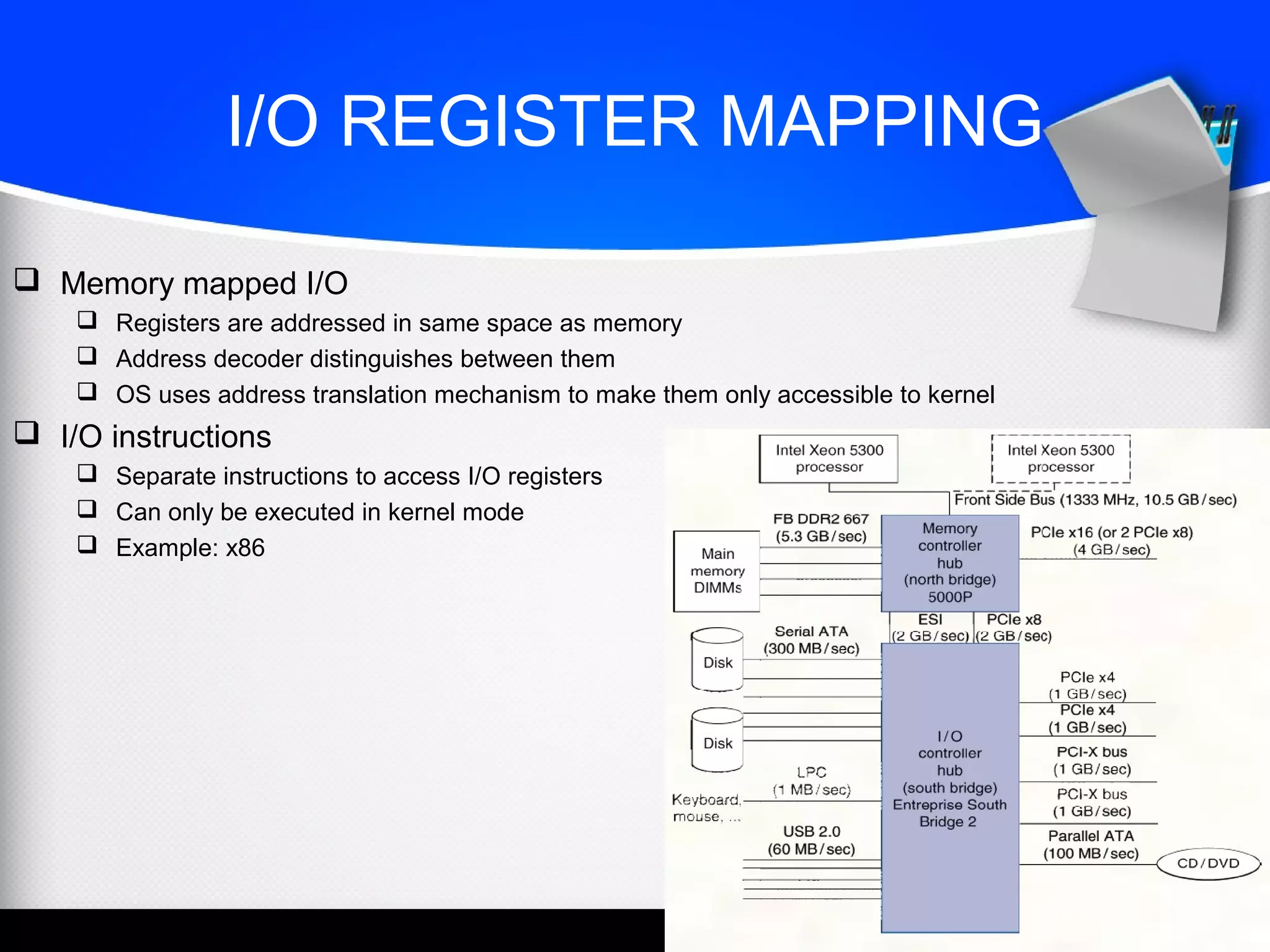

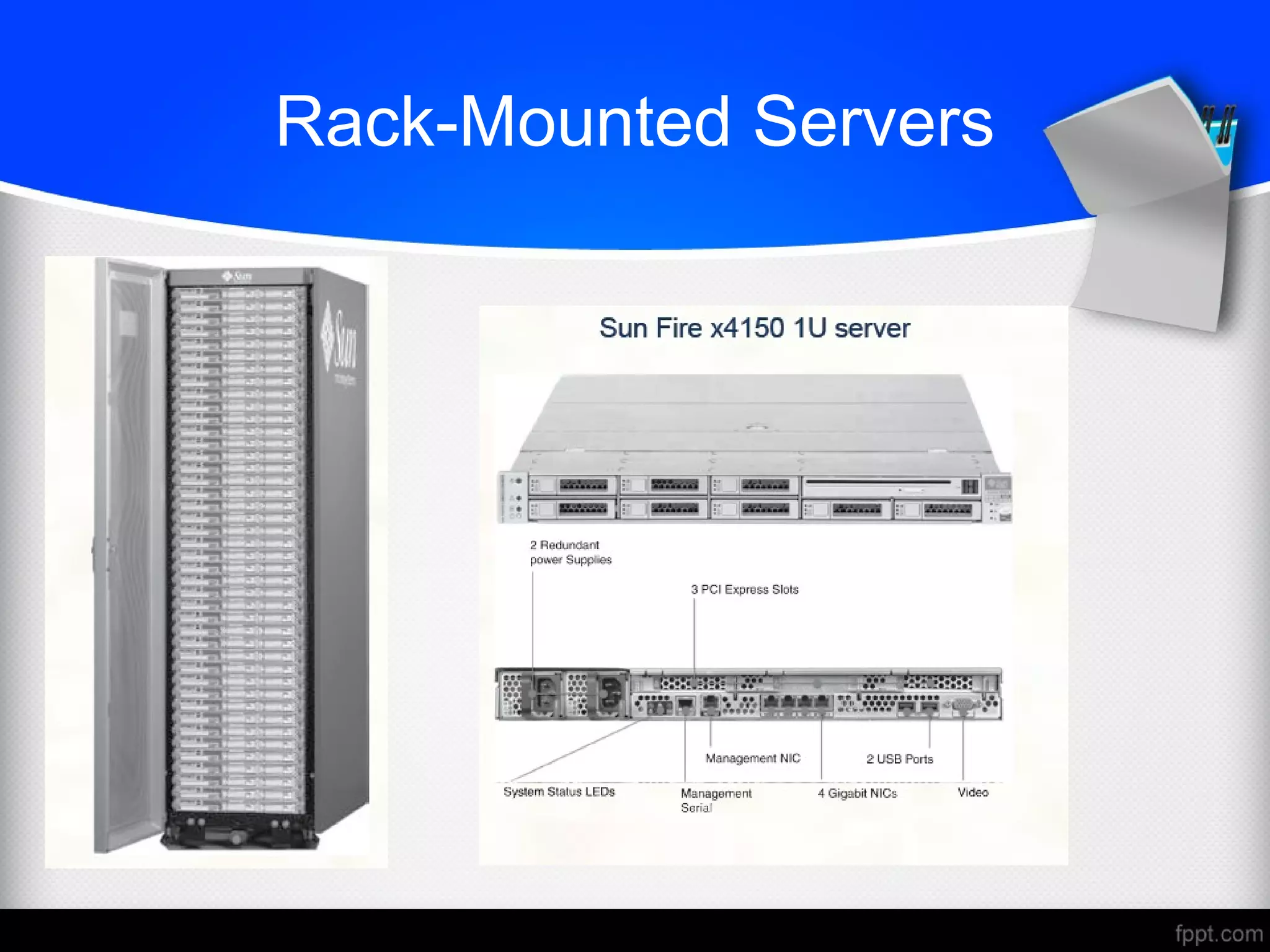

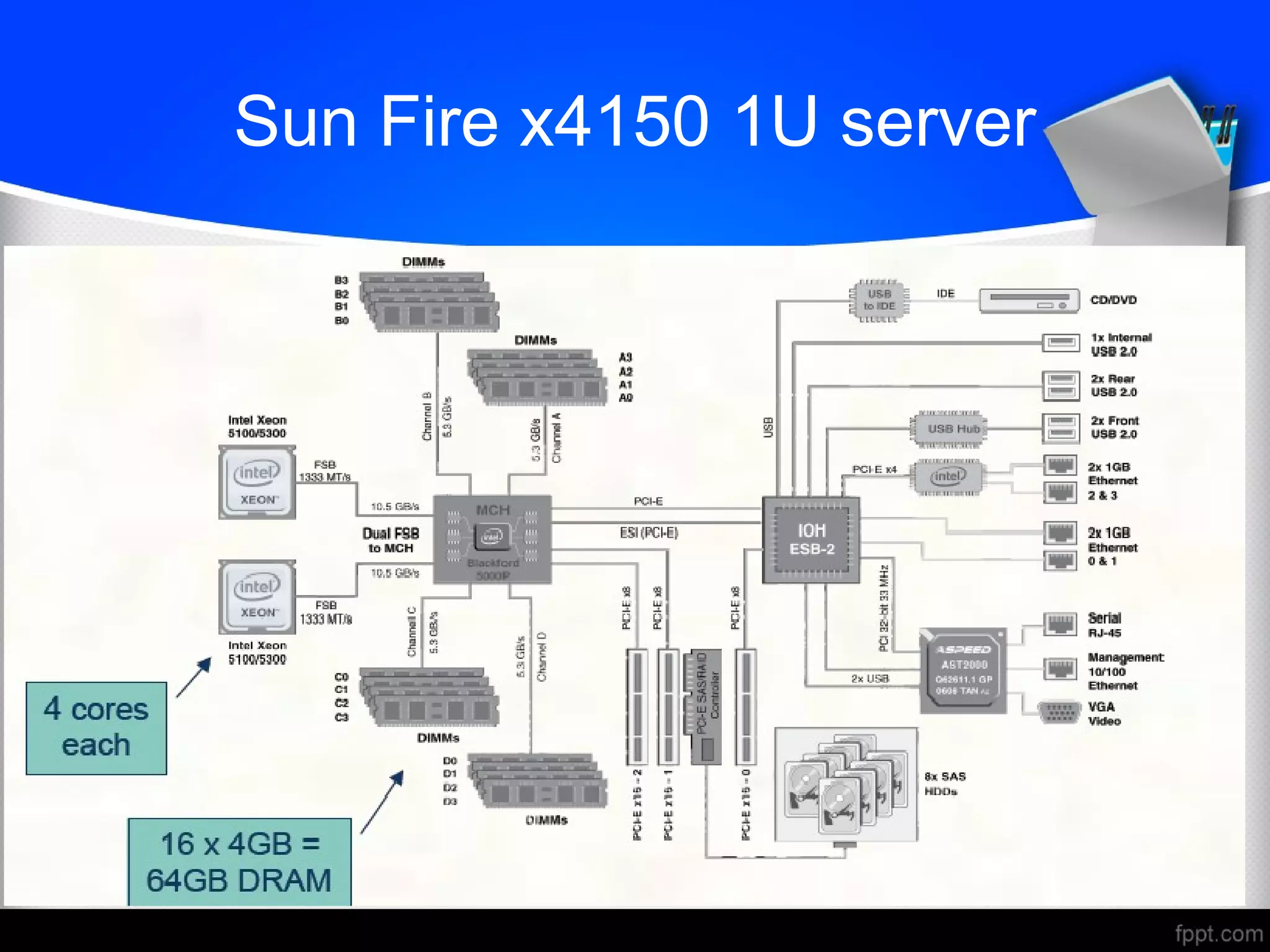

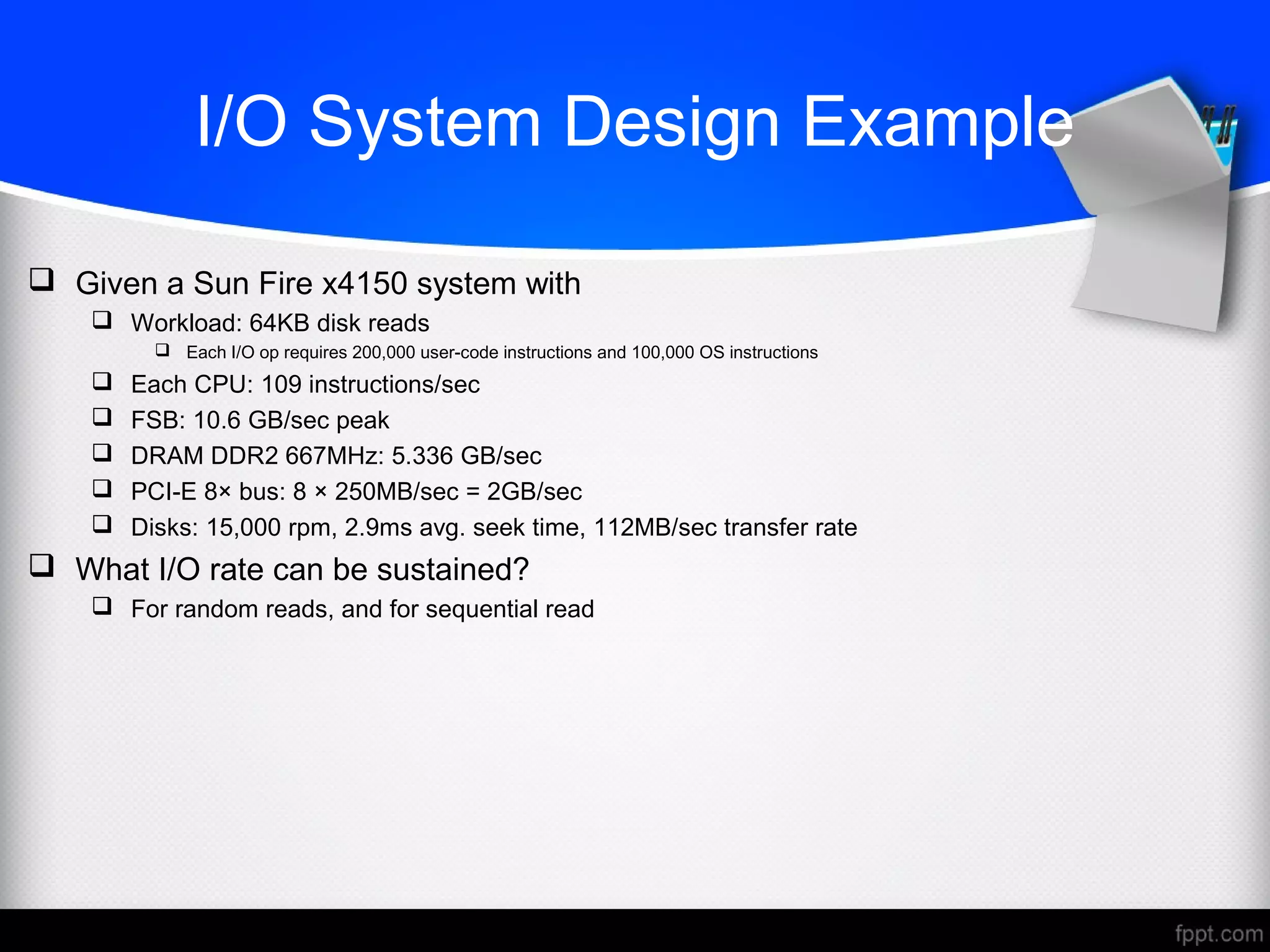

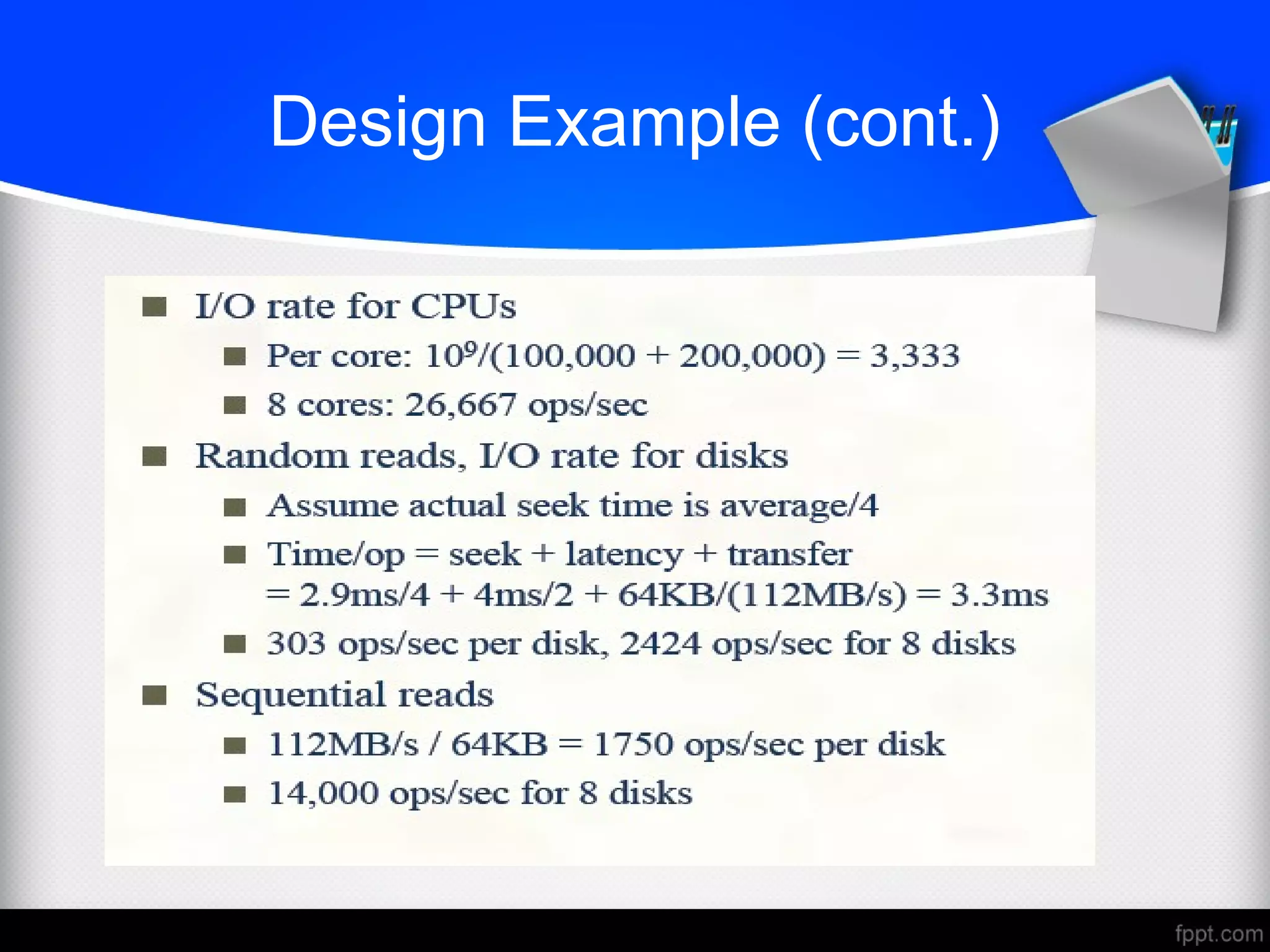

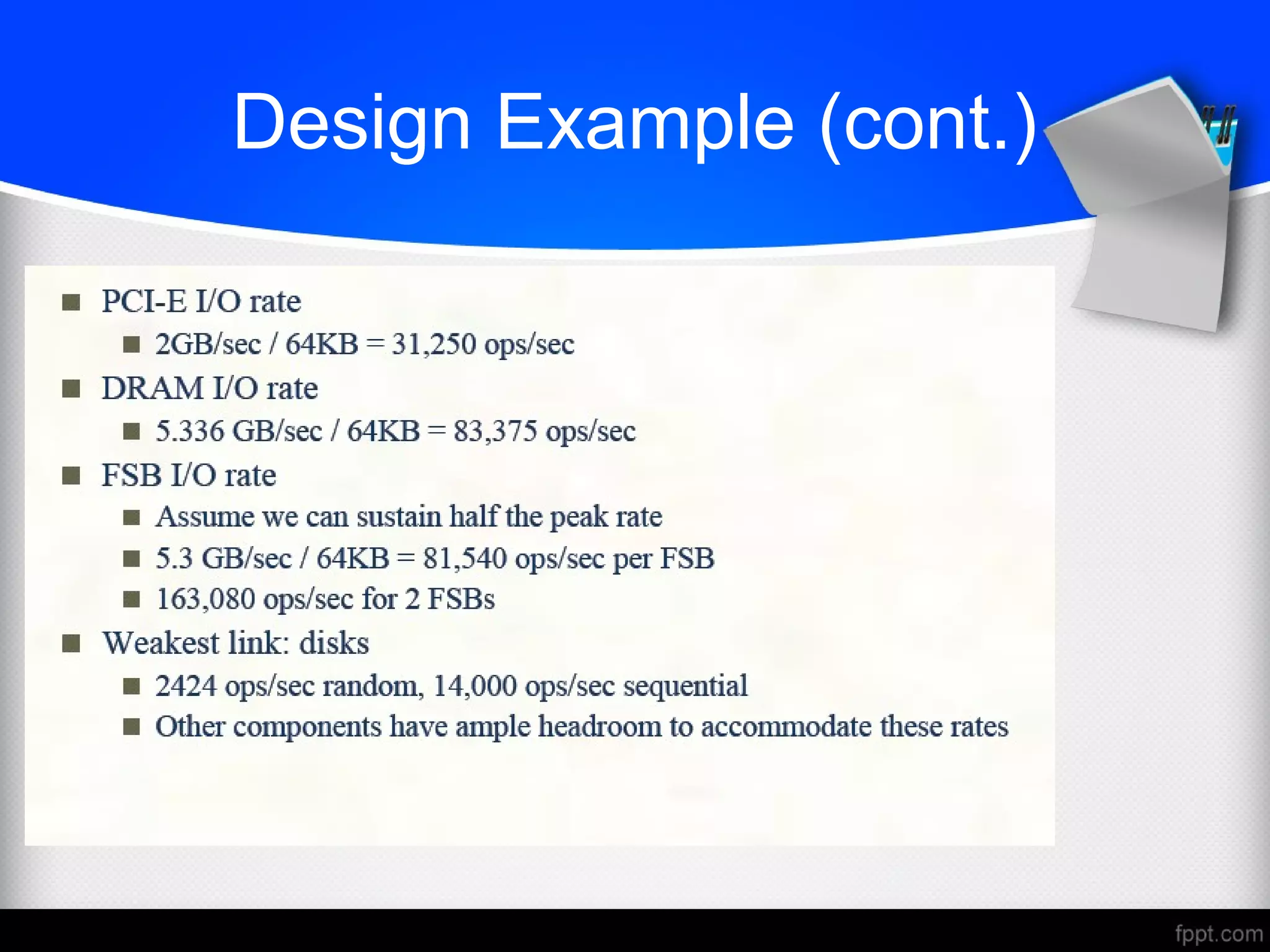

This document discusses I/O systems and their design. It describes the major components of I/O systems including devices, buses, and controllers. It discusses characteristics like performance, dependability, and expandability. Specific storage technologies like disks are examined in depth, covering aspects like seek time, rotational latency, and caching. The document also covers I/O programming techniques, buses, DMA, benchmarks, and example designs to optimize throughput and latency. A key consideration in design is balancing the workload between CPUs and I/O processors.