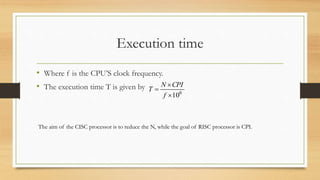

This document discusses the differences between Complex Instruction Set Computers (CISCs) and Reduced Instruction Set Computers (RISCs). CISCs use multi-step instructions to reduce the number of instructions needed, but this can decrease performance if the complex instructions take significantly longer to execute. RISCs aim to improve performance by limiting memory access to load and store instructions, keeping most data in registers to reduce processing time. While CISCs may have smaller programs, RISCs can have faster execution speeds by optimizing the number of clock cycles needed per instruction.