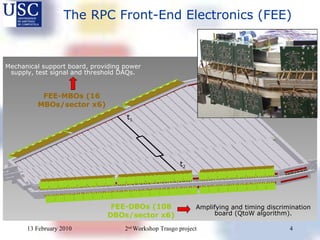

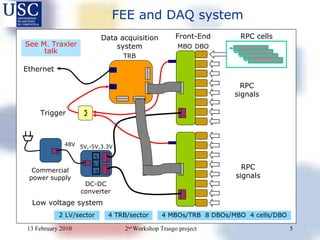

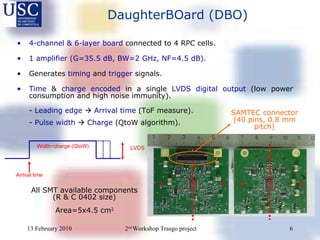

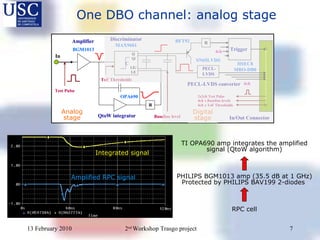

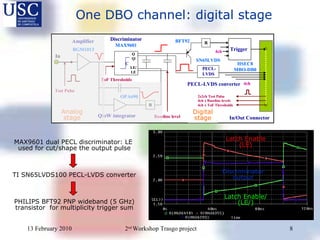

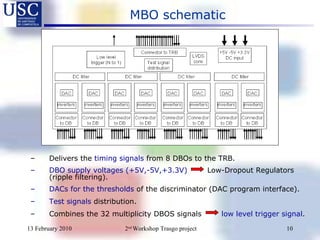

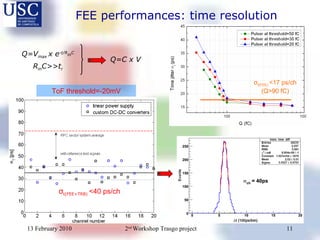

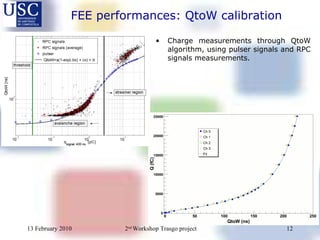

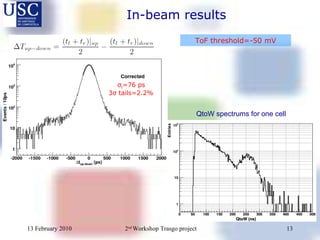

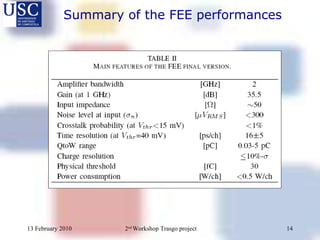

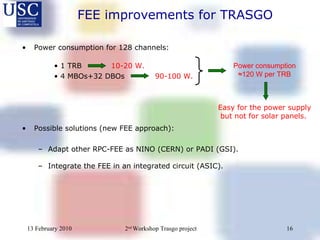

The document discusses the front-end electronics (FEE) developed for the timing RPCs used in the HADES experiment. The FEE consists of daughter boards (DBOs) connected to the RPC cells that amplify and digitize signals, and mother boards (MBOs) that interface between the DBOs and data acquisition system. The FEE achieves a time resolution of less than 17 ps using a charge-to-width algorithm to encode timing and charge information. Testing shows the FEE performs well and could be adapted for use in the TRASGO detector with some modifications to reduce power consumption.