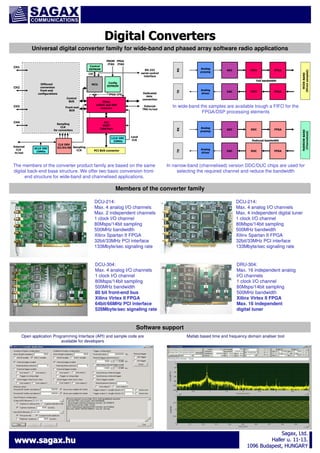

This document summarizes a universal digital converter family for software radio applications. It offers two front-end configurations: wide-band direct sampling and narrow-band channelized. In wide-band mode, samples are available through a FIFO for FPGA/DSP processing. In narrow-band mode, DDC/DUC chips are used to select channels and reduce bandwidth. The family includes products with up to 4 or 16 channels that sample at 80Msps with 14-bit resolution and 500MHz bandwidth, and interface with FPGAs and PCI buses. Open APIs and sample code are provided for developers.