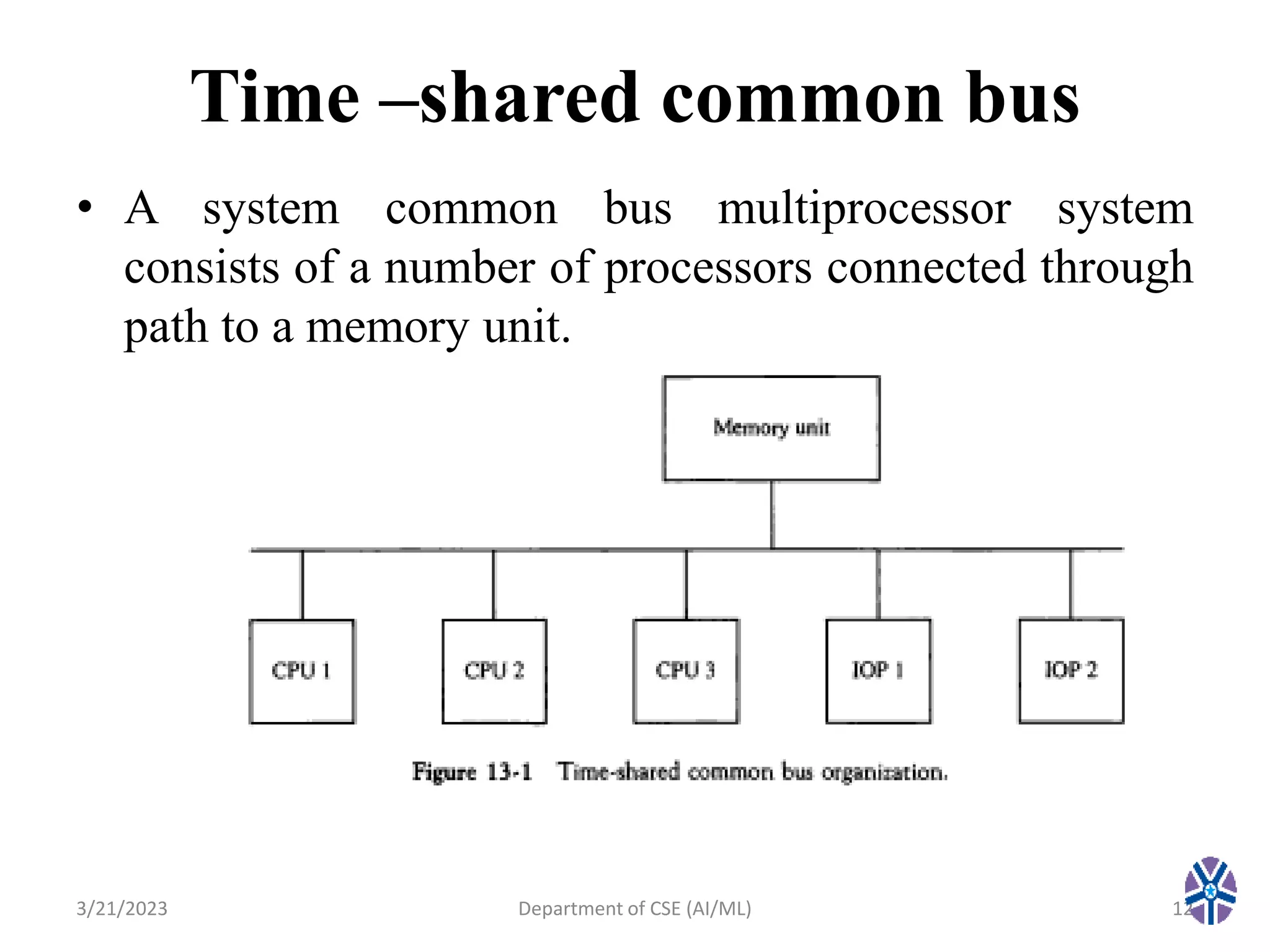

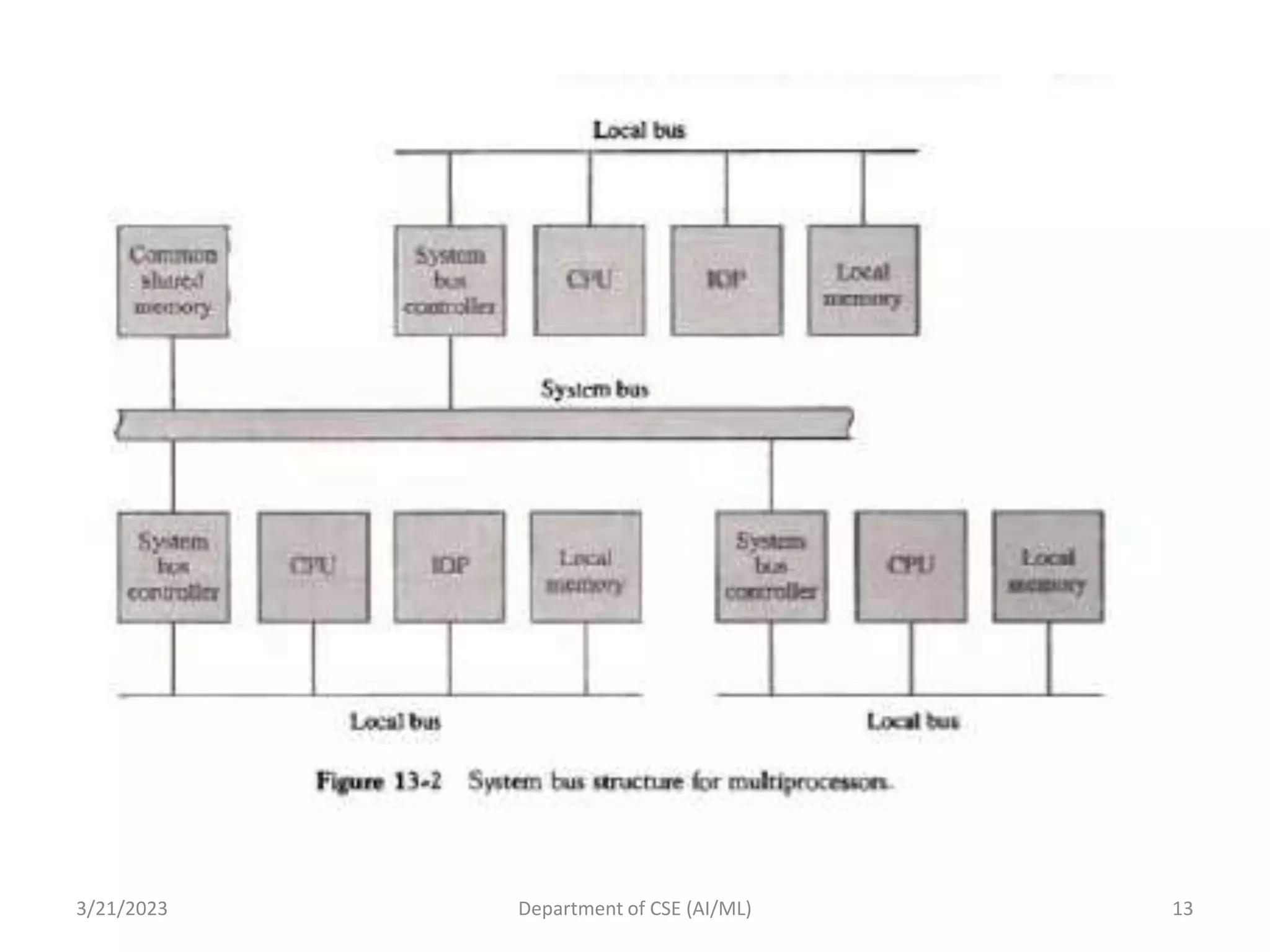

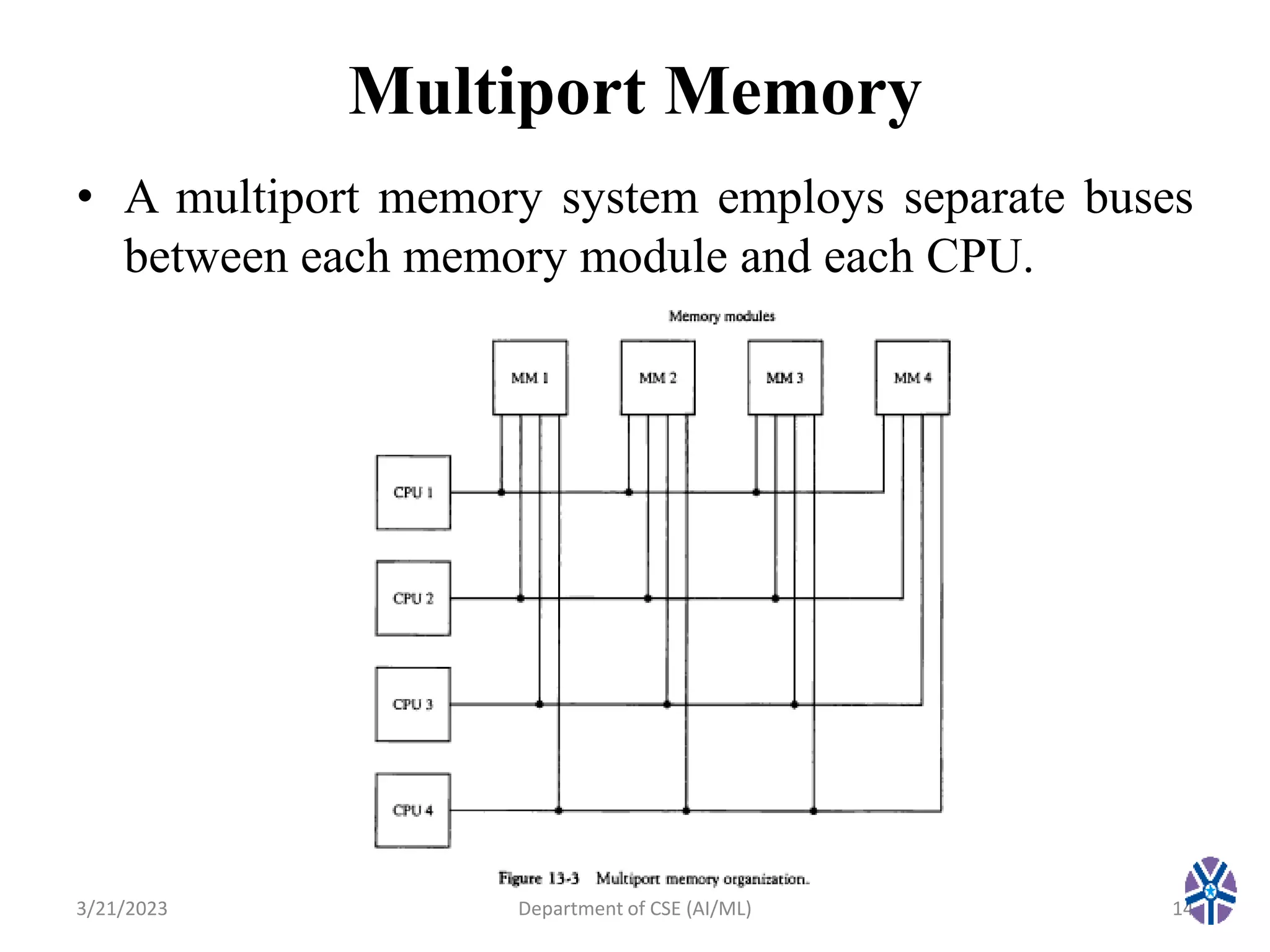

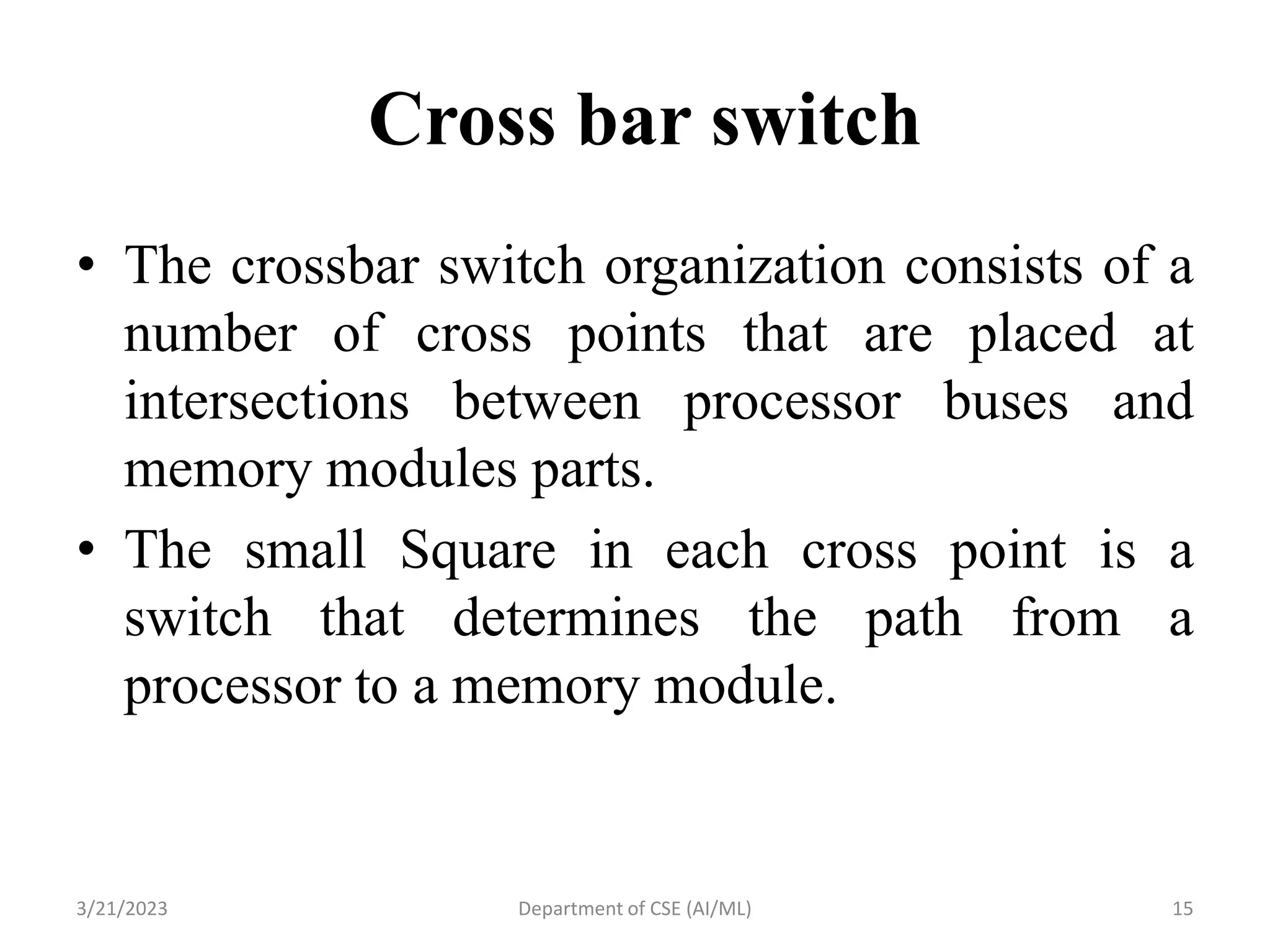

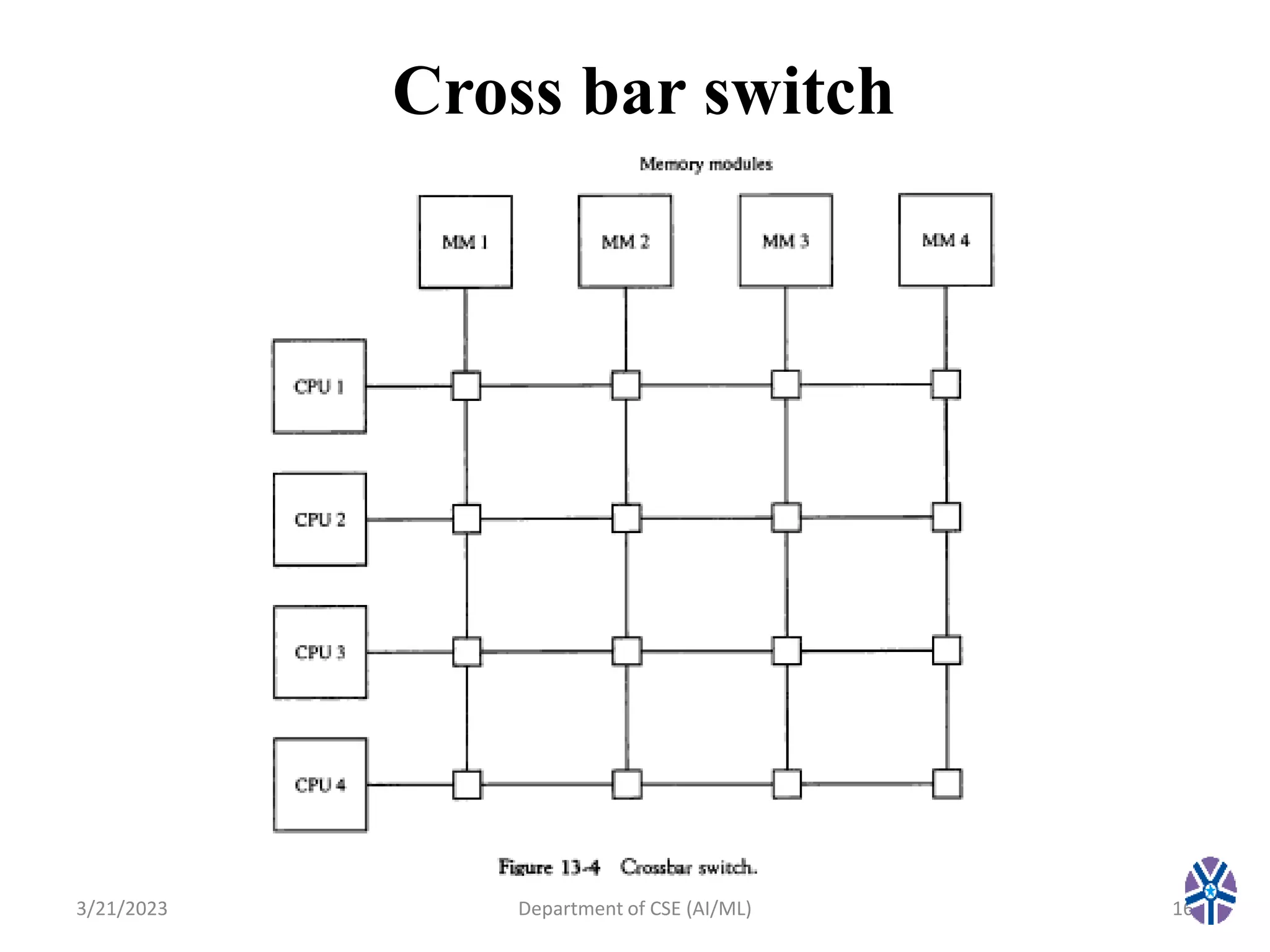

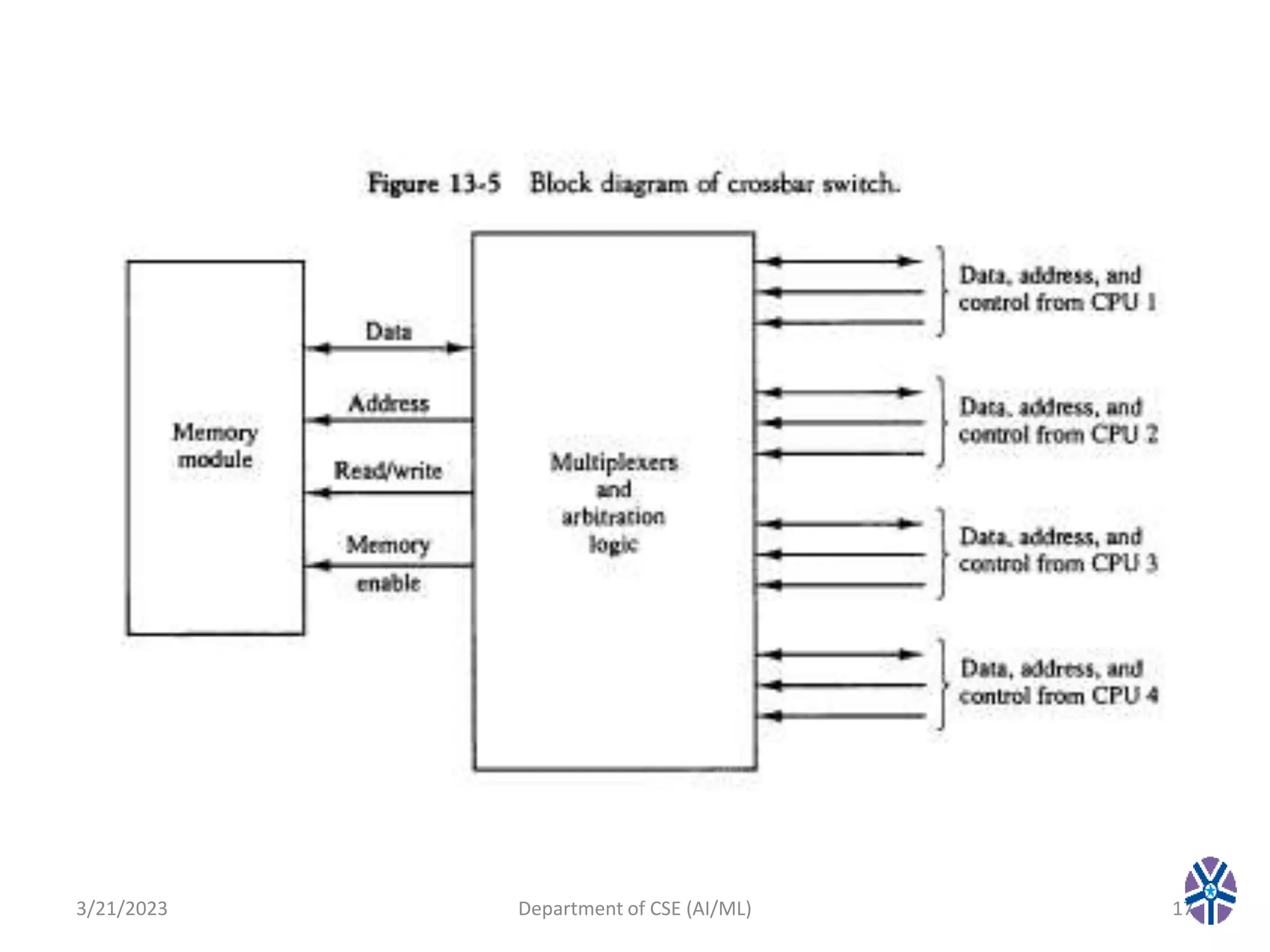

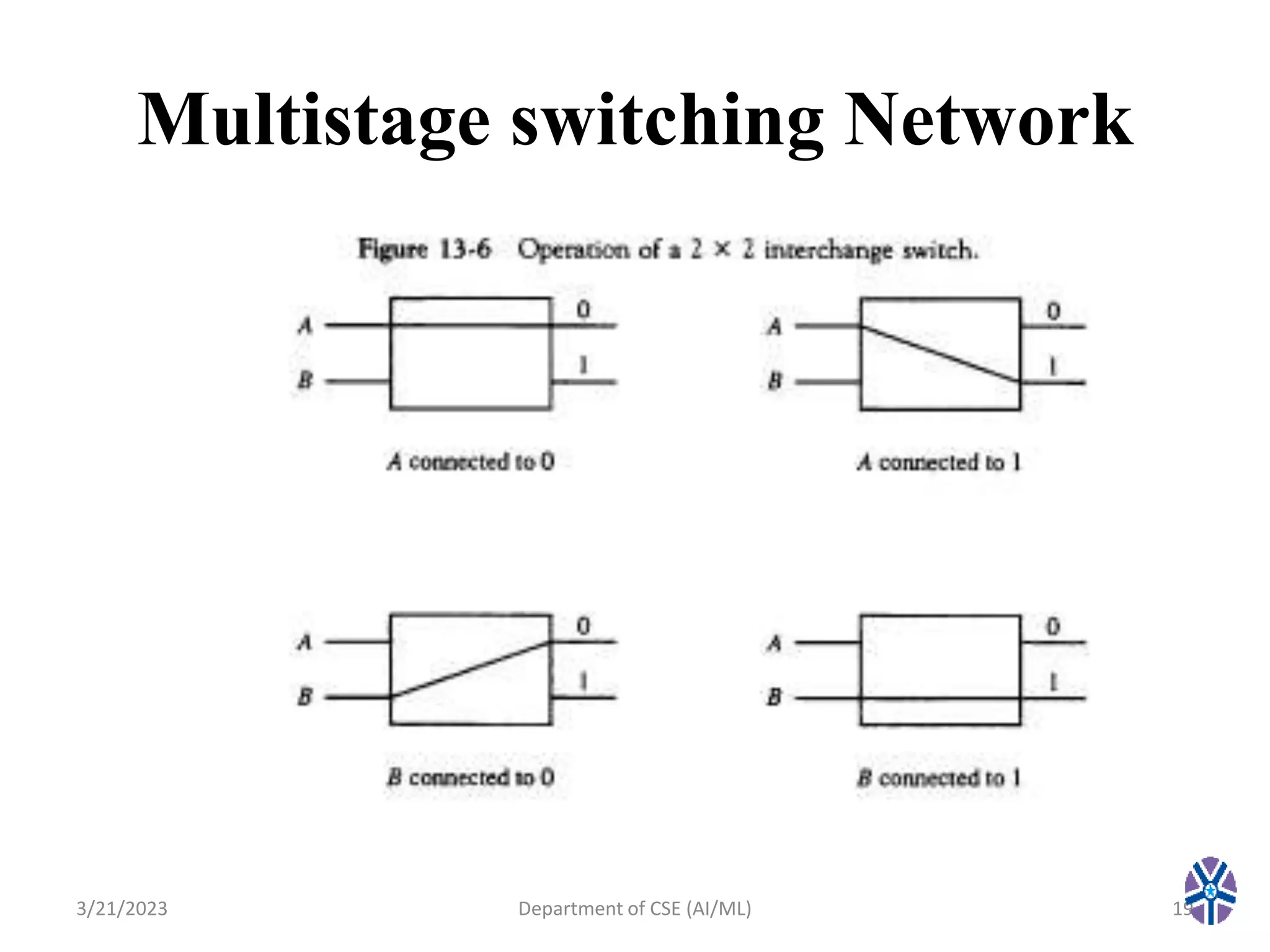

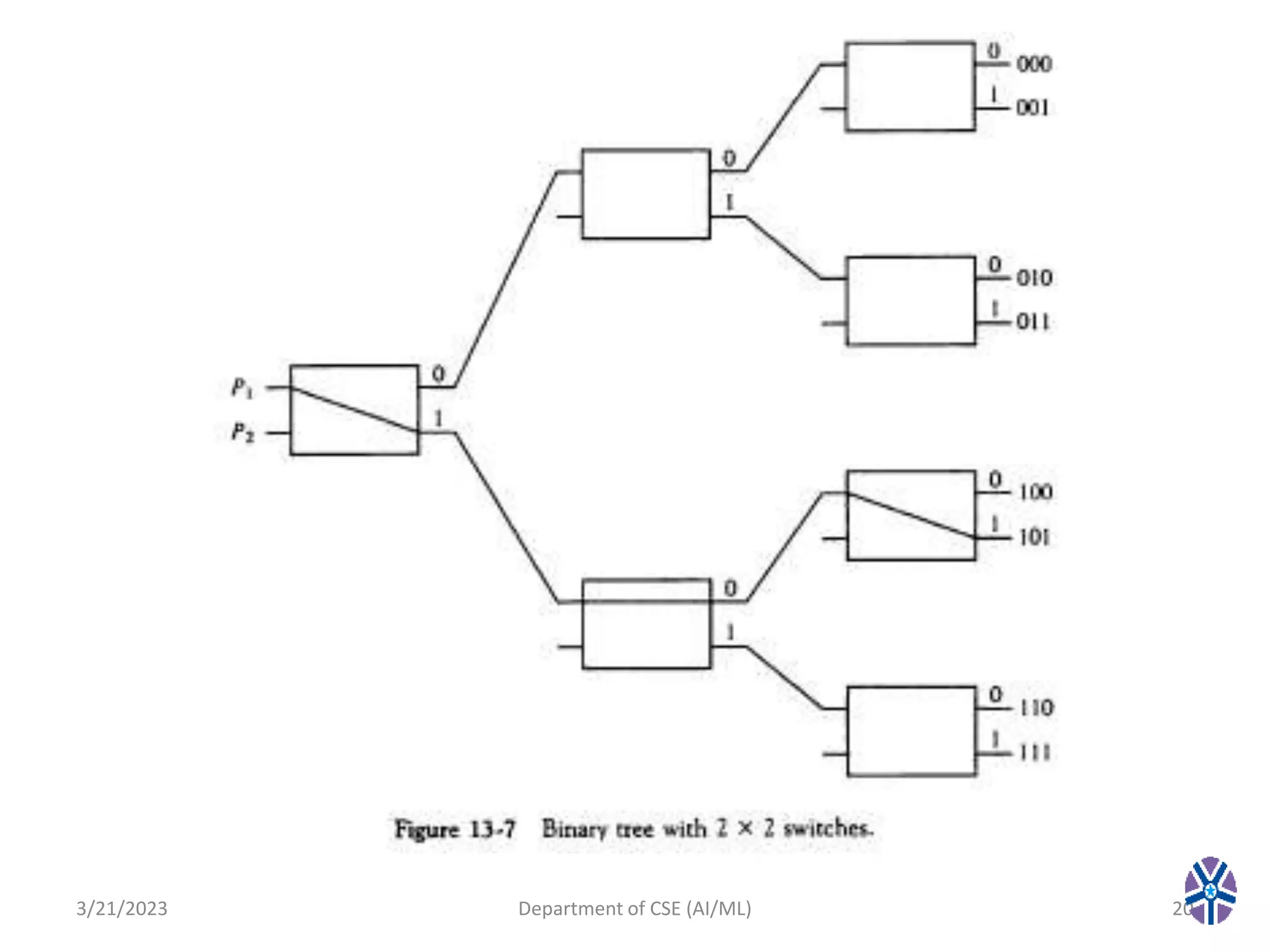

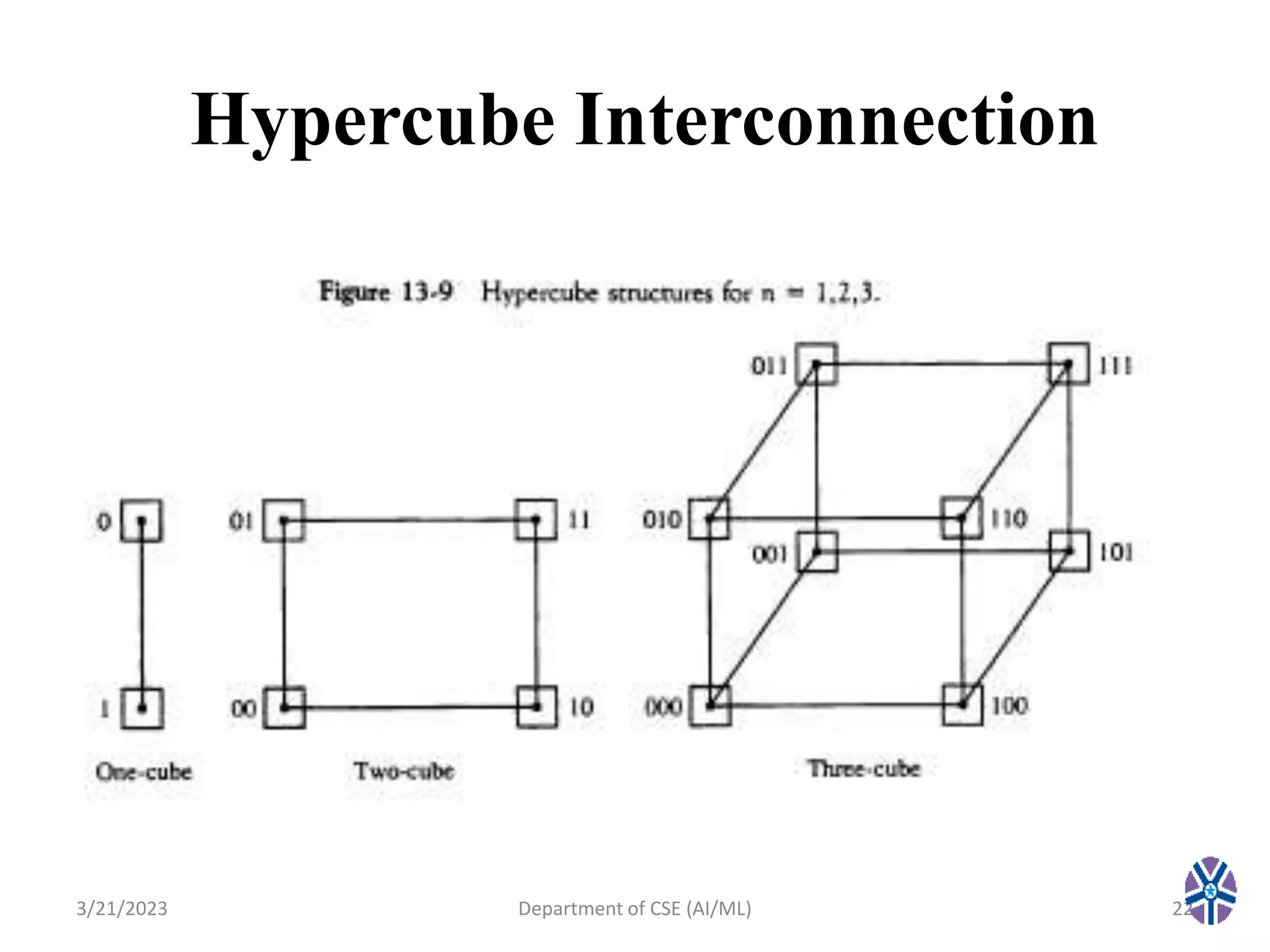

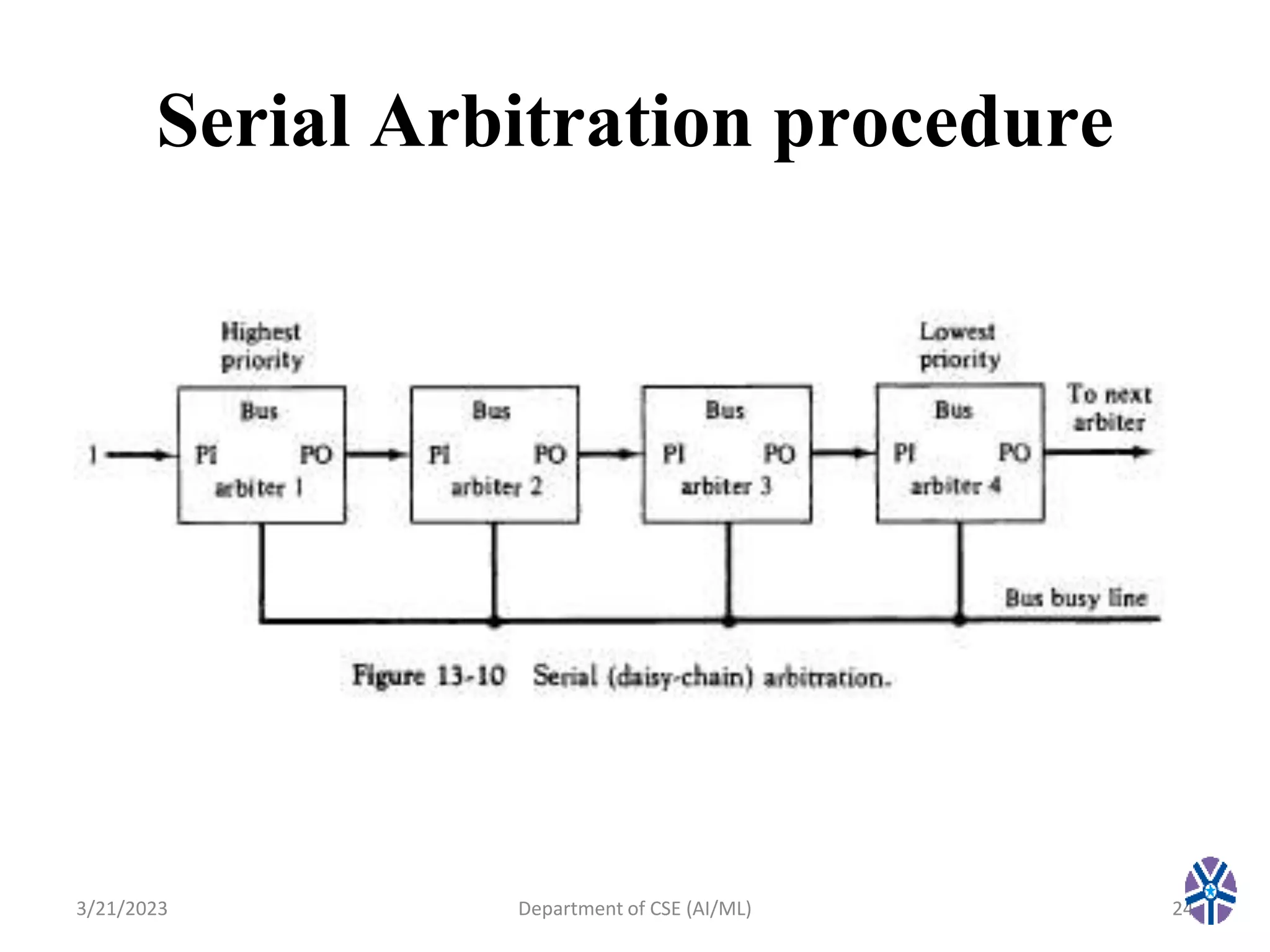

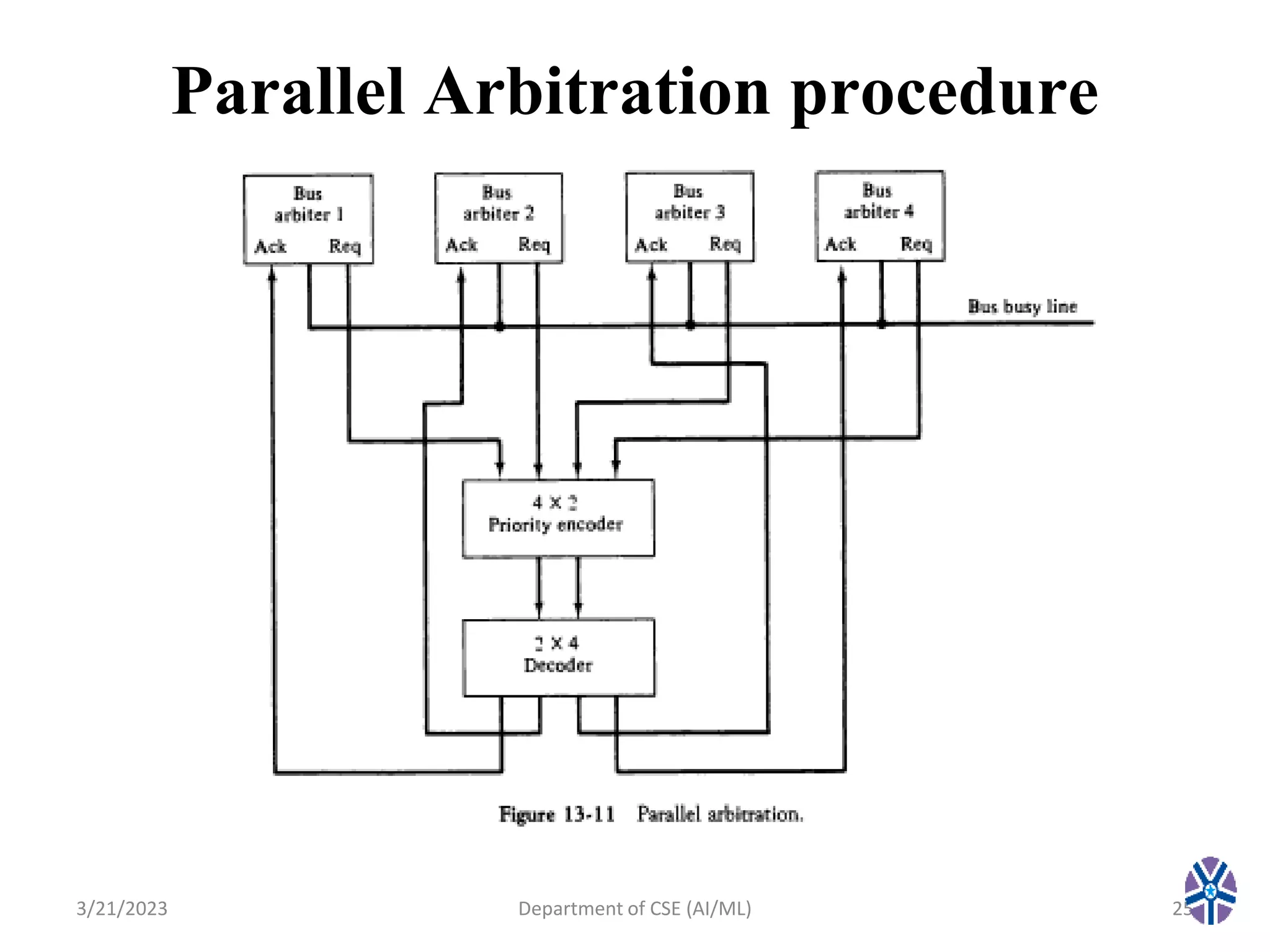

This document contains the summary of a session on multiprocessor systems. It discusses various topics related to multiprocessors including classification of multiprocessors into tightly coupled and loosely coupled systems based on memory organization. It describes different interconnection structures for multiprocessors like shared bus, multiport memory, crossbar switch, multistage switching network and hypercube. It also discusses arbitration techniques for resolving bus conflicts and topics related to interprocessor communication and synchronization that will be covered in the next session.