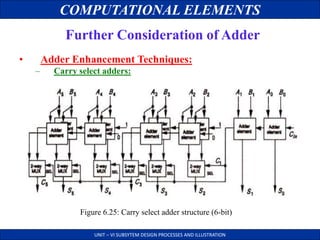

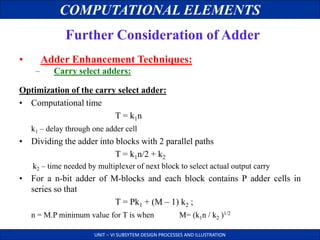

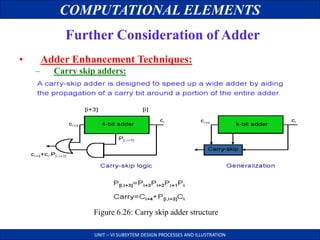

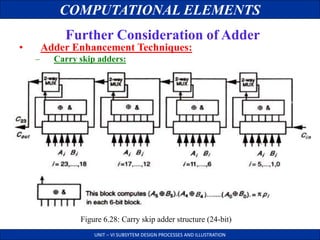

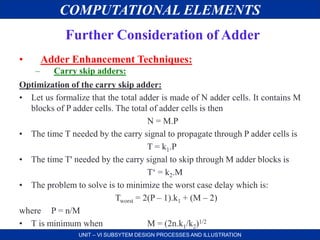

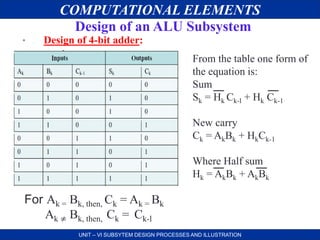

The document discusses the design of an adder subsystem. It describes the design of a 4-bit adder using equations to calculate the sum and carry. It then covers further considerations for adder design including generation and propagation principles. It presents schematics for CMOS adder elements and Manchester carry chains. Finally, it discusses techniques for enhancing adder performance including carry select adders and carry skip adders. Optimization strategies are presented for carry select and carry skip adder structures to minimize delay.

![COMPUTATIONAL ELEMENTS

UNIT – VI SUBSYTEM DESIGN PROCESSES AND ILLUSTRATION

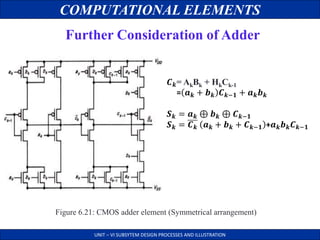

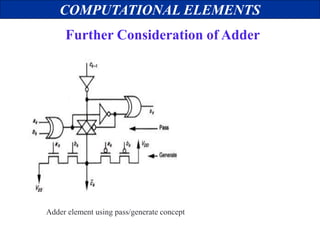

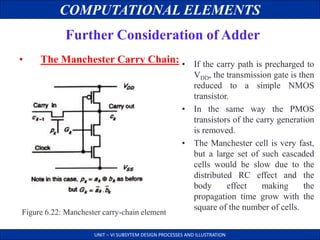

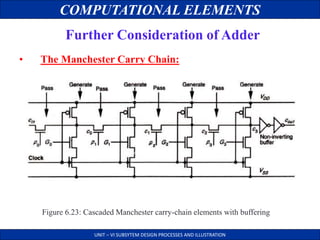

Further Consideration of Adder

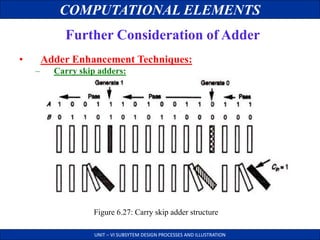

Generation:

• This principle of generation allows the system to take advantage of

the occurrences “Ak=Bk”.

Propagation:

• If we are able to localize a chain of bits Ak Ak+1... Ak+p and Bk Bk+1...

Bk+p for which Ak not equal to Bk for k in [k, k+p], then the output

carry bit of this chain will be equal to the input carry bit of the

chain.

Pk = Ak XOR Bk

Gk = Ak Bk](https://image.slidesharecdn.com/chapter8-nh-160603175520/85/Basic-VLSI-Design-Chapter-8-3-320.jpg)