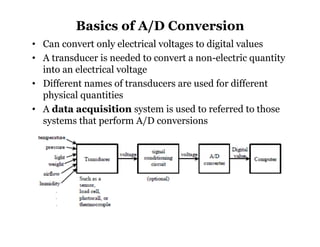

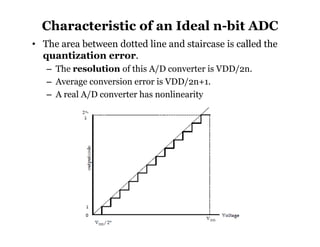

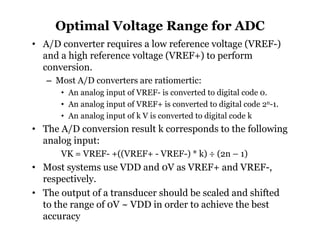

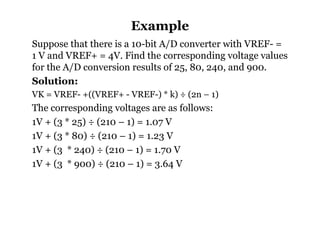

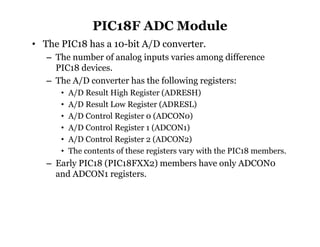

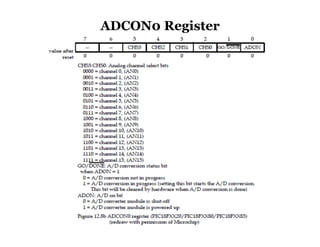

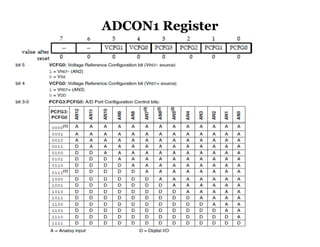

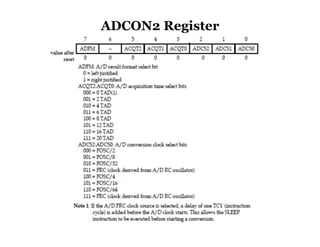

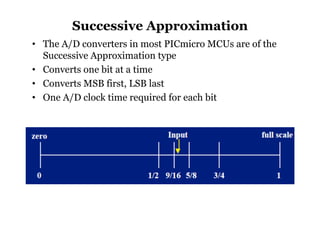

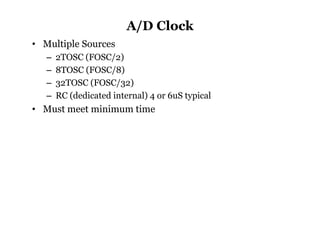

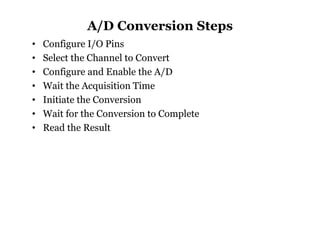

This document discusses analog to digital conversion and interfacing an ADC with a PIC18 microcontroller. It describes the basics of A/D conversion including using transducers to convert non-electric quantities to voltages. It also discusses the characteristics of an ideal ADC and quantization error. The document provides an example of calculating digital codes from analog voltages for a 10-bit ADC. It then describes the registers and conversion process for the A/D converter module in PIC18 microcontrollers.