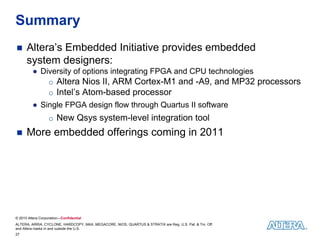

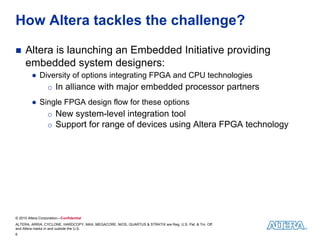

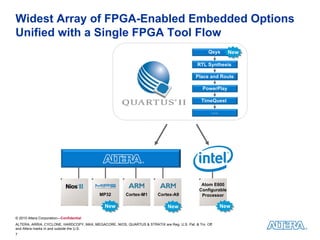

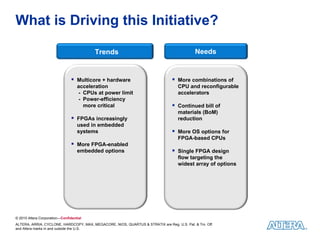

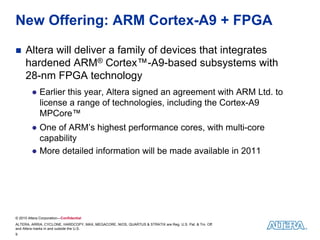

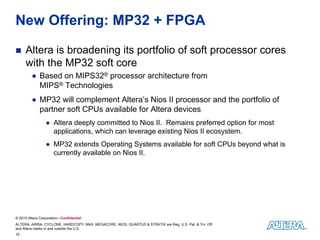

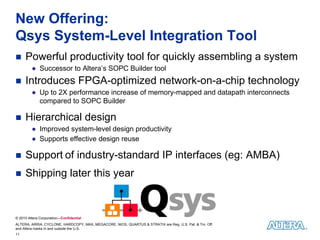

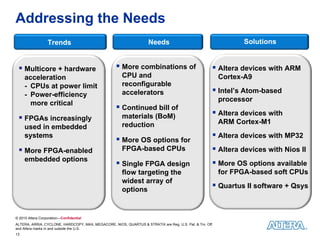

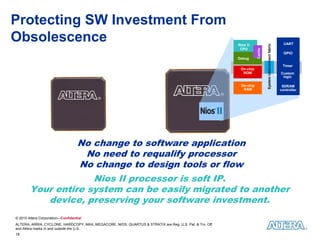

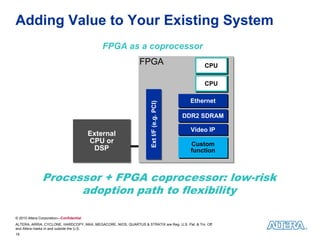

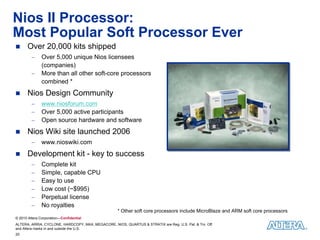

Altera is launching an initiative to help designers more easily create embedded systems using FPGAs. This includes providing a diversity of processor core options that can be integrated with FPGAs, along with a single design flow. Altera will offer devices containing ARM Cortex-A9 and Cortex-M1 processors, an MP32 processor, and will continue to support Nios II processors. A new system integration tool called Qsys will provide a simplified way to assemble full systems. This will help address challenges around cost reduction, flexibility, and power efficiency for embedded system design.

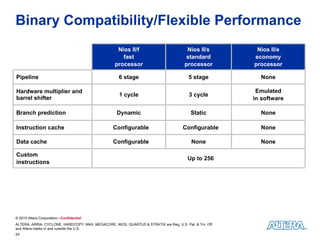

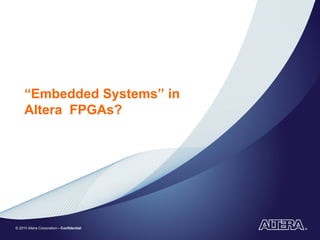

![Nios II Processor

Nios II processor core

reset

General

Instruction and

Instruction and

clock Program purpose Instruction

data trace

controller

data trace

JTAG interface registers Instruction master

Hardware- and cache

to software port

assisted address

debugger debug module generation Status and

control

registers Tightly

Tightly

High-speed Trace coupled

connection Trace port Trace coupled

Trace port memory I-memory

to trace pod memory I-memory

breakpoints

breakpoints

MMU

Exception Tightly

Tightly

HW

coupled

HW

controller coupled

D-memory

D-memory

Interrupt MPU

irq[31..0] controller

Data

Data master

Custom cache

Custom instruction Arithmetic port

I/O signals logic logic unit

= Optional = Configurable

= Fixed = Debug Options

© 2010 Altera Corporation—Confidential

ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U.S. Pat. & Tm. Off.

and Altera marks in and outside the U.S.

23](https://image.slidesharecdn.com/ourdev598703tpwcm7-101208070746-phpapp02/85/Ourdev-598703-tpwcm7-23-320.jpg)