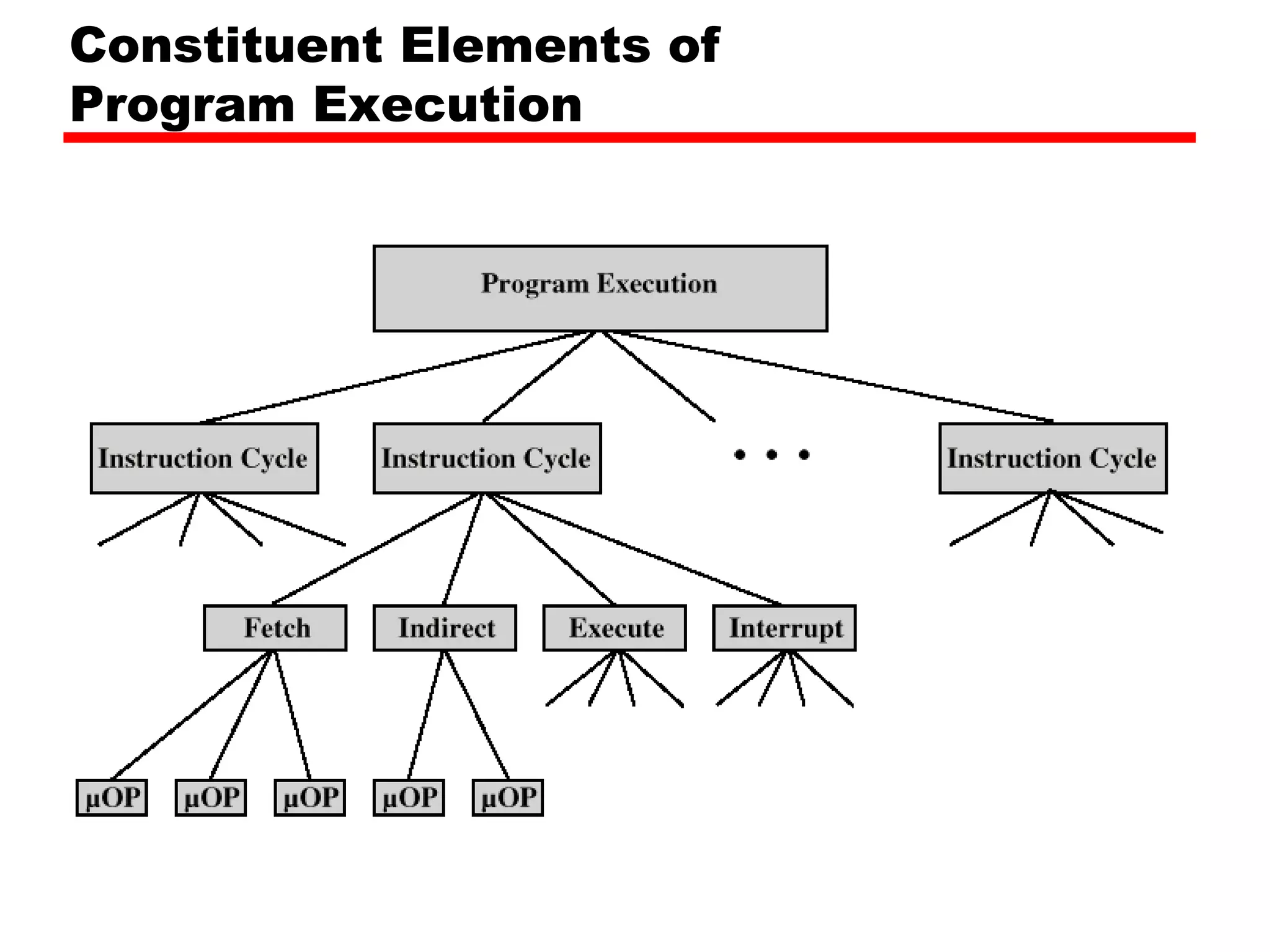

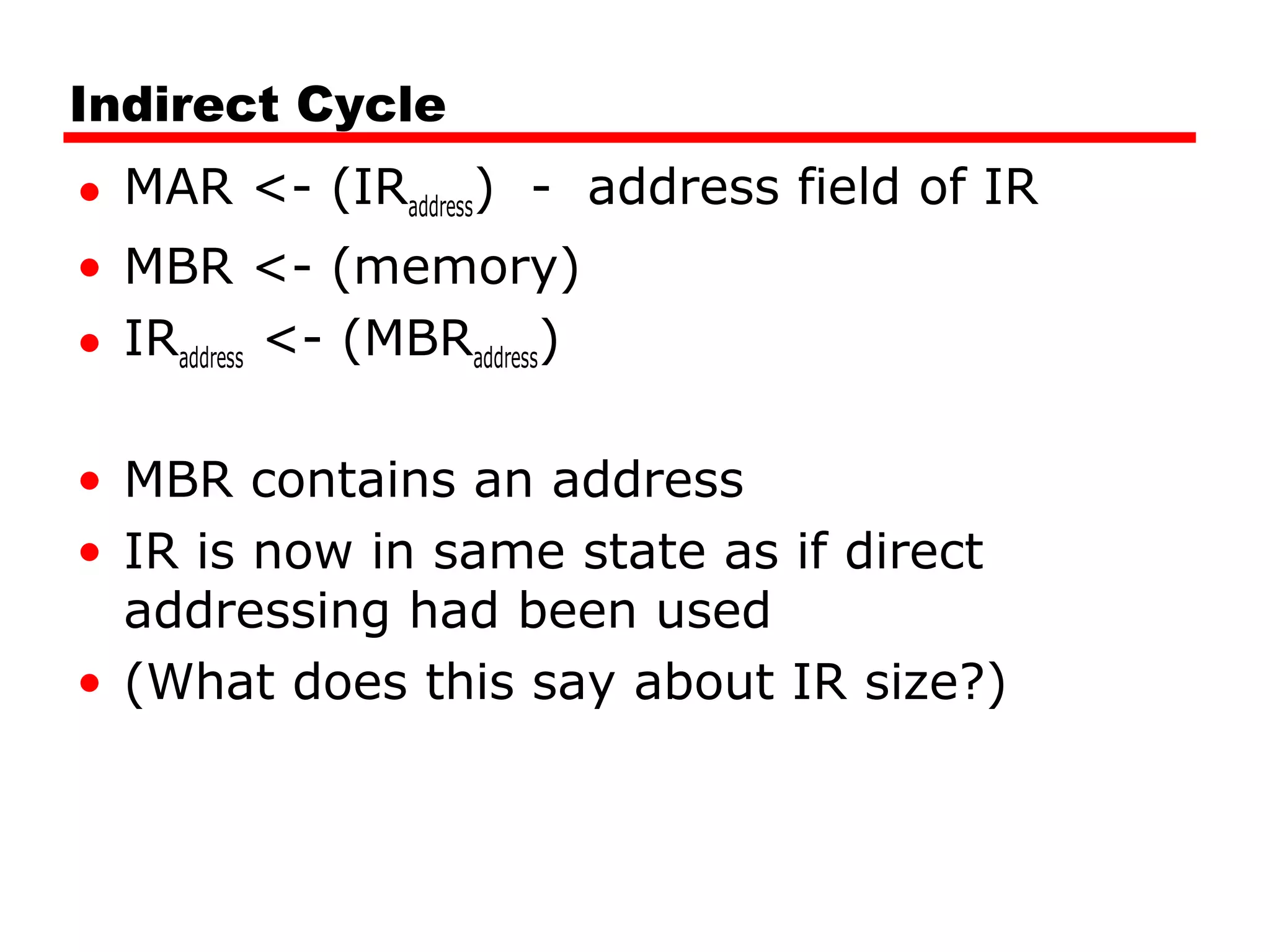

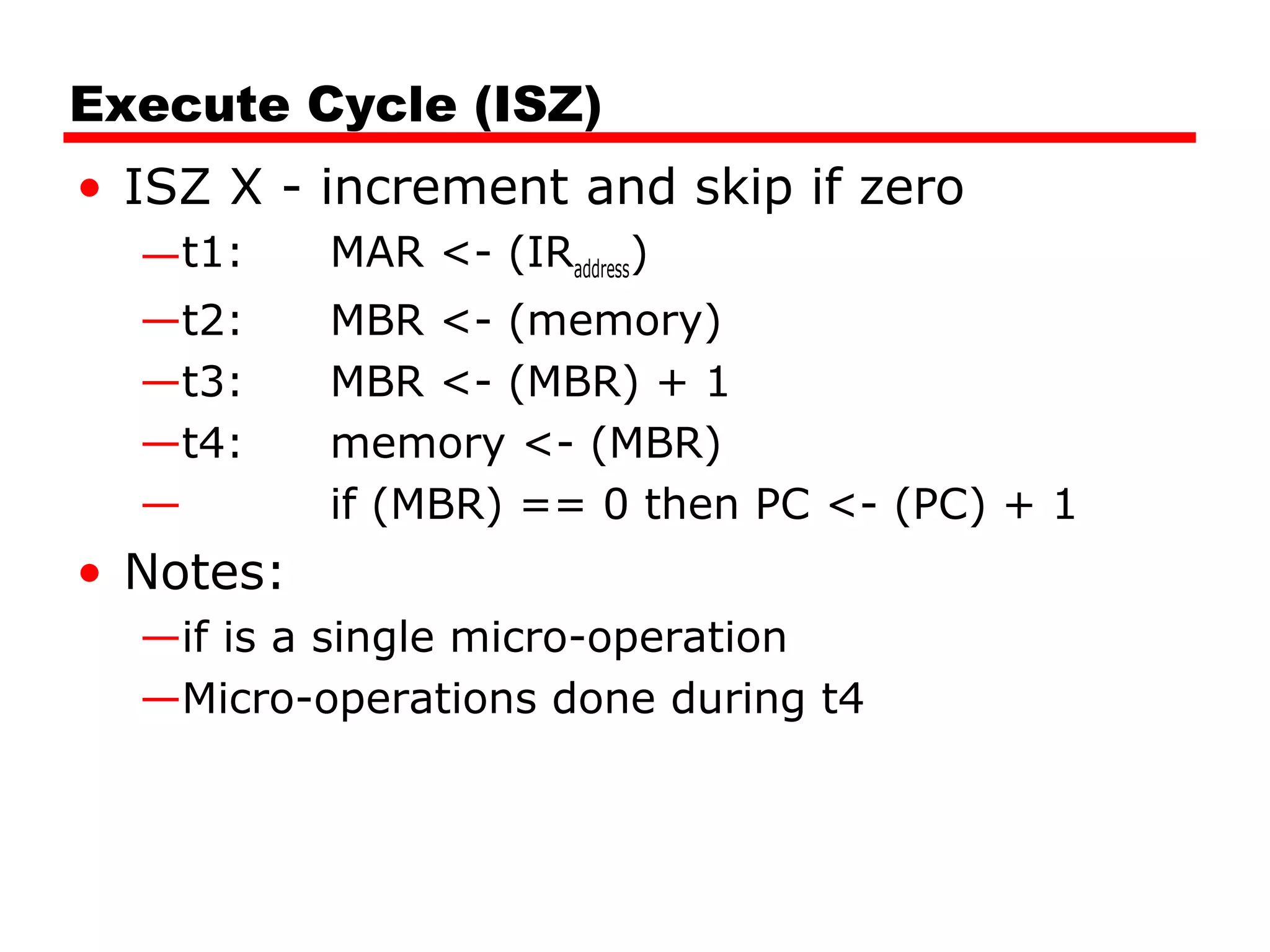

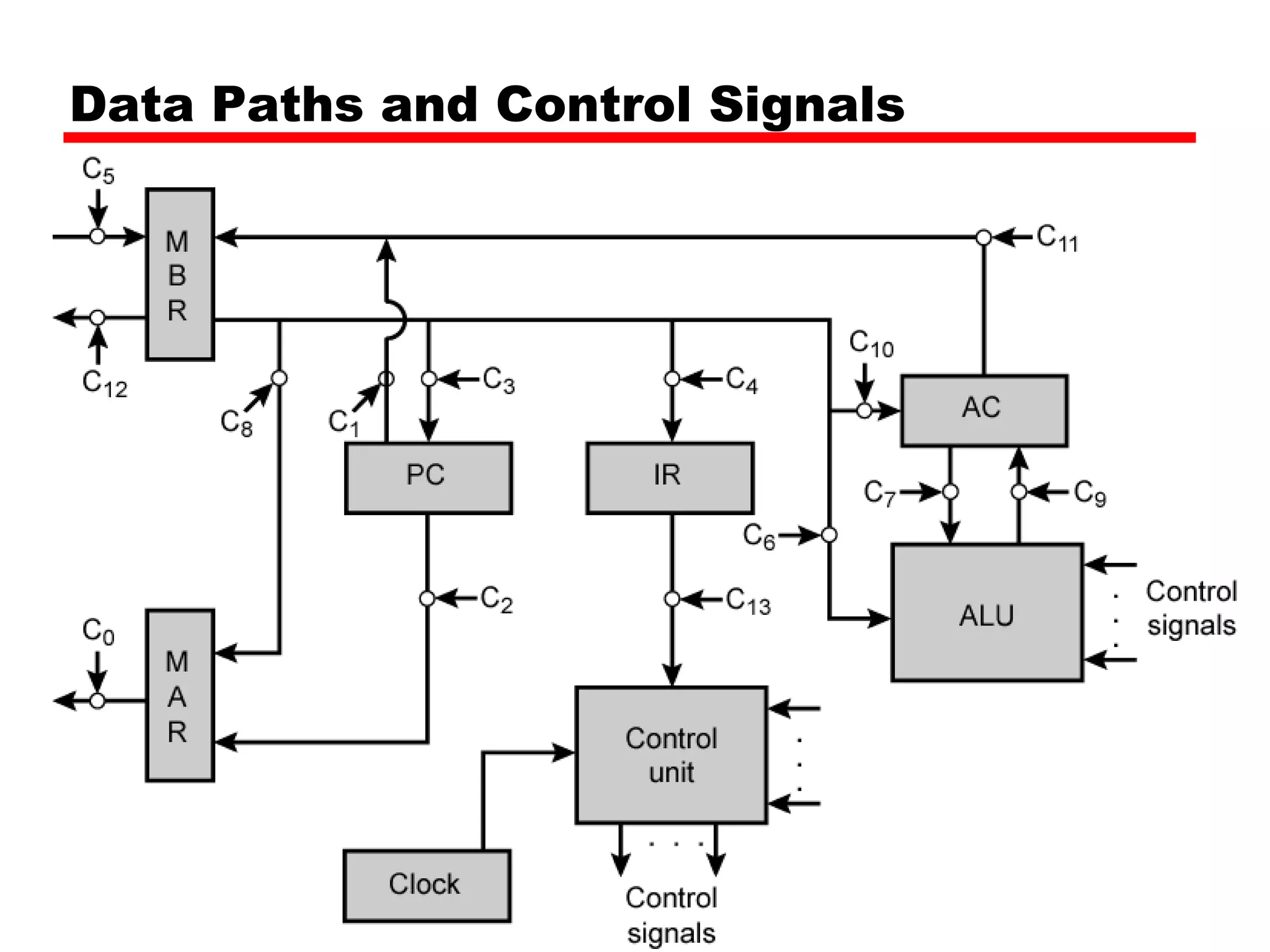

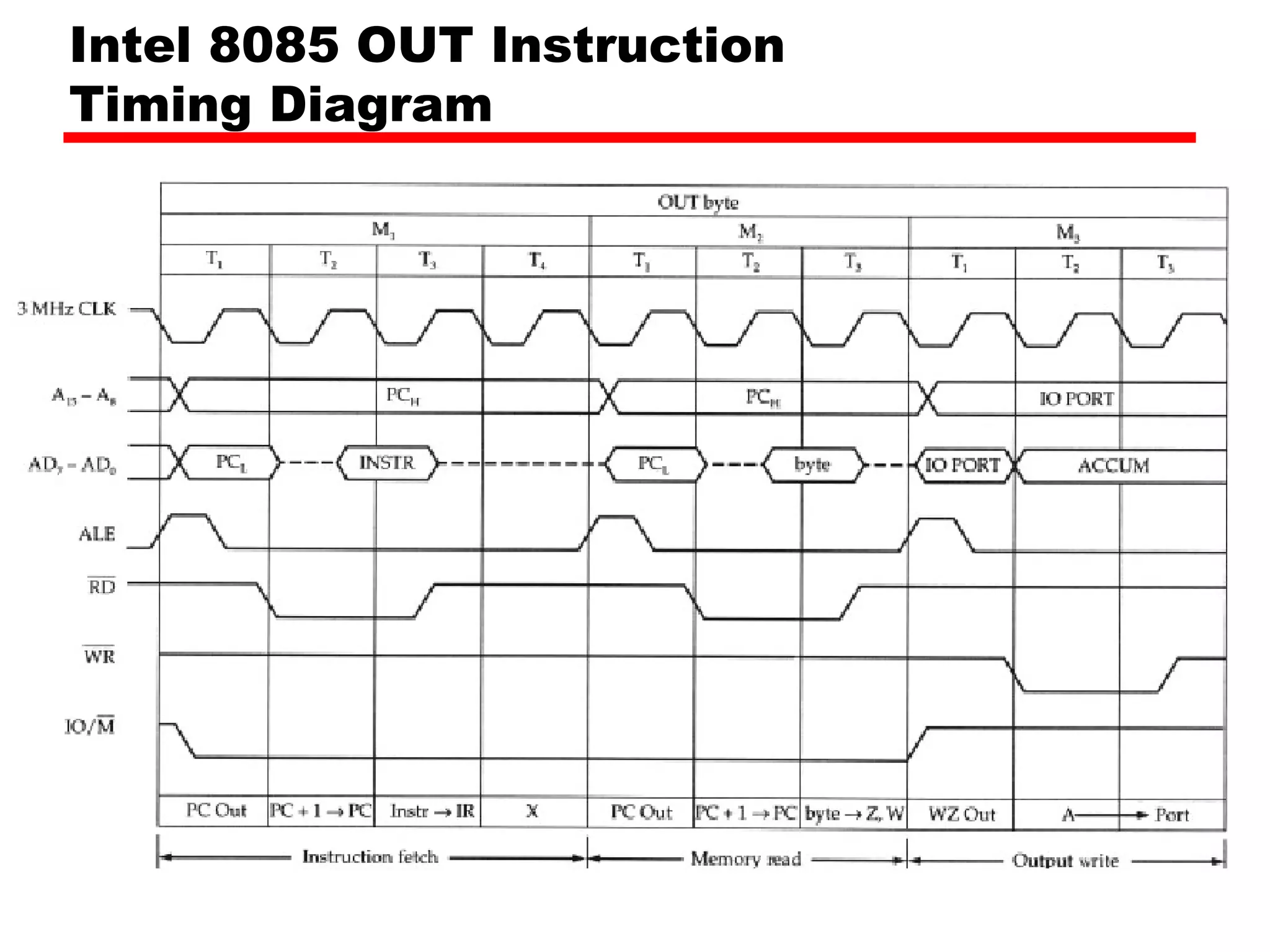

This document summarizes key aspects of control unit operation from William Stallings' Computer Organization and Architecture textbook. It discusses micro-operations which are the basic steps that make up each instruction fetch/execute cycle. The constituent elements involved in program execution like registers are described. The sequences of steps in the fetch, indirect, and interrupt cycles are outlined. Examples of the execute cycle for different instructions like ADD and ISZ are provided. The functional requirements, basic elements, and types of micro-operations that a control unit must perform are identified. Models of the control unit and how it generates control signals to orchestrate data movement and activation of functions are described.