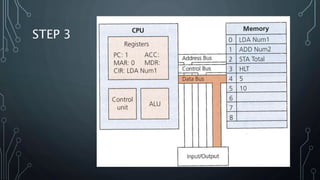

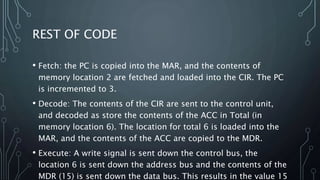

The document describes the fetch-decode-execute (FDE) cycle of a processor. It explains the main components of the processor including registers, arithmetic logic unit (ALU), control unit, and buses. It then walks through the steps of the FDE cycle, which includes fetching an instruction from memory, decoding it, and executing the operation. First, the program counter addresses the instruction and it is stored in the instruction register. Then it is decoded and the appropriate operation is performed using data from memory or registers. This cycle is then repeated for each subsequent instruction.