binary decrementer.pdf

•

0 likes•161 views

Computer operations and architecture

Report

Share

Report

Share

Download to read offline

More Related Content

What's hot

What's hot (20)

Image Interpolation Techniques with Optical and Digital Zoom Concepts

Image Interpolation Techniques with Optical and Digital Zoom Concepts

B. SC CSIT Computer Graphics Unit 2 By Tekendra Nath Yogi

B. SC CSIT Computer Graphics Unit 2 By Tekendra Nath Yogi

Similar to binary decrementer.pdf

Similar to binary decrementer.pdf (20)

Adder & subtractor (Half adder, Full adder, Half subtractor, Full subtractor)

Adder & subtractor (Half adder, Full adder, Half subtractor, Full subtractor)

Implementation and Simulation of Ieee 754 Single-Precision Floating Point Mul...

Implementation and Simulation of Ieee 754 Single-Precision Floating Point Mul...

DLD Lecture No 20 Look Ahead Carry Generator, Binary Subtractors and BCD Add...

DLD Lecture No 20 Look Ahead Carry Generator, Binary Subtractors and BCD Add...

Comparison of Adders for optimized Exponent Addition circuit in IEEE754 Float...

Comparison of Adders for optimized Exponent Addition circuit in IEEE754 Float...

Cse lecture-4.2-c bit wise operators and expression

Cse lecture-4.2-c bit wise operators and expression

CDS Fundamentals of digital communication system UNIT 1 AND 2.pdf

CDS Fundamentals of digital communication system UNIT 1 AND 2.pdf

Recently uploaded

Recently uploaded (20)

Theory of Time 2024 (Universal Theory for Everything)

Theory of Time 2024 (Universal Theory for Everything)

Developing a smart system for infant incubators using the internet of things ...

Developing a smart system for infant incubators using the internet of things ...

Tembisa Central Terminating Pills +27838792658 PHOMOLONG Top Abortion Pills F...

Tembisa Central Terminating Pills +27838792658 PHOMOLONG Top Abortion Pills F...

21scheme vtu syllabus of visveraya technological university

21scheme vtu syllabus of visveraya technological university

5G and 6G refer to generations of mobile network technology, each representin...

5G and 6G refer to generations of mobile network technology, each representin...

Independent Solar-Powered Electric Vehicle Charging Station

Independent Solar-Powered Electric Vehicle Charging Station

8th International Conference on Soft Computing, Mathematics and Control (SMC ...

8th International Conference on Soft Computing, Mathematics and Control (SMC ...

UNIT-2 image enhancement.pdf Image Processing Unit 2 AKTU

UNIT-2 image enhancement.pdf Image Processing Unit 2 AKTU

Filters for Electromagnetic Compatibility Applications

Filters for Electromagnetic Compatibility Applications

Instruct Nirmaana 24-Smart and Lean Construction Through Technology.pdf

Instruct Nirmaana 24-Smart and Lean Construction Through Technology.pdf

Interfacing Analog to Digital Data Converters ee3404.pdf

Interfacing Analog to Digital Data Converters ee3404.pdf

binary decrementer.pdf

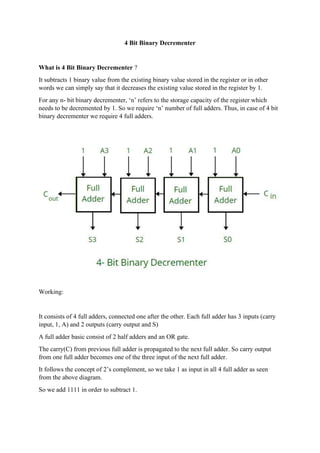

- 1. 4 Bit Binary Decrementer What is 4 Bit Binary Decrementer ? It subtracts 1 binary value from the existing binary value stored in the register or in other words we can simply say that it decreases the existing value stored in the register by 1. For any n- bit binary decrementer, ‘n’ refers to the storage capacity of the register which needs to be decremented by 1. So we require ‘n’ number of full adders. Thus, in case of 4 bit binary decrementer we require 4 full adders. Working: It consists of 4 full adders, connected one after the other. Each full adder has 3 inputs (carry input, 1, A) and 2 outputs (carry output and S) A full adder basic consist of 2 half adders and an OR gate. The carry(C) from previous full adder is propagated to the next full adder. So carry output from one full adder becomes one of the three input of the next full adder. It follows the concept of 2’s complement, so we take 1 as input in all 4 full adder as seen from the above diagram. So we add 1111 in order to subtract 1.

- 2. Reason for adding 1111: This is because our main motive is to subtract 1 which in 4 bit representation is 0001 Representing it in 1’s complement will give: 1110 Representing it in 2’s complement (adding 1 to 1’s complement) will give: 1111 This is the reason why input 1111 is given to get a decremented output in 4 bit binary decrementer.