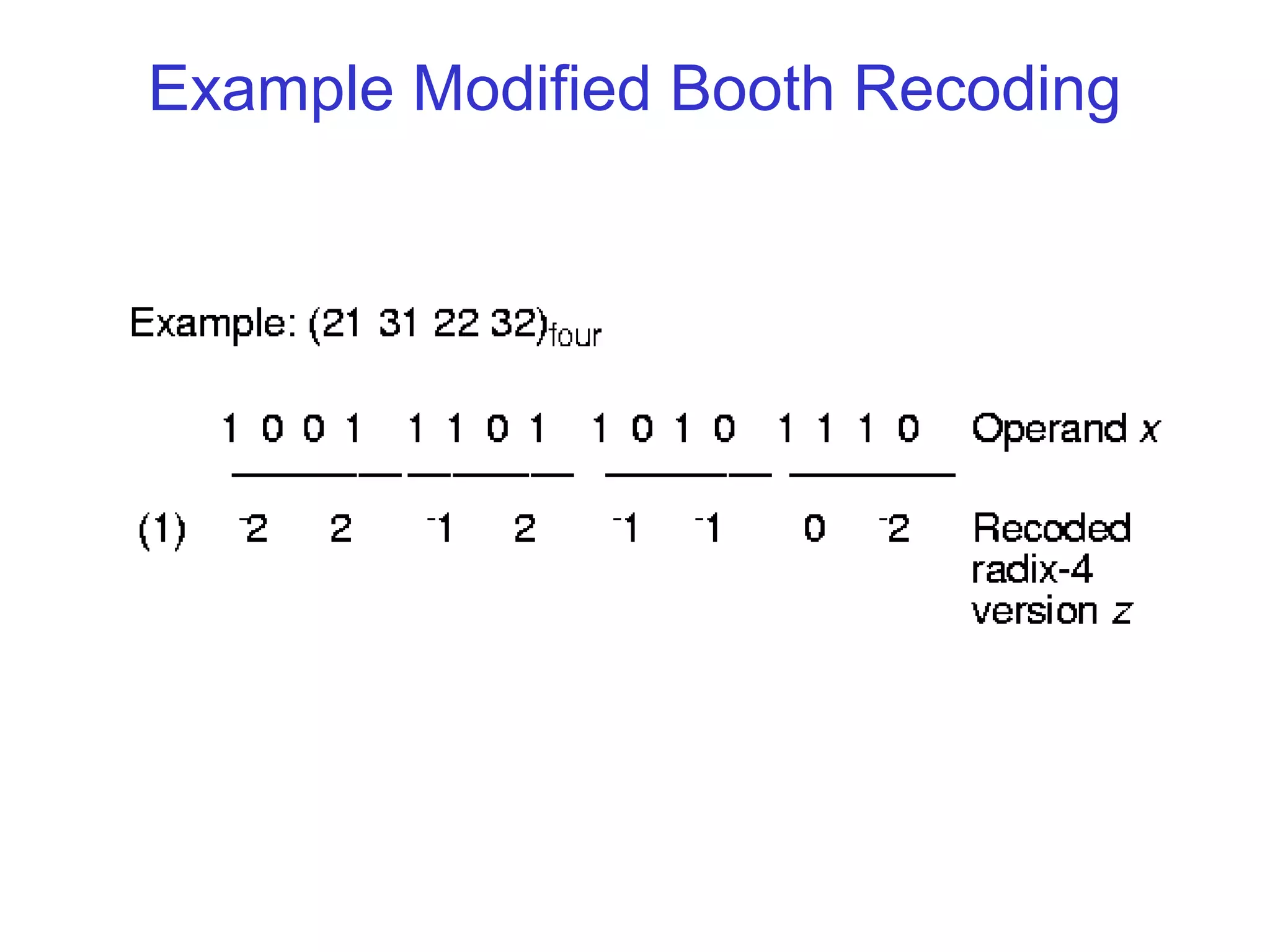

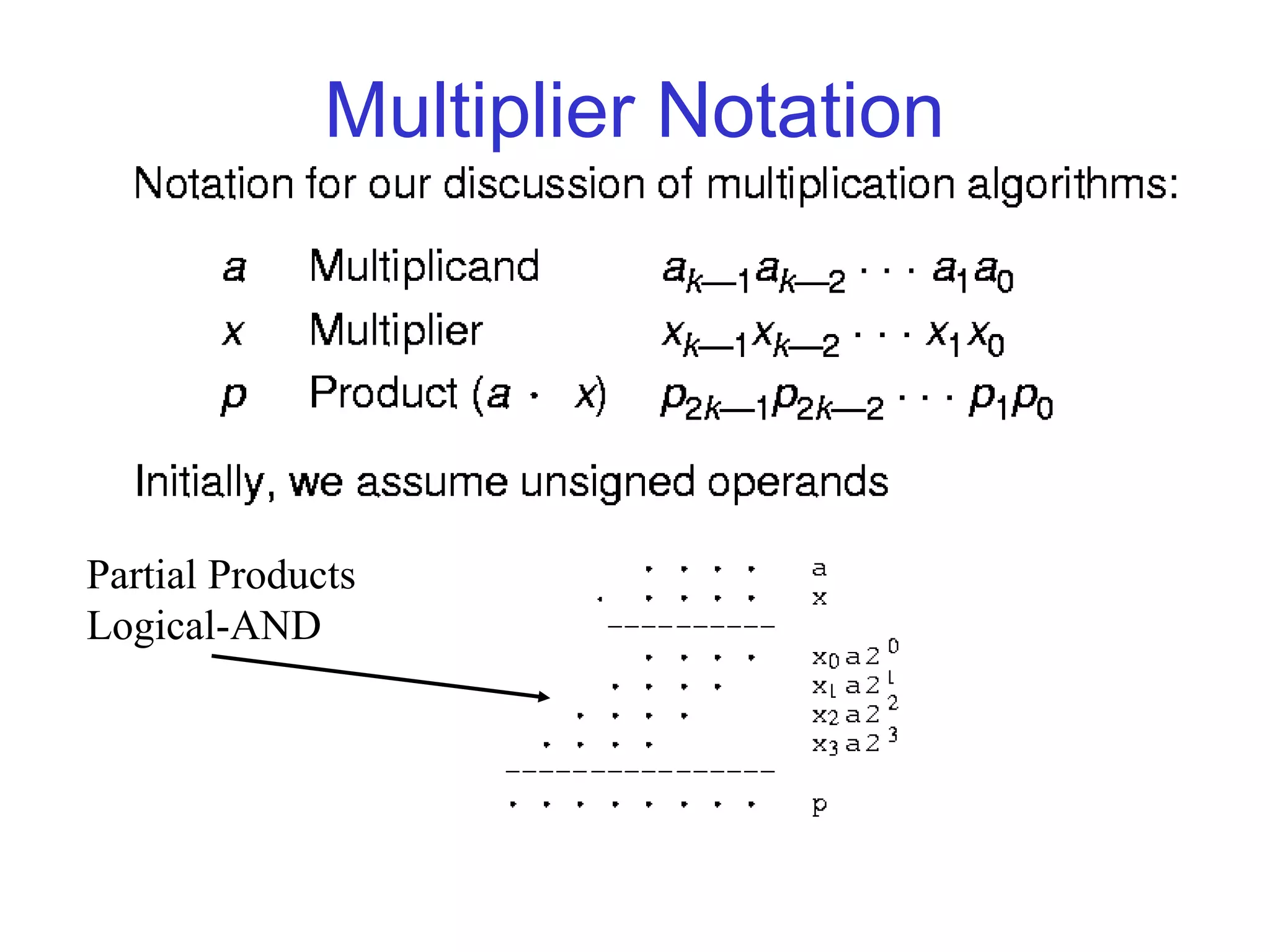

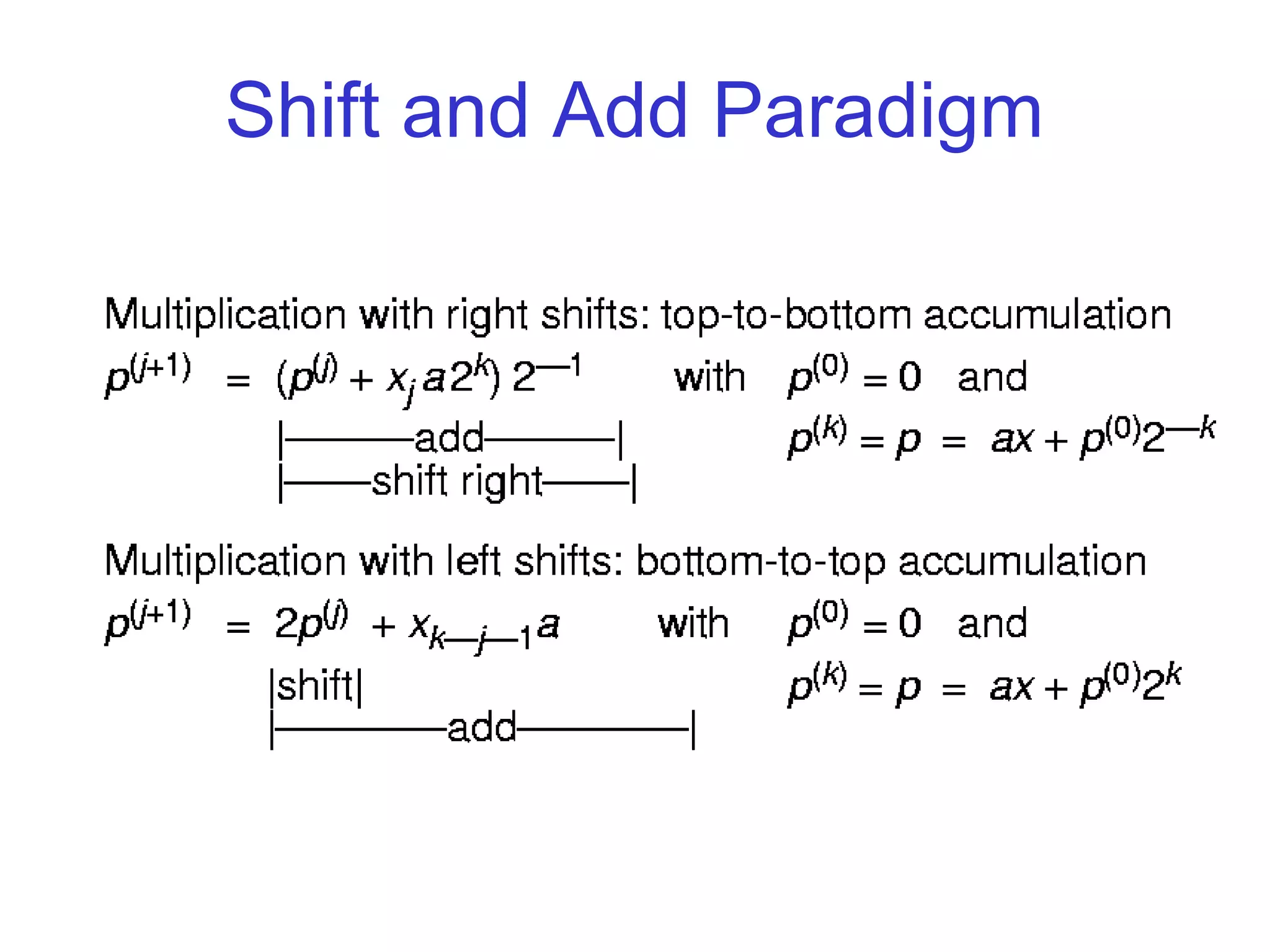

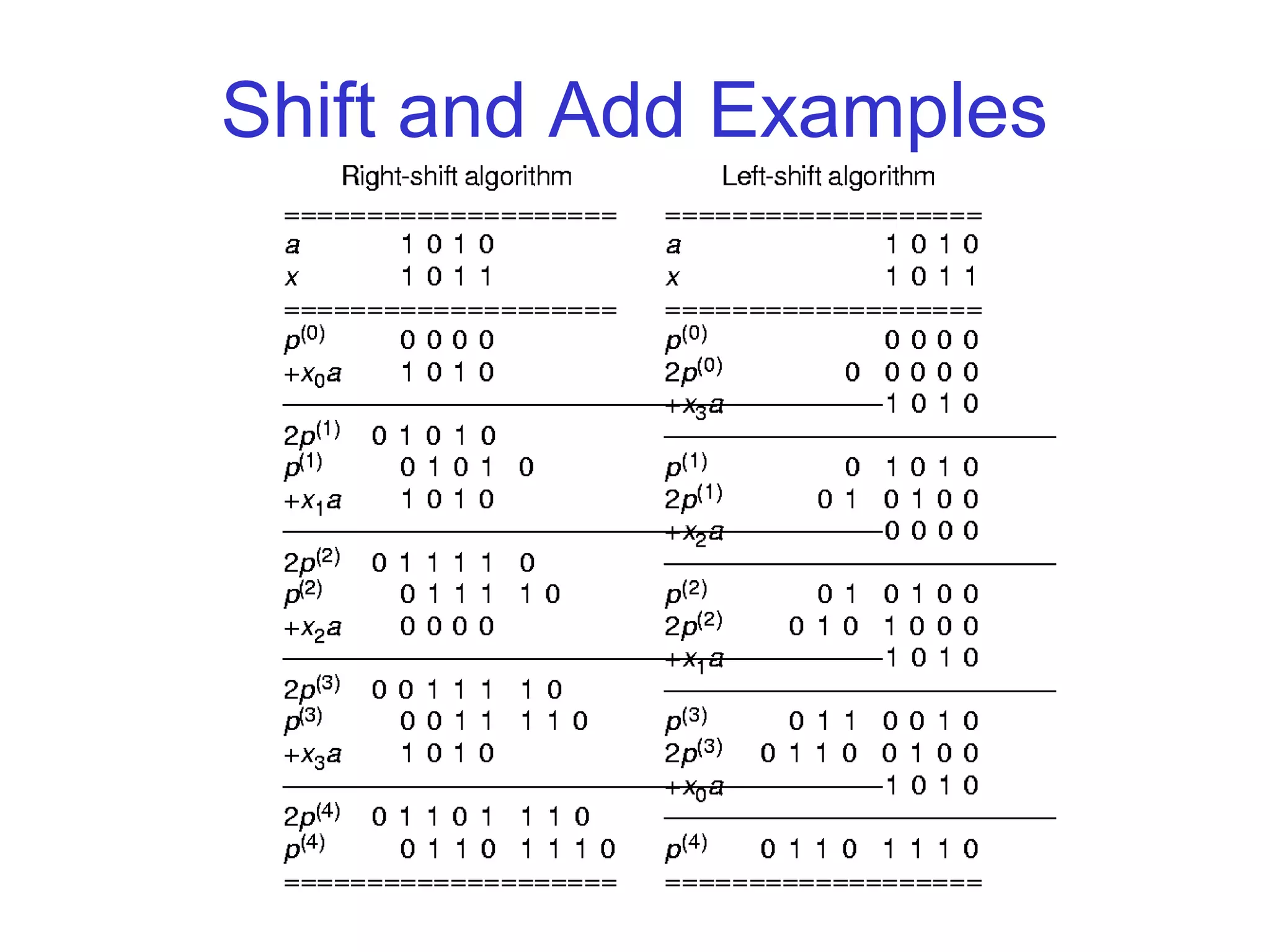

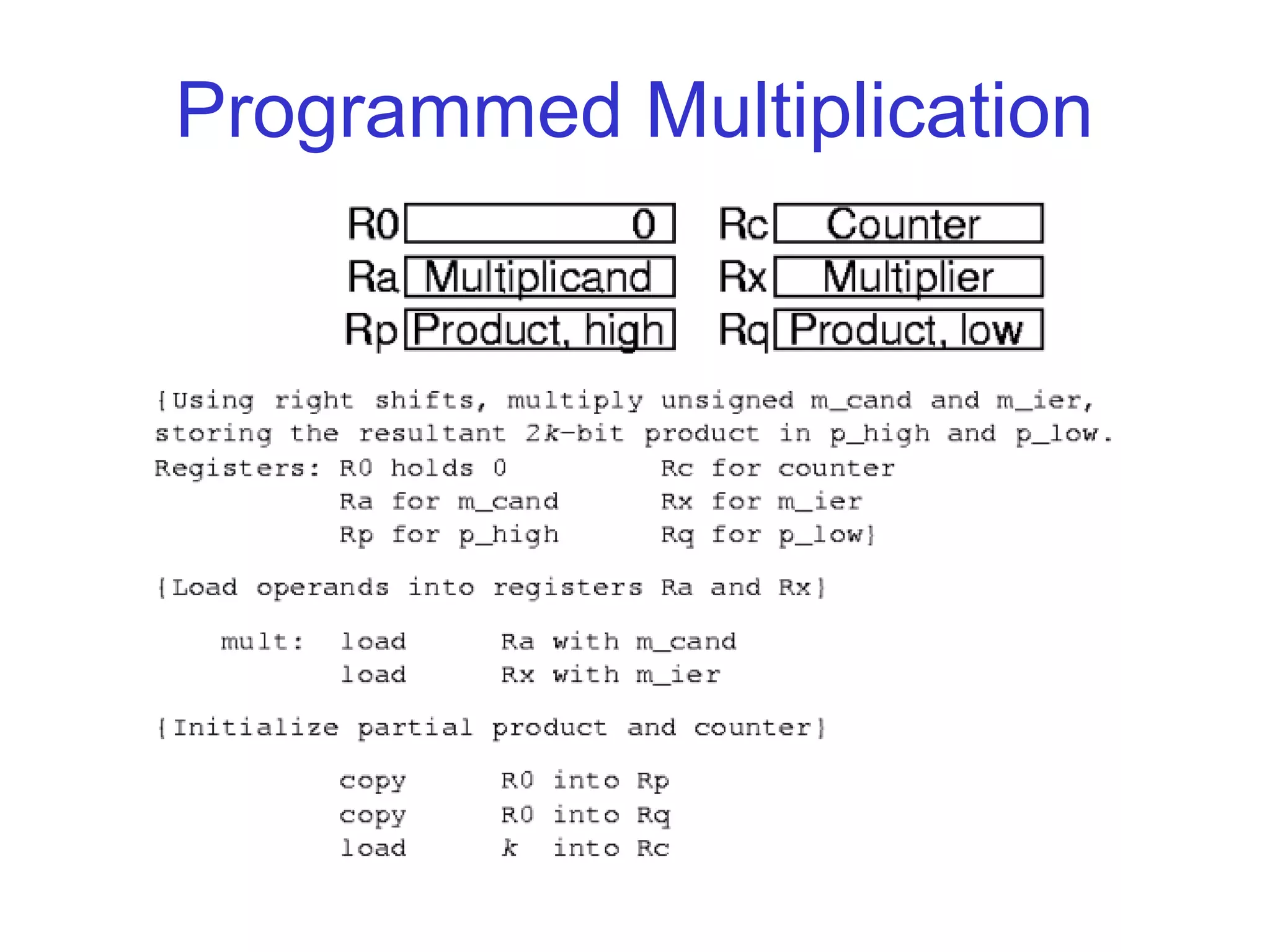

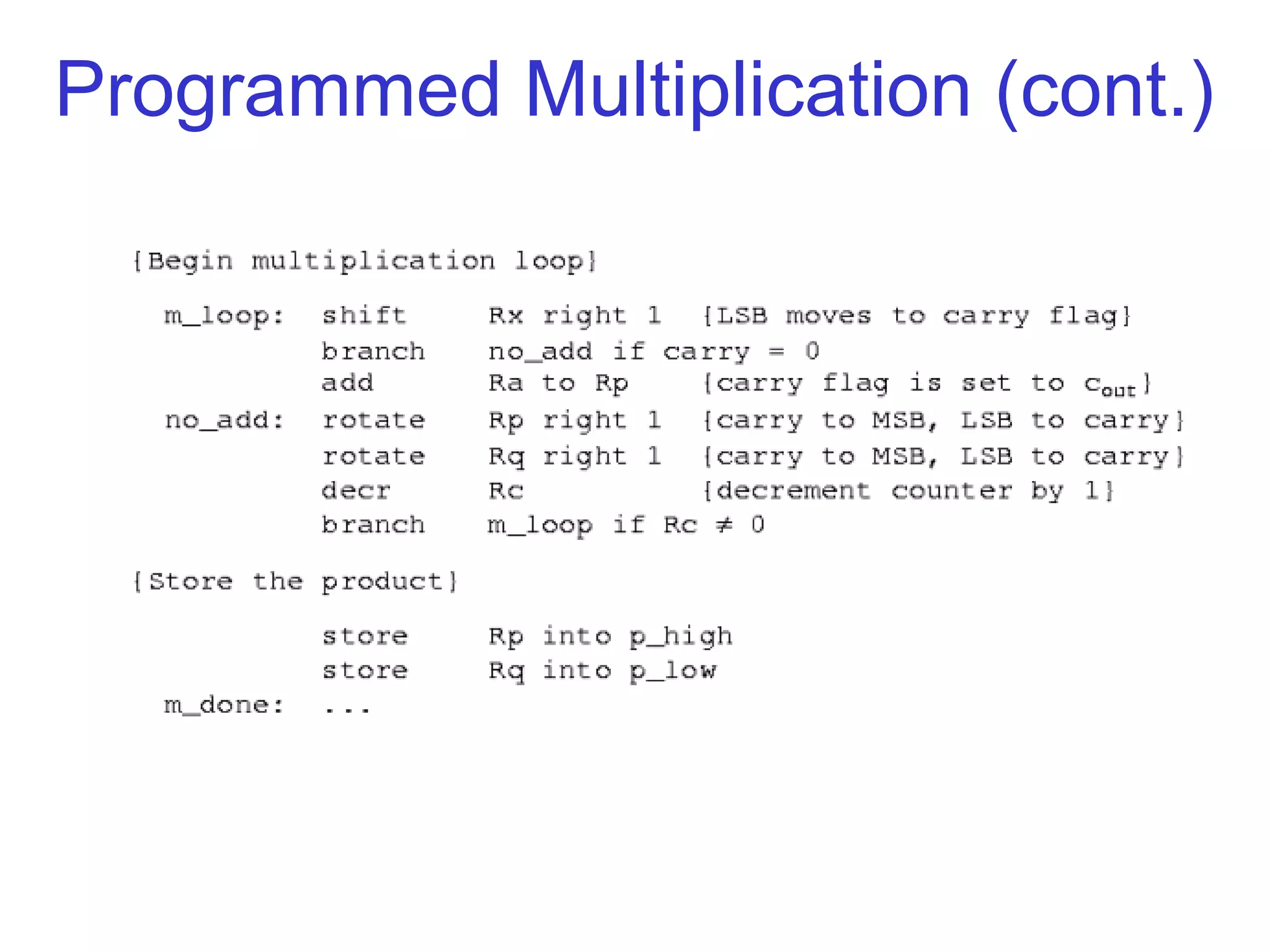

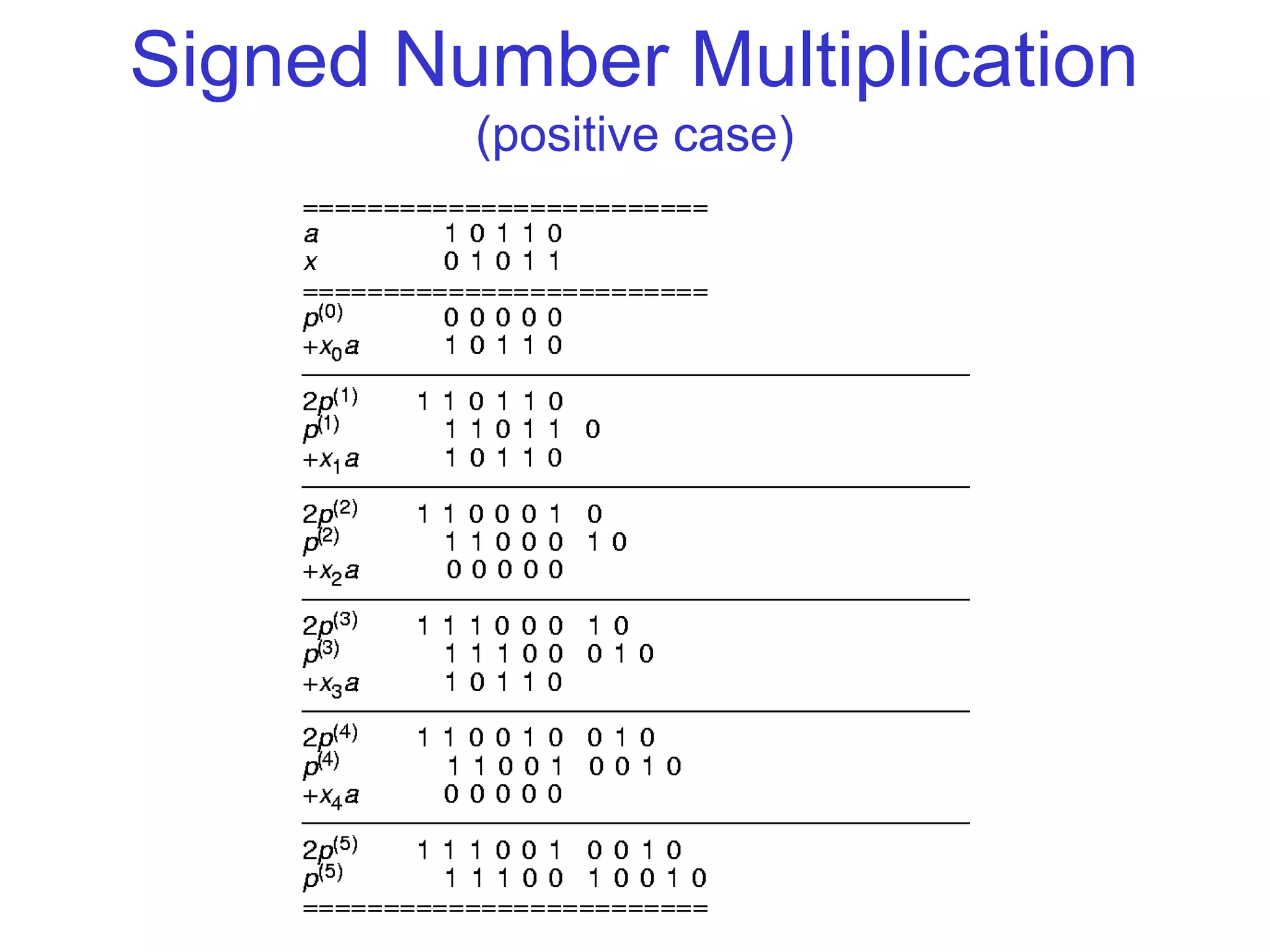

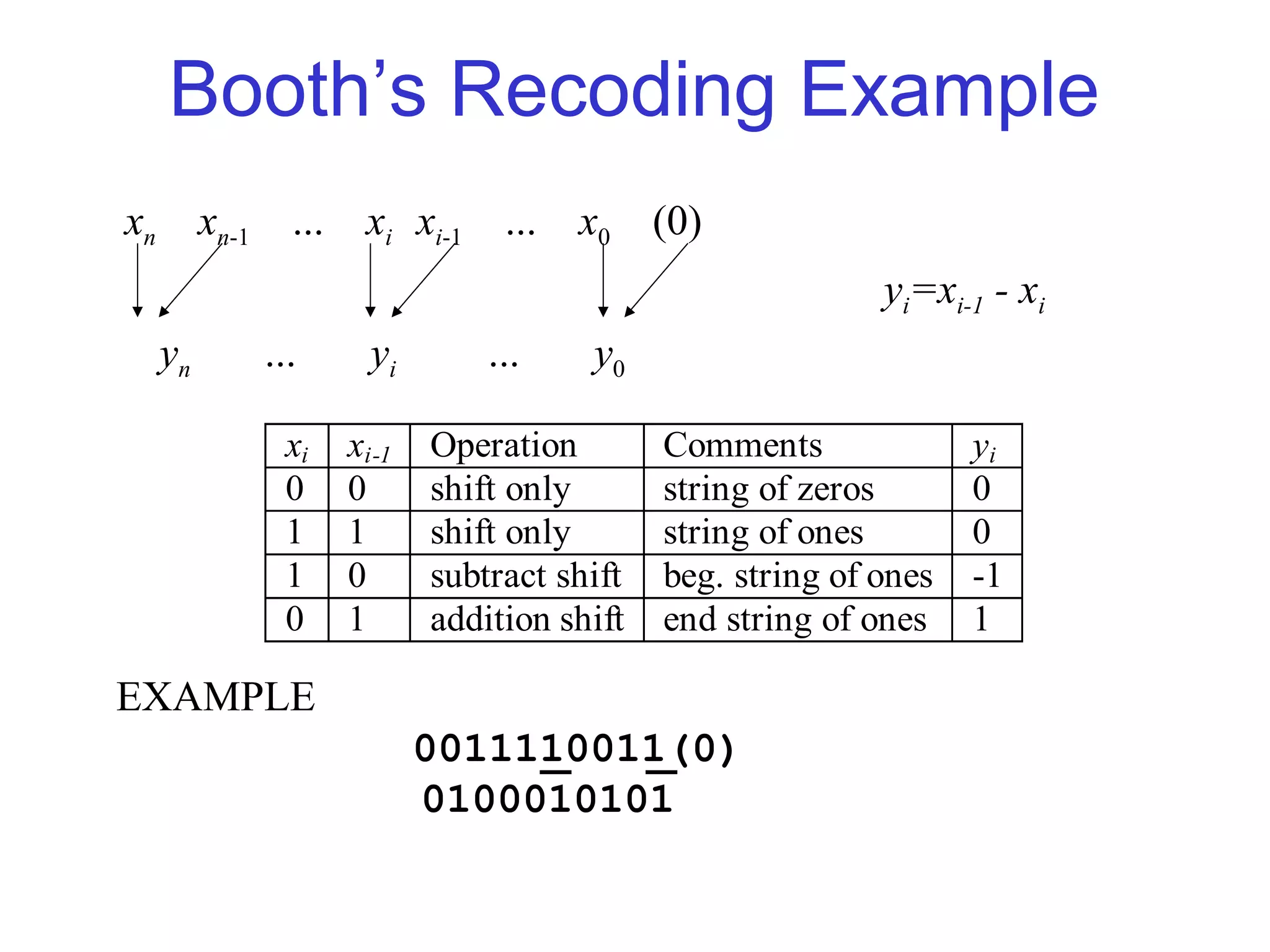

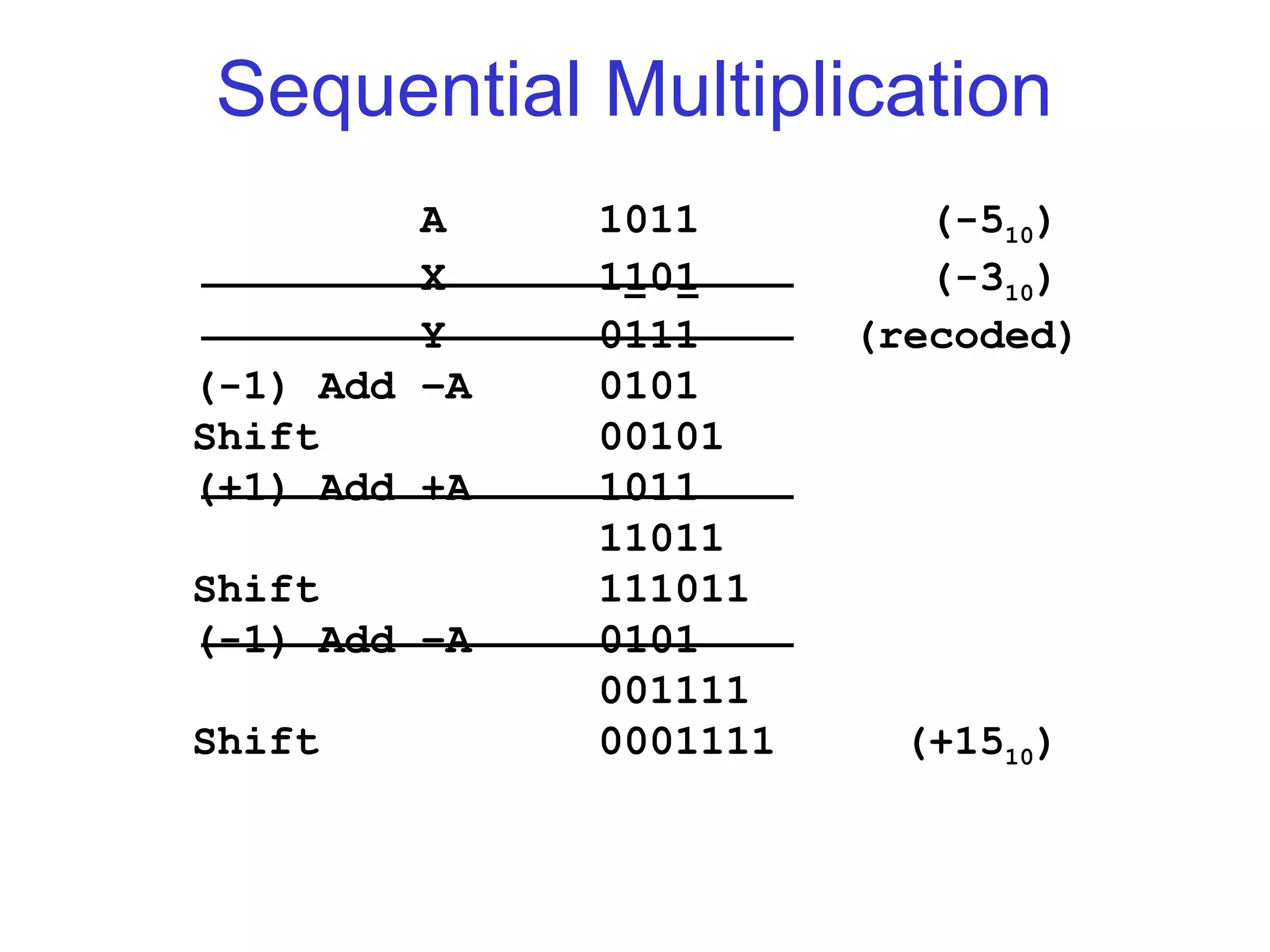

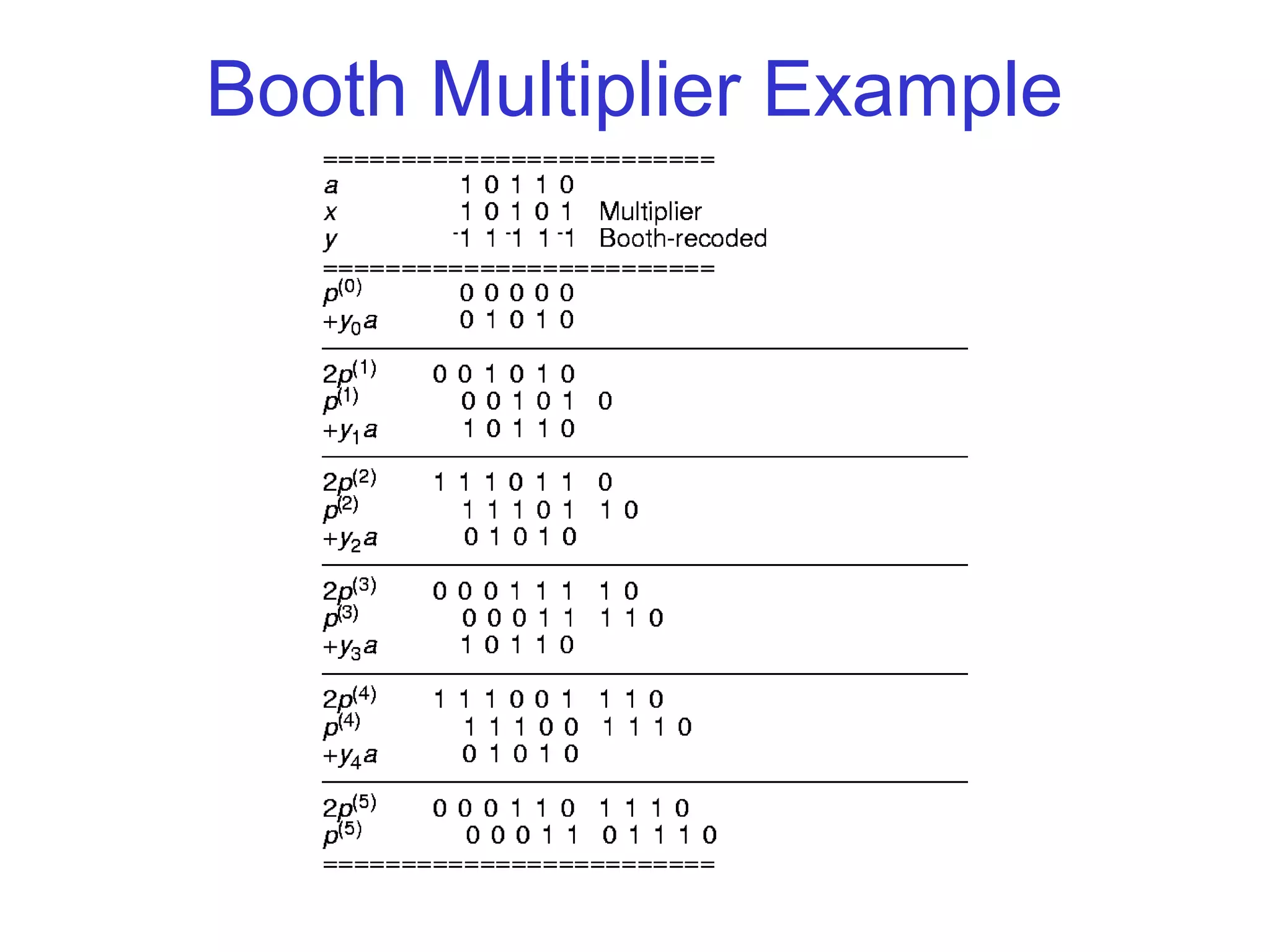

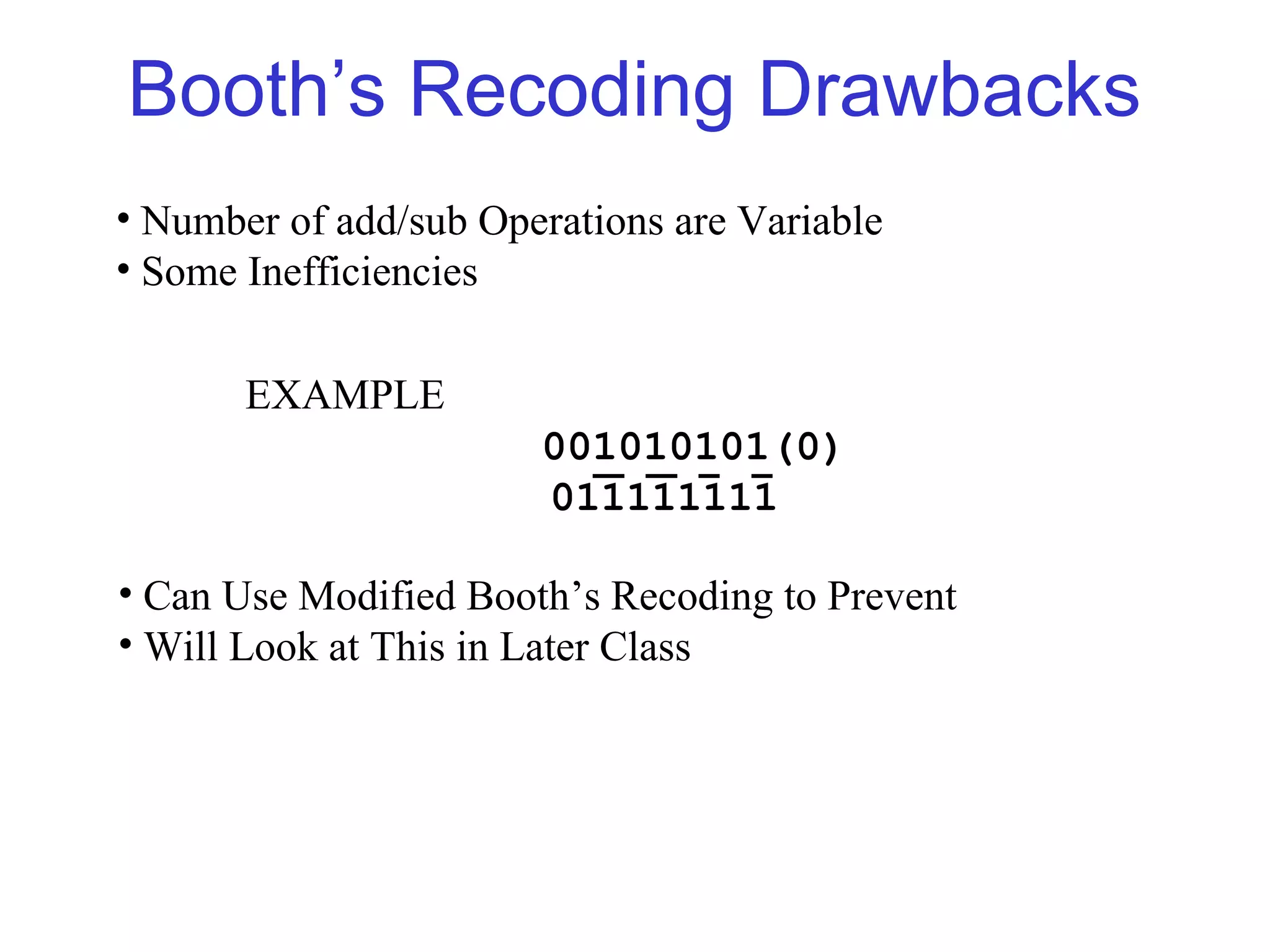

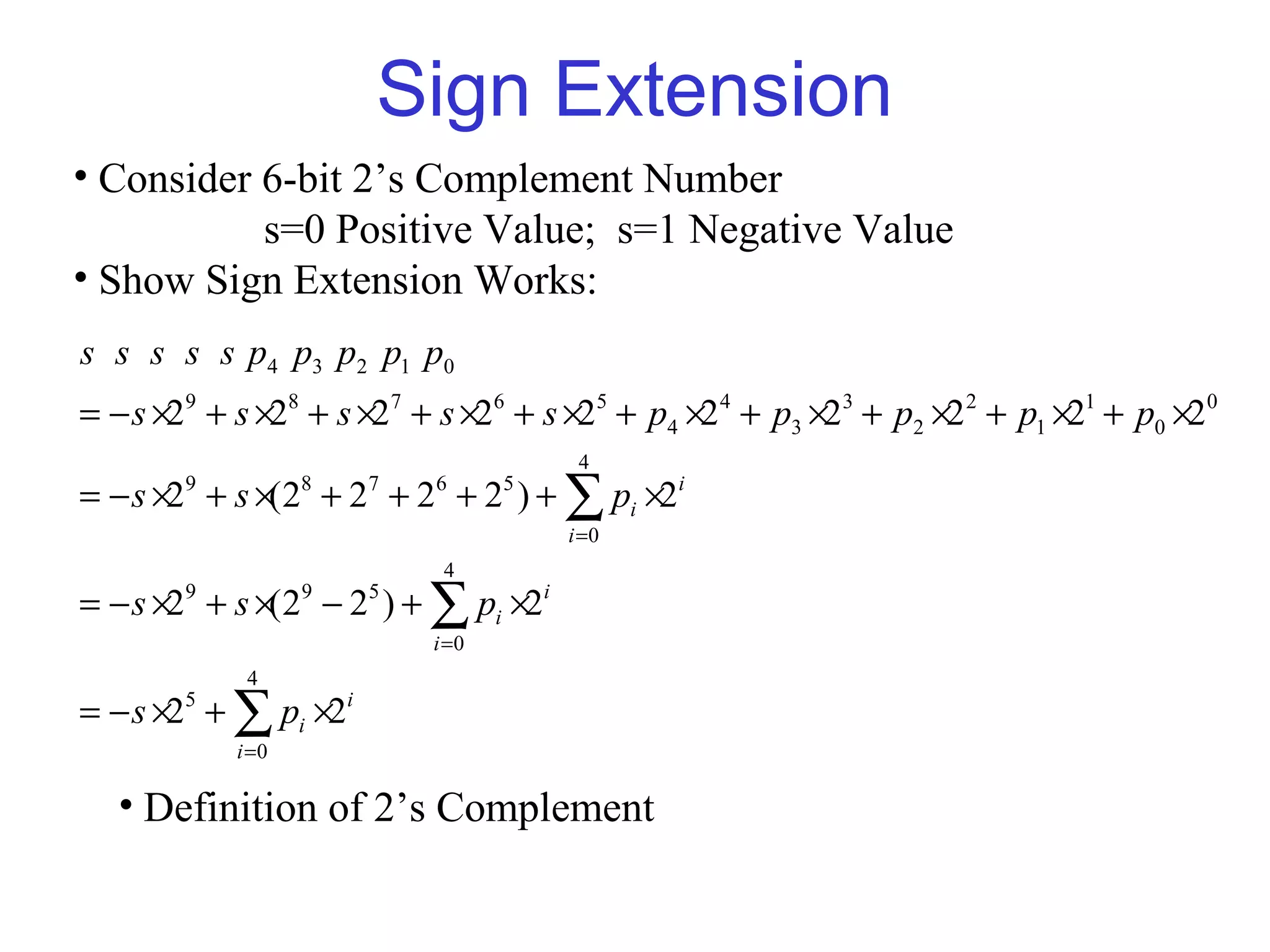

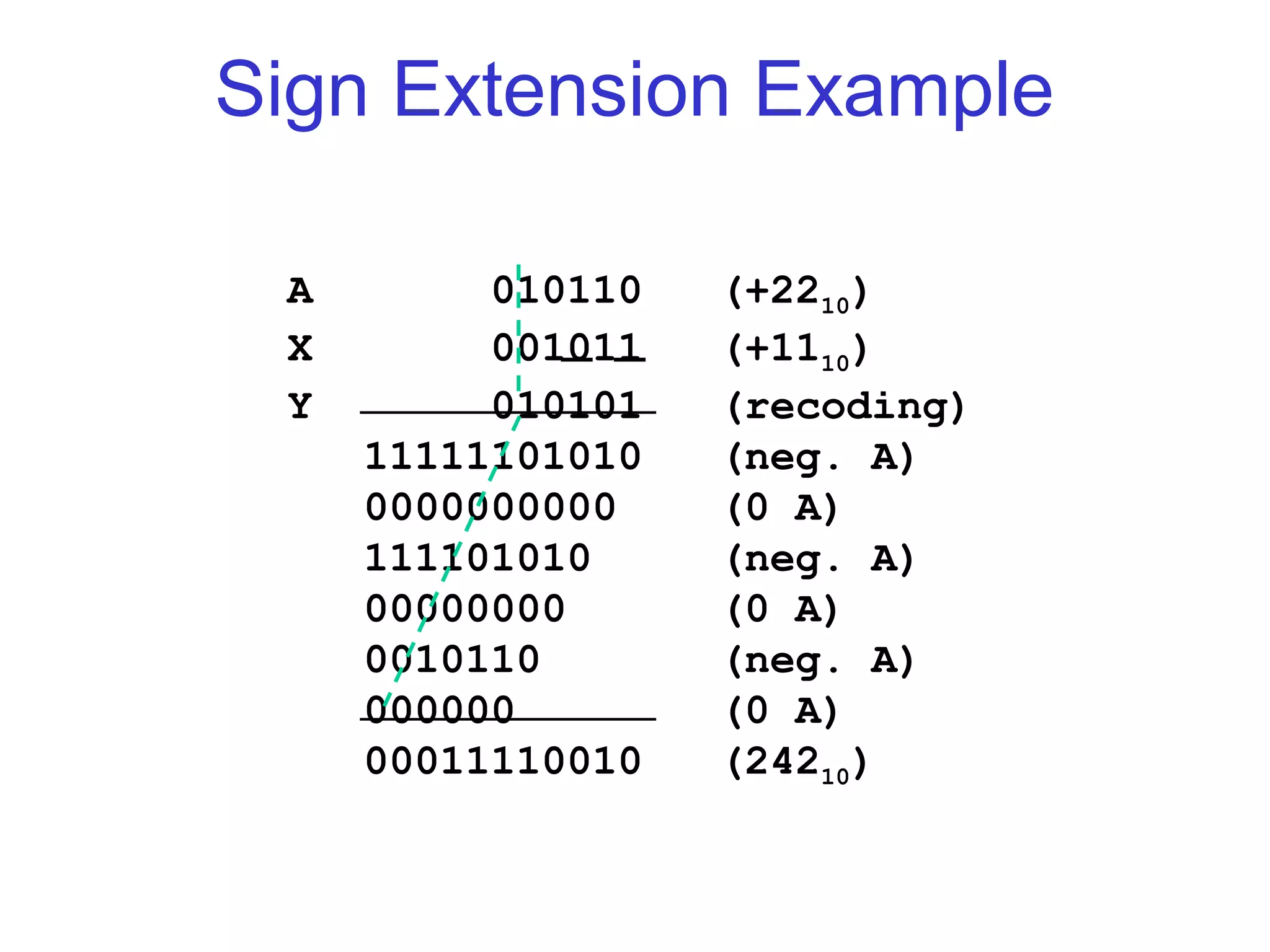

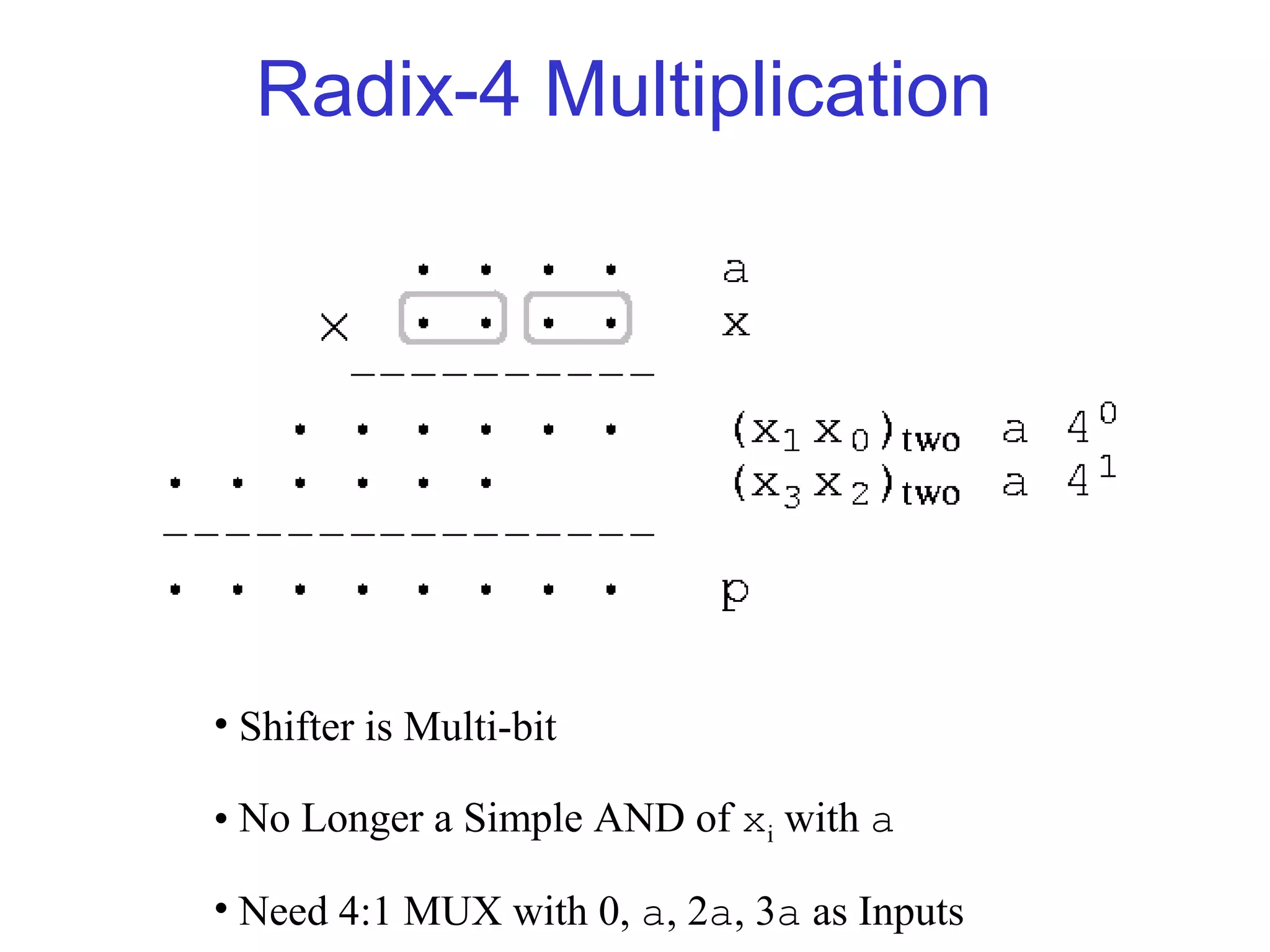

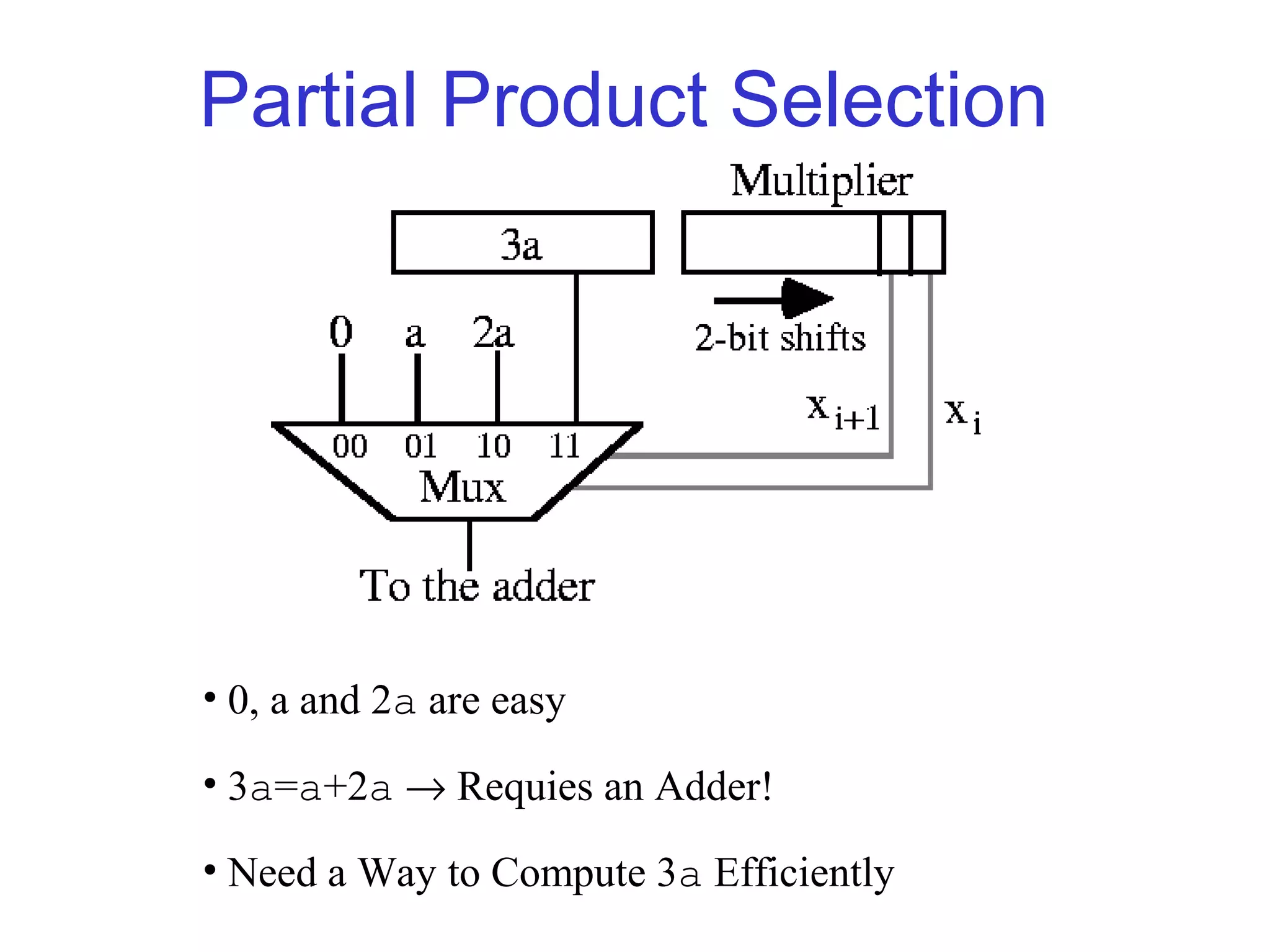

The document discusses various techniques for accelerating the multiplication process, including shift-and-add, Booth's recoding, and higher radix multipliers. Booth's recoding maps digit sets to [-1,1] to skip additions when partial products are zero. Modified Booth's recoding improves on this by considering three adjacent bits to encode multipliers into [-2,2], allowing the use of radix-4 grouping to reduce the number of partial product additions. Modern multipliers apply Modified Booth's Recoding to take advantage of its higher radix structure.

![Booth’s Recoding

• Maps Words With Digit Set [0,1] to Those With [-1,1]](https://image.slidesharecdn.com/multiplier-130126014439-phpapp02/75/Booth-Multiplier-14-2048.jpg)

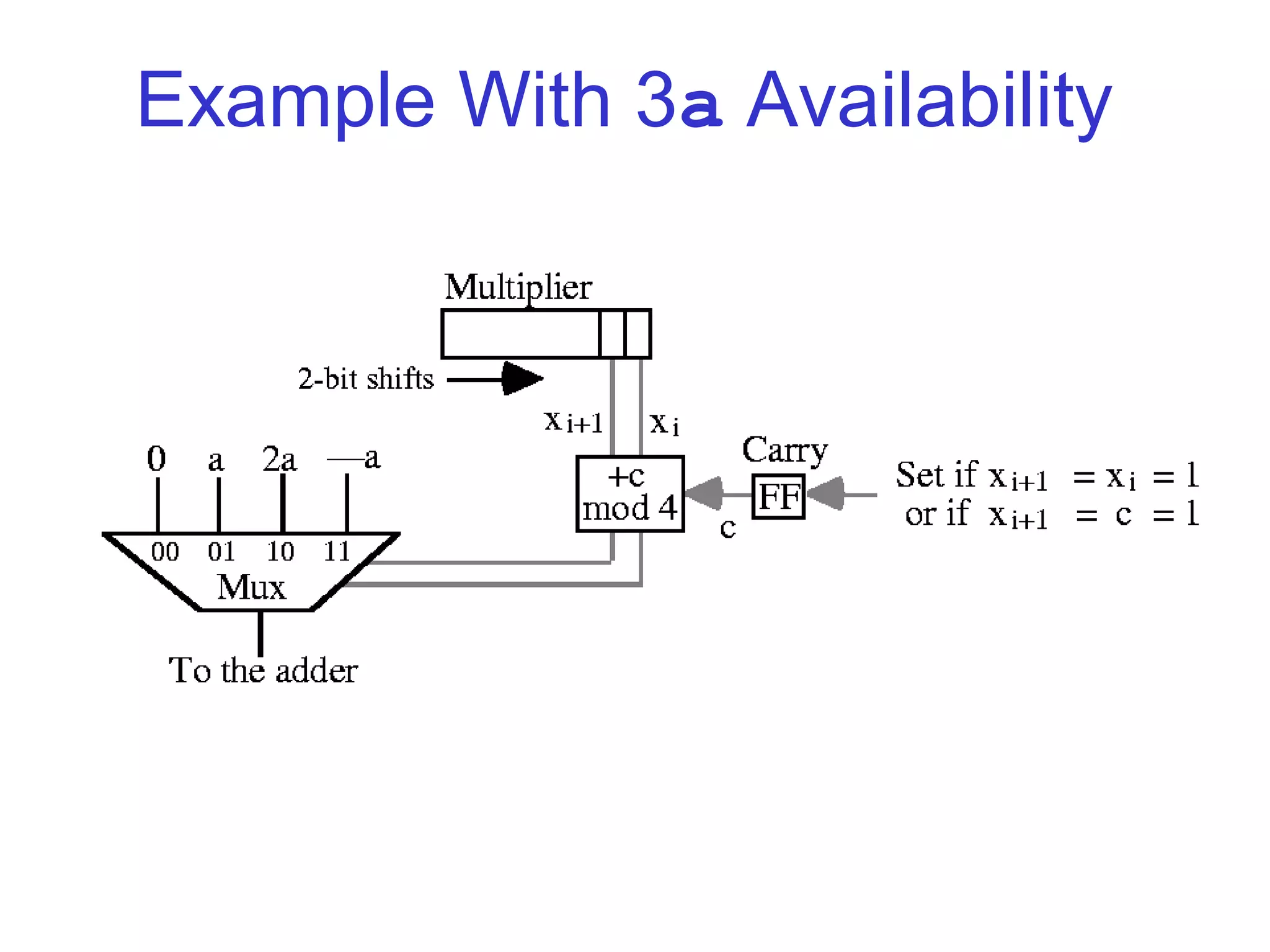

![Computing 3a

• One Way is to Precompute 3a and Store in Register Initially

• Another Way is When 3a Occurs Add -a

• Send Carry of 1 to Next into Next Radix-4 Digit of Multiplier

• Causes Incoming Multiple to be [0,4] Versus [0,3]

– 4 Because incoming carry to 112 Causes Digit 1002

• Multiples 0, 1, 2 Handled Easily

• Multiple 3 Converted to –1 With Outgoing Carry of 1

• Multiple 4 Converted to 0 With Outgoing Carry of 1

• Requires Extra Cycle of Computation Since MSD May Have Carry](https://image.slidesharecdn.com/multiplier-130126014439-phpapp02/75/Booth-Multiplier-26-2048.jpg)

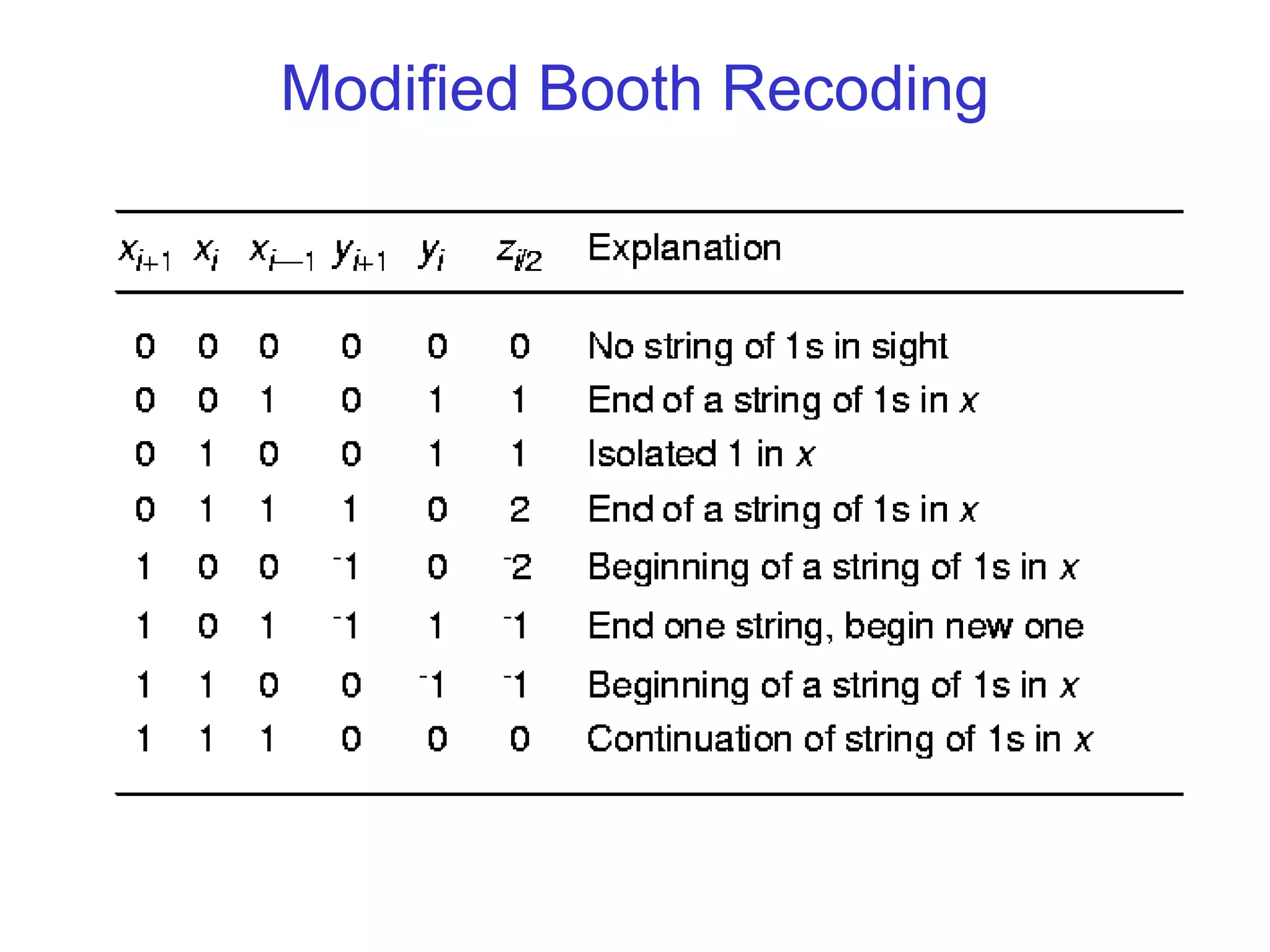

![Modified Booth Recoding

• Booth Recoding Results From xi and xi-1

• Radix-4 Multiplier Digits Implies Booth Recoding

Based on xi+1, xi and xi-1

• Similar to Classical Booth Recoding, Modified Booth

Recoding Encodes Multipliers into [-2,2]](https://image.slidesharecdn.com/multiplier-130126014439-phpapp02/75/Booth-Multiplier-30-2048.jpg)