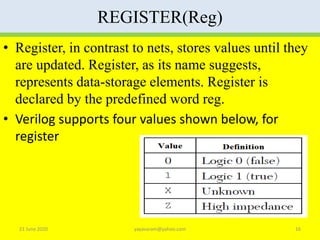

The document discusses different data types in Verilog including nets, registers, vectors, real numbers, parameters, arrays, and integers. It explains that nets like wire are used to model physical connections and do not store values while registers like reg can store values. Vectors allow declaring registers and nets with multiple bits. Parameters represent symbolic constant values. Arrays allow declaring registers with multiple elements. Integers are for non-hardware variables like loop indices.

![Contd

• By default Nets are 1-bit values. But it can be a

vector also.

• For ex: wire [31:0]bus ; Here the size of the bus is

32 bit vector and it is a wire type.

• All unconnected nets are set to ‘z’.(High impedance)

• Also wire is always input , for standard

interconnection.

• Nets are used to model connections between

continuous assignments and instantiations.

21 June 2020 7yayavaram@yahoo.com](https://image.slidesharecdn.com/verilog-datatypes-200621065753/85/Verilog-data-types-For-beginners-7-320.jpg)

![VECTORS

• Vectors are multiple bits. A register or a net can be

declared as a vector.

• Vectors are declared by brackets [ ].

• Examples of vectors are:

• wire [31:0] a = 32’b1010;

• reg [7:0] total = 8’d12;

• The first statement declares a net a. It has 32 bits,

and its initial value is 00…1010 (b stands for bit).

The second statement declares a register total.

• Its size is eight bits, and its value is decimal 12 (d

stands for decimal).21 June 2020 18yayavaram@yahoo.com](https://image.slidesharecdn.com/verilog-datatypes-200621065753/85/Verilog-data-types-For-beginners-18-320.jpg)

![Example

module my_comp1 (X, Y, xgty, xlty, xeqy);

parameter N = 3;

input [N:0] X, Y;

output xgty, xlty, xeqy;

wire [N:0] sum, Y;

To change the size of the inputs x and y, the size of

the nets sum, and the size of net Y to eight bits, the

value of N is changed to seven as:

• parameter N = 7

21 June 2020 21yayavaram@yahoo.com](https://image.slidesharecdn.com/verilog-datatypes-200621065753/85/Verilog-data-types-For-beginners-21-320.jpg)

![ARRAYS

Verilog, in contrast to VHDL, does not have a predefined

word for array.

• Registers and integers can be written as arrays. For

example:

• parameter N = 4;

• parameter M = 3;

• reg signed [M:0] carry [0:N];

• The above statements declare an array by the name

carry. The array carry has five elements, and each

element is four bits. The four bits are in two’s

complement form. For example, if the value of a certain

element is 1001, then it is equivalent to decimal –7.21 June 2020 22yayavaram@yahoo.com](https://image.slidesharecdn.com/verilog-datatypes-200621065753/85/Verilog-data-types-For-beginners-22-320.jpg)

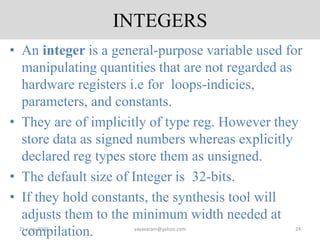

![contd

• An integer declaration uses the integer keyword and

specifies a list of variables.

• integer a, b; //two integers

• integer c [1:10]; // an array of integers.

• integer data; // integer

• integer i, j, k; // multiple integers

• An integer is a general purpose 32-bit variable.

Operations on it are assumed to be two's

complement and the most significant bit indicates

the sign.

21 June 2020 25yayavaram@yahoo.com](https://image.slidesharecdn.com/verilog-datatypes-200621065753/85/Verilog-data-types-For-beginners-25-320.jpg)