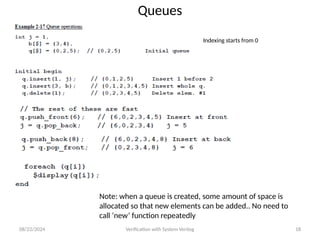

The document discusses various data types in System Verilog, contrasting them with Verilog-95 types. It outlines the distinctions between 4-state and 2-state data types, array types including fixed and dynamic arrays, and user-defined types, including enumerated types and their applications. Additionally, it highlights best practices for using these data types effectively in simulation and verification contexts.

![‘2 state’ data types

08/22/2024 Verification with System Verilog 5

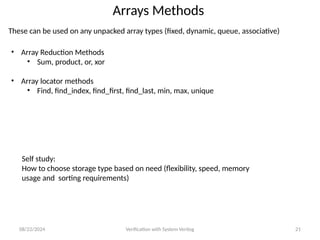

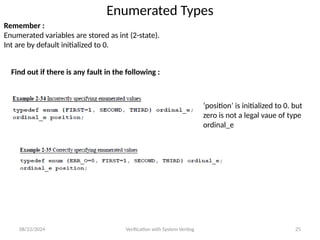

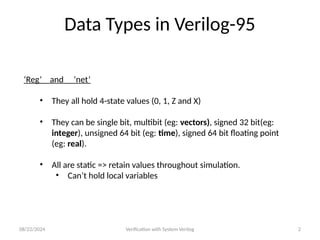

• In Verilog, all data types are 4-states.

• System verilog introduces ‘two-state’ data types (hold only ‘0’ or ‘1’).

• We use them where ‘x’ and ‘z’ not needed eg: test benches, loop variables,

• Make the simulators more efficient and also reduces memory storage requirements.

Ans: No.. One is 2 state and other is 4 state. Also, one is signed and

other is unsigned.. Hence range of data stored is different.

*Note

1) System verilog stores each element as a long-word (32 bit). Longint is stored in 2 long

words. Four state type like logic is also stored as 2-long words (64 bits)

2) ‘int’ is a 2 state data type while ‘integer’ is a 4 state data type.

Ques: Can we use ‘byte’ and logic[7:0] interchangably?](https://image.slidesharecdn.com/7-b-sysverilogdatatypes-240822174025-acf69d4a/85/7-B-SysVerilog_DataTypes-pptx-_-5-320.jpg)

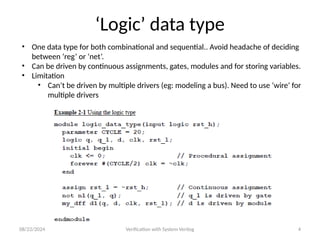

![Array Operations (multi-dimensional)

08/22/2024 Verification with System Verilog 11

Note the syntax :md[I,j]](https://image.slidesharecdn.com/7-b-sysverilogdatatypes-240822174025-acf69d4a/85/7-B-SysVerilog_DataTypes-pptx-_-11-320.jpg)

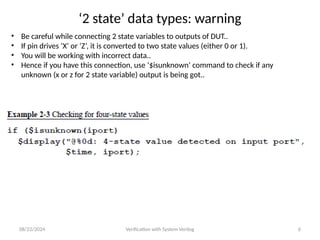

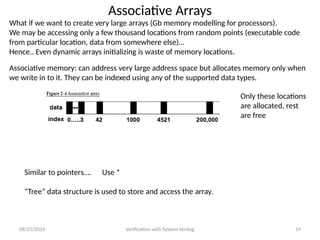

![Associative Arrays

08/22/2024 Verification with System Verilog 20

Foreach (variable[iterator])

The iterator can be anything, not

needed to be defined before.

1) Study about “addressing

using strings”.

‘first’ and ‘next’ are functions that

modify the index and return a ‘0’ or ‘1’

depending on existence of data in the

position](https://image.slidesharecdn.com/7-b-sysverilogdatatypes-240822174025-acf69d4a/85/7-B-SysVerilog_DataTypes-pptx-_-20-320.jpg)