This document compares the Open Verification Methodology (OVM) and Universal Verification Methodology (UVM). It describes the key differences between OVM and UVM phases, managing end of test, component configuration, and register modeling. The UVM phases have been expanded and modified compared to OVM phases. UVM also introduced changes to how components are configured and the end of test is managed.

![5 Configuring Component

In UVM it is recommended to use “uvm_config_db” method for configuring components. OVM used the “[set,get]_config_[int,string,object]“

methods for configuring components. The UVM equivalents of these methods are available, but not recommended.

The “uvm_config_db” is parameterized by the type of object that is being configured.

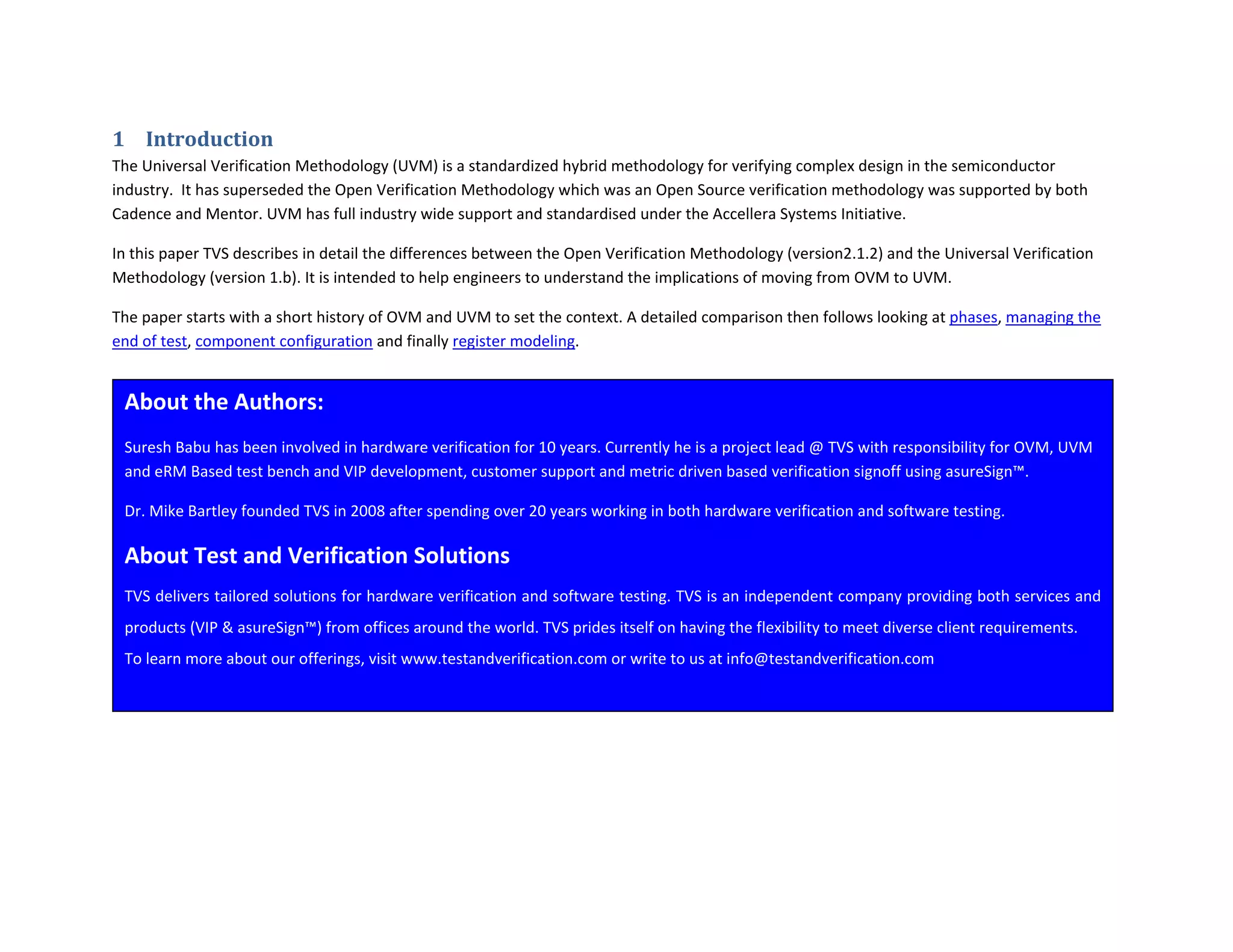

OVM UVM

class my_env extends ovm_env;

...

function void build();

ahb_cfg = ahb_config::type_id::create("ahb_cfg");

ahb_cfg.width = 16;

// set additional fields

set_config_object("*","ahb_cfg",ahb_cfg);

endfunction

...

endclass

class my_ahb_agent extends ovm_component;

...

function void build();

ovm_object cfg;

ahb_config my_cfg;

assert(get_config_object("ahb_cfg",cfg,0);

if (!$cast(my_cfg, cfg))

ovm_report_error(...);

...

endfunction

...

endclass

class my_env extends uvm_env;

...

function void build();

ahb_cfg = ahb_config::type_id::create("ahb_cfg");

ahb_cfg.width = 16;

// set additional fields

uvm_config_db#(ahb_config)::set(

this,"ahb_agent","ahb_cfg",ahb_cfg);

endfunction

...

endclass

class my_ahb_agent extends uvm_component;

...

function void build();

ahb_config my_cfg;

if (!uvm_config_db::ahb_config::get(

this,"","ahb_cfg",my_cfg);

`uvm_error(...)

...

endfunction

...

endclass

Table 4: Configuring components in OVM and UVM](https://image.slidesharecdn.com/ovm-vs-uvm-151016033906-lva1-app6892/75/Ovm-vs-uvm-8-2048.jpg)

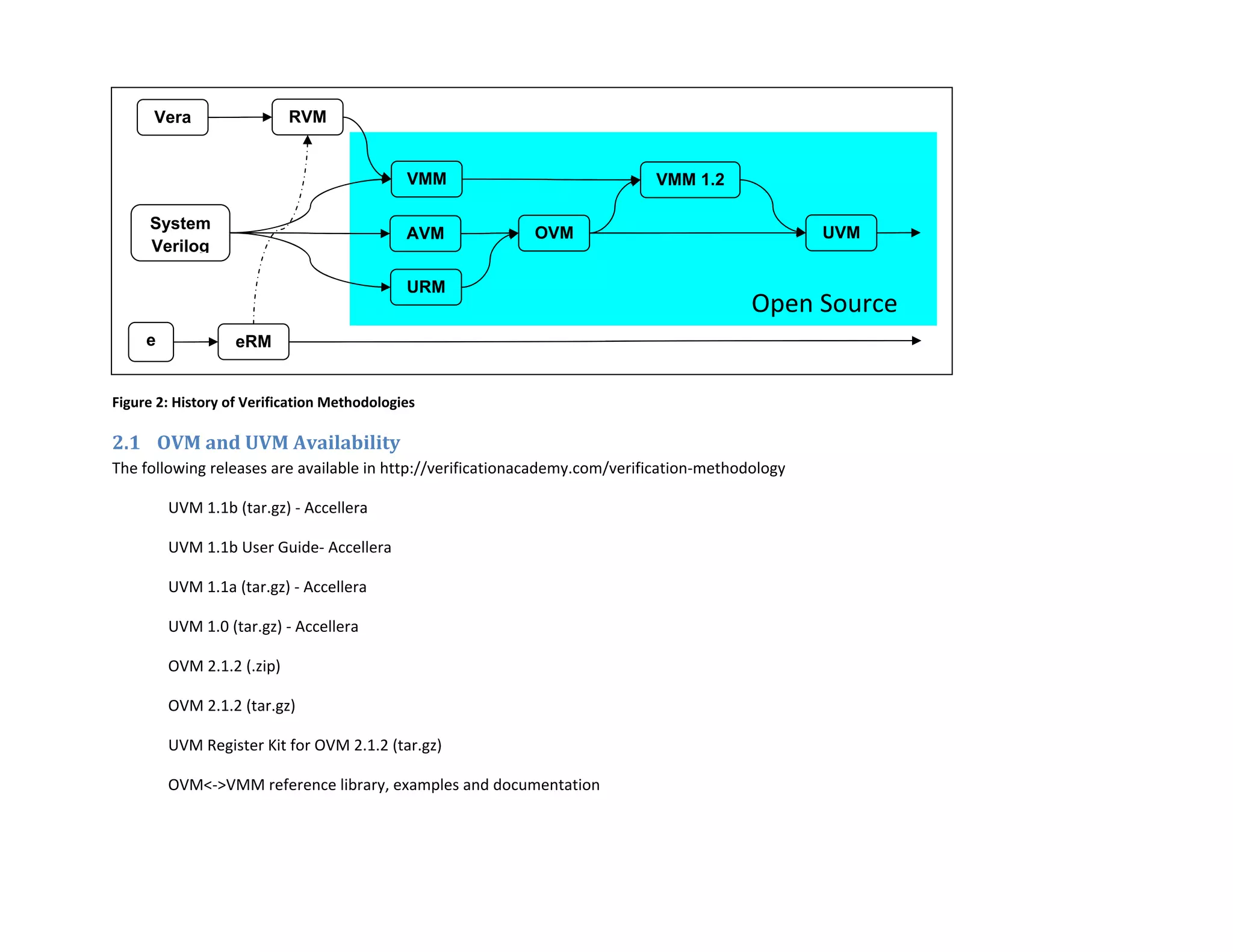

![It is recommended to avoid using “assign_vi” function that takes a virtual interface handle as an argument and calls an equivalent function on

one or more child component. This is repeated down until the last component reached.

Following approach is not recommended

XBUS ENV

function void assign_vi(virtual interface xbus_if xi);

xi0 = xi;

if( bus_monitor != null) begin

bus_monitor.assign_vi(xi);

end

for(int i = 0; i < num_masters; i++) begin

masters[i].assign_vi(xi);

end

for(int i = 0; i < num_slaves; i++) begin

slaves[i].assign_vi(xi);

end

endfunction : assign_vi

AGENT

function void assign_vi(virtual interface xbus_if xmi);

monitor.assign_vi(xmi);

if (is_active == UVM_ACTIVE) begin

sequencer.assign_vi(xmi);

driver.assign_vi(xmi);

end

endfunction : assign_vi

Table 5: Avoid using “assign_vi”](https://image.slidesharecdn.com/ovm-vs-uvm-151016033906-lva1-app6892/75/Ovm-vs-uvm-9-2048.jpg)