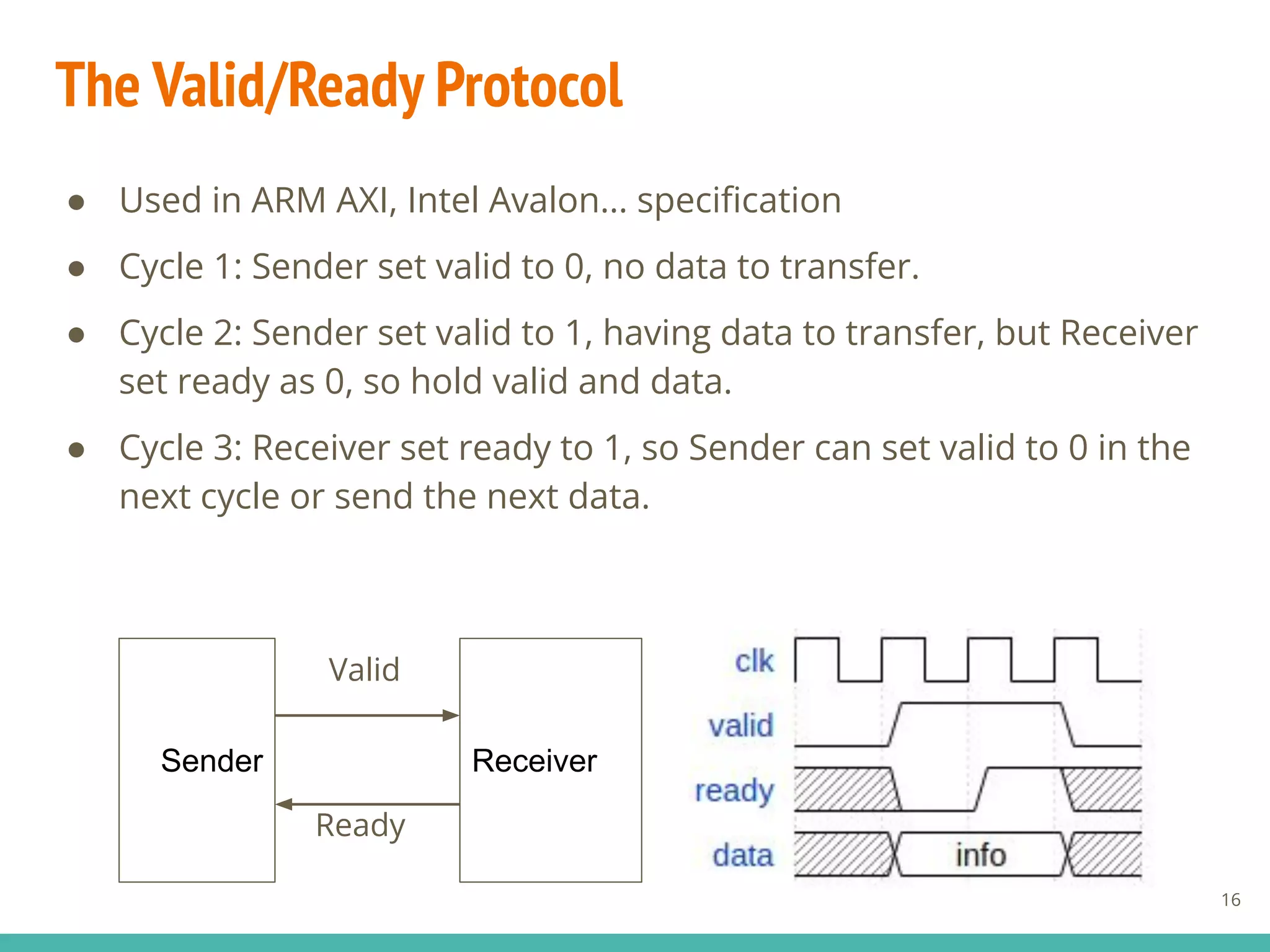

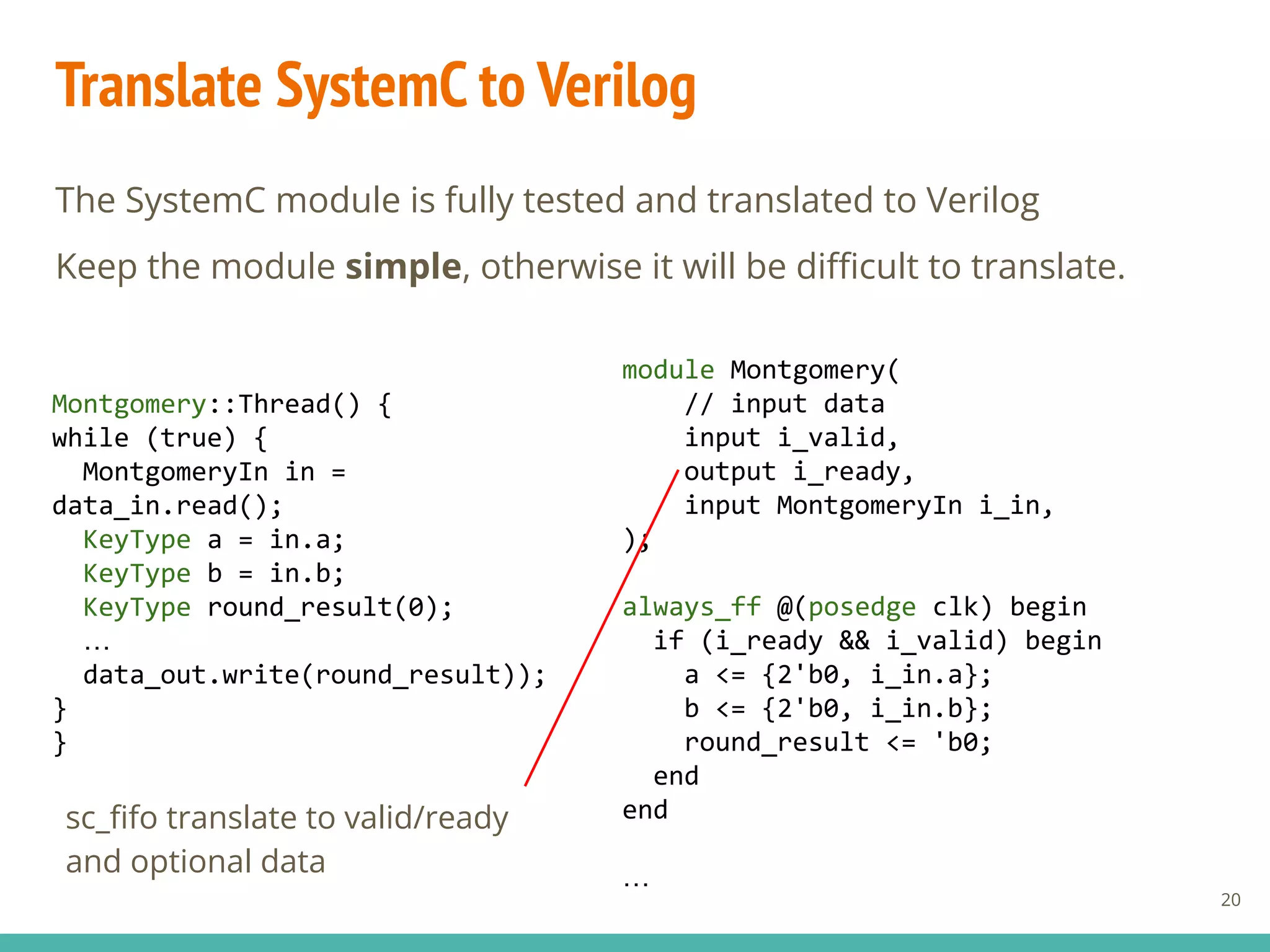

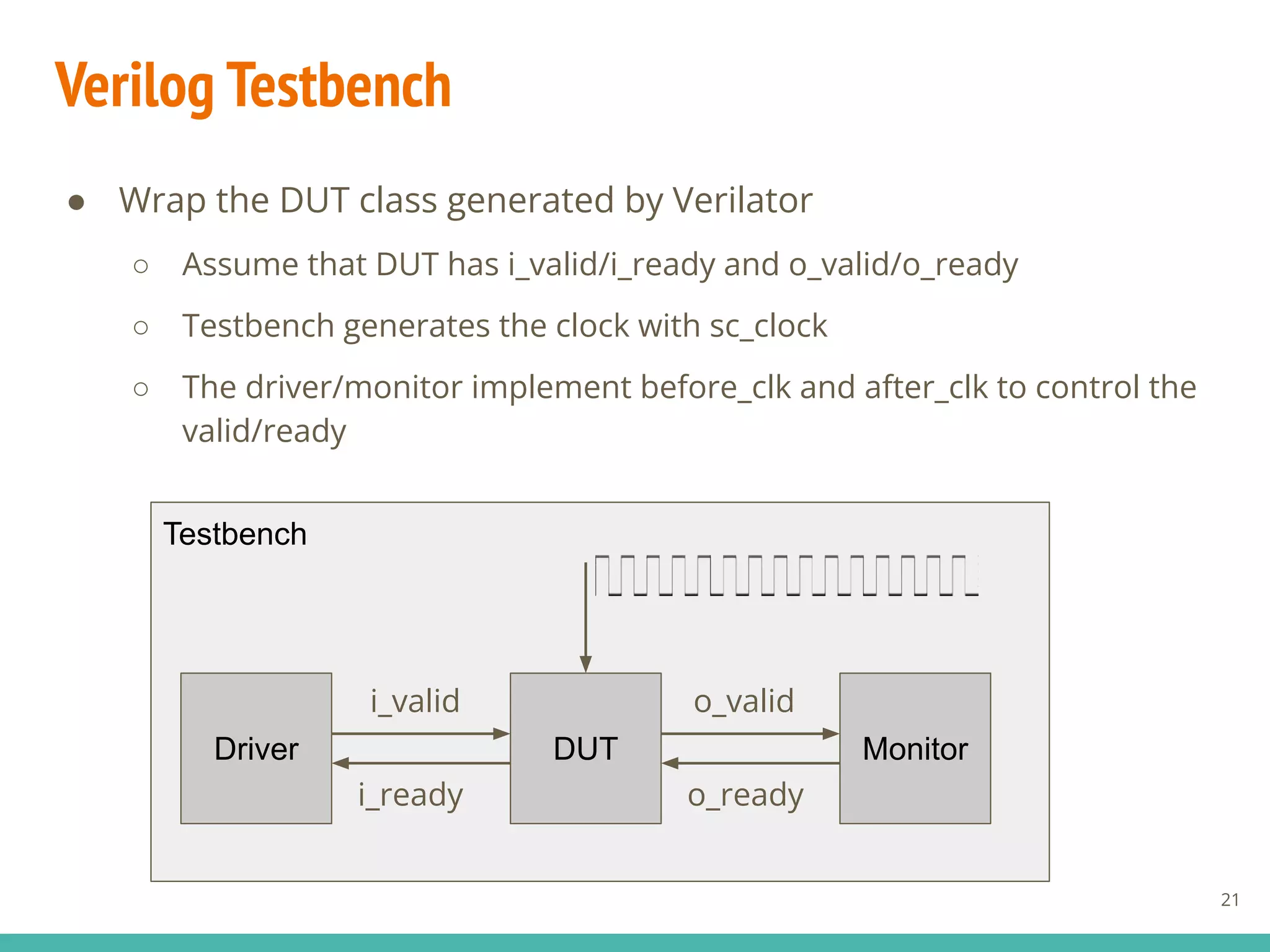

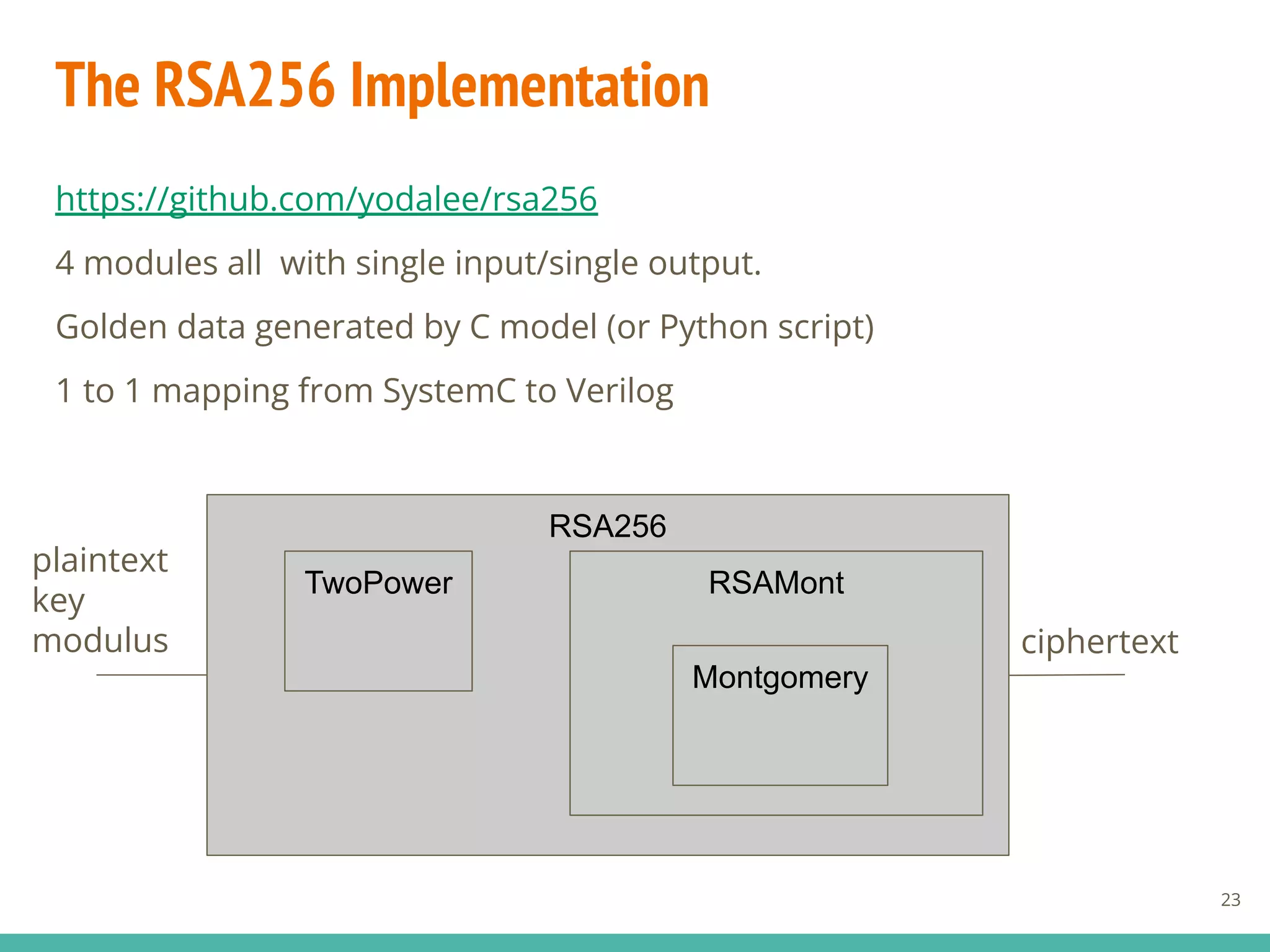

The document discusses robust Verilog testing using Verilator, SystemC, and C++17, with a focus on simplifying SystemVerilog (SV) coding through structures and arrays. It includes a case study on implementing RSA256 while tackling challenges related to signal handling and data type conversions between SV and C++. The document highlights the creation of new data types to facilitate better integration between SystemC and Verilog, ultimately enhancing simulation efficiency.

![How Verilator works

5

module Mod(

input [7:0] i_data,

output output_ok,

output [12:0] o_data [2]

);

struct VMod {

u8 i_data;

u8 output_ok;

u16 o_data[2];

};

VMod m;

m.i_data = 45;

while (not m.output_ok) {}

EXPECT_EQ(m->o_data[0], 30);

Verilog

User C++ testbench

Generated C++

Simulation Binary

./run.exe

Gtest: 100 != 30](https://image.slidesharecdn.com/coscup2023rsa256verilator-230803015754-9648aef9/75/COSCUP2023-RSA256-Verilator-pdf-5-2048.jpg)

![Challenges

6

module Mod(

input [7:0] i_data,

output output_ok,

output [12:0] o_data [2]

);

struct VMod {

u8 i_data;

u8 output_ok;

u16 o_data[2];

};

VMod m;

m.i_data = 45;

while (not m.output_ok) {}

EXPECT_EQ(m->o_data[0], 30);

Verilog

User C++ testbench

Generated C++

Simulation Binary

./run.exe

Gtest: 100 != 30

Too many signals to control

Solution: use struct

Bitwidth information loss](https://image.slidesharecdn.com/coscup2023rsa256verilator-230803015754-9648aef9/75/COSCUP2023-RSA256-Verilator-pdf-6-2048.jpg)

![Use Struct to Simplify SV & Challenges

7

Verilog

Bitwidth information loss

Struct information loss [2]

Support struct v5.000+ [1]

module Mod(

input [7:0] i_data,

input [13:0] i_data2,

input i_data3

);

typedef struct {

logic [7:0] data;

logic [13:0] data2;

logic data3;

} ModIn ;

module Mod(

input ModIn i

);

SystemVerilog

class VMod {

u32 i;

};

Generated C++

[1] We use v5.006 right now.

[2] Verilator has intensive issue and PR about this.

rewrite](https://image.slidesharecdn.com/coscup2023rsa256verilator-230803015754-9648aef9/75/COSCUP2023-RSA256-Verilator-pdf-7-2048.jpg)

![We need int/array/struct that works for SV and C++

● Challange: Information loss when converting from SV to Verilator

C++

○ Bitwidth & struct information

● Why?

○ The interface that Verilator will convert to is not standardized.

● Solution: Abstraction

○ Build a SV-compatible type system with C++17

8

typedef struct {

logic [7:0] data;

logic [13:0] data2;

logic data3;

} ModIn ;

class ModIn {

u32 i;

};

User code Adaptor

Generated C++

SV-C++ interface](https://image.slidesharecdn.com/coscup2023rsa256verilator-230803015754-9648aef9/75/COSCUP2023-RSA256-Verilator-pdf-8-2048.jpg)

![3 weapons mimicking the SV typing system

● vuint<11>

○ logic [10:0] sig;

○ Replace sc_uint

● varray<vuint<11>, 3, 4>

○ logic [10:0] sig [3][4];

○ std::array with multiple dimension

● vstruct (macro)

○ typedef struct packed { ... } iStruct;

○ C++17 based type reflection struct supporting $bits, $pack

9

← Example later](https://image.slidesharecdn.com/coscup2023rsa256verilator-230803015754-9648aef9/75/COSCUP2023-RSA256-Verilator-pdf-9-2048.jpg)

![● Why reinvent sc_uint<int>?

● sc_uint is virtual, we cannot memcpy

● sc_uint must link against libsystemc

● You need sc_biguint<int> for wide integers.

● vuint is strictly typed

○ vuint<10> == vuint<11> is disallowed, required by many Lint tools

● C++11 type deduction system and varadic length template

○ auto val = Concat(vuint<4>, vuint<99>, vuint<2>)

Arbitrary bitwidth integer

10

vuint<11> v

| |

logic [10:0] v](https://image.slidesharecdn.com/coscup2023rsa256verilator-230803015754-9648aef9/75/COSCUP2023-RSA256-Verilator-pdf-10-2048.jpg)

![Array

● Just like std::array, but high-dim.

● Also support array of struct.

11

varray<vuint<11>,2,3> v

| |

logic [10:0] v [2][3];

or

logic [0:1][0:2][10:0] v ;

We treat them the same](https://image.slidesharecdn.com/coscup2023rsa256verilator-230803015754-9648aef9/75/COSCUP2023-RSA256-Verilator-pdf-11-2048.jpg)

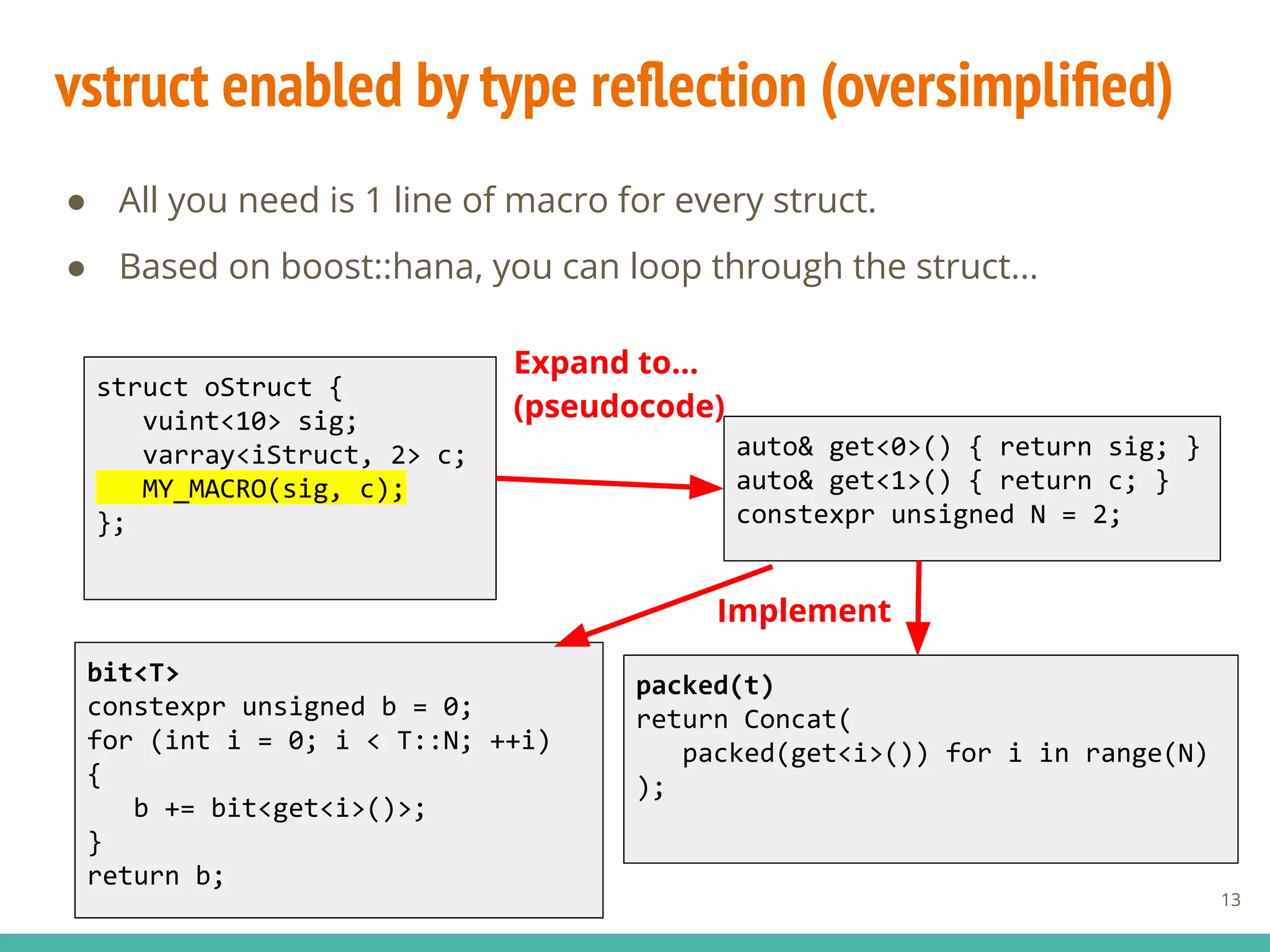

![vstruct (macro) : Verilog struct

● C++17 magic!

● We want to fully utilize C++ standard.

● In SystemVerilog:

○ $bit(oStruct) == 36

○ logic [$bit(oStruct)-1:0] v;

● Our C++ API allows us to:

○ vuint<bit<oStruct>> value;

○ vuint<36> value = packed(oStruct);

○ Also support: unpack, print json, Verilator I/O

struct iStruct {

vuint<3> a;

vuint<10> b;

};

struct oStruct {

vuint<10> sig;

varray<iStruct, 2> c;

};

12](https://image.slidesharecdn.com/coscup2023rsa256verilator-230803015754-9648aef9/75/COSCUP2023-RSA256-Verilator-pdf-12-2048.jpg)

![Example using vuint/varray/vstruct

parameter MOD_WIDTH = 256;

parameter INT_WIDTH = 32;

typedef logic [MOD_WIDTH-1:0] KeyType;

typedef logic [INT_WIDTH-1:0] IntType;

typedef struct packed {

IntType power;

KeyType modulus;

} TwoPowerIn;

constexpr unsigned MOD_WIDTH = 256;

constexpr unsigned INT_WIDTH = 32;

typedef vuint<MOD_WIDTH> KeyType;

typedef vuint<INT_WIDTH> IntType;

struct TwoPowerIn {

IntType power;

KeyType modulus;

MY_MACRO(power, modulus)

};

14

C++ Model SystemVerilog Package

The 1:1 SV-C++ mapping is beautiful](https://image.slidesharecdn.com/coscup2023rsa256verilator-230803015754-9648aef9/75/COSCUP2023-RSA256-Verilator-pdf-14-2048.jpg)

![How Verilator works

15

module Mod(

input [7:0] i_data,

output output_ok,

output [12:0] o_data [2]

);

struct VMod {

u8 i_data;

u8 output_ok;

u16 o_data[2];

};

VMod m;

m.i_data = 45;

while (not m.output_ok) {}

EXPECT_EQ(m->o_data[0], 30);

Verilog

User C++ testbench

Generated C++

Simulation Binary

./run.exe

Gtest: 100 != 30

How to drive

module?

How to feed data?

Verilog can have any

kind of interface](https://image.slidesharecdn.com/coscup2023rsa256verilator-230803015754-9648aef9/75/COSCUP2023-RSA256-Verilator-pdf-15-2048.jpg)