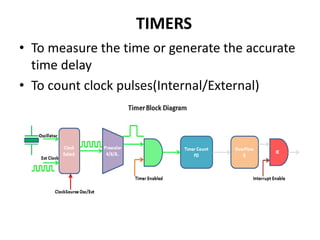

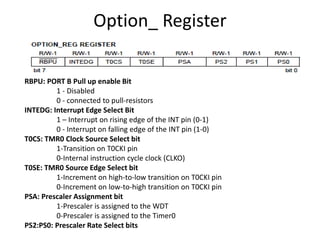

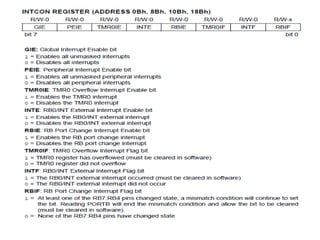

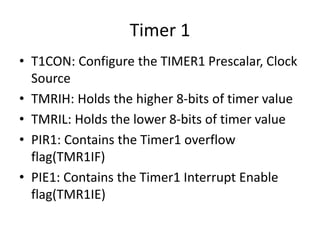

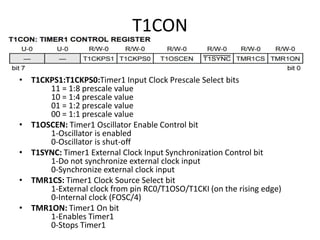

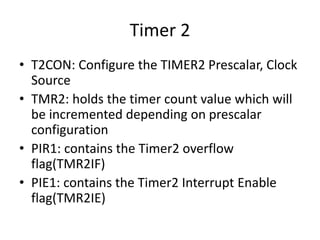

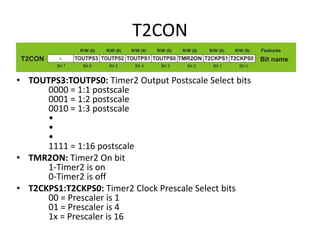

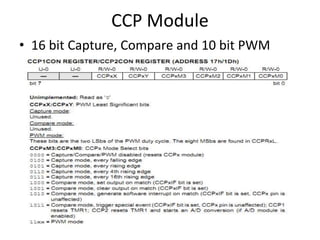

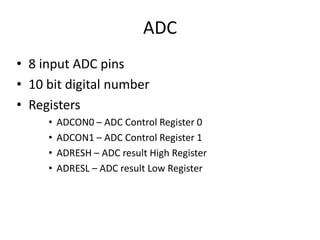

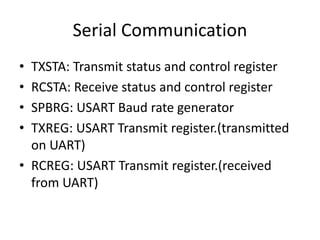

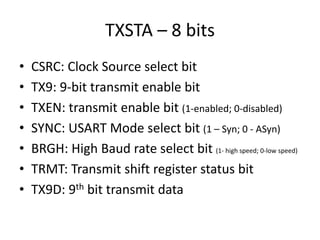

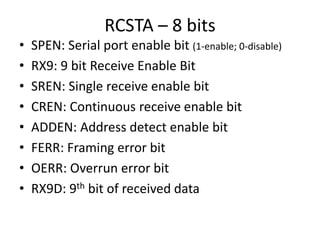

This document discusses timers, the CCP module, ADC, and serial communication in PIC microcontrollers. It provides details on the different timer modules including Timer 0, Timer 1, and Timer 2, and describes their control and count registers. It also summarizes the functions of the CCP module, ADC module, and components used for serial communication like TXSTA, RCSTA, and related registers.