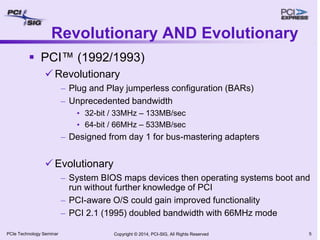

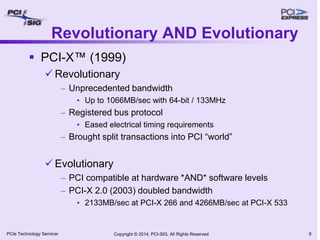

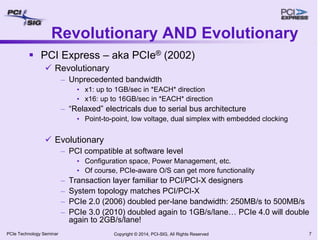

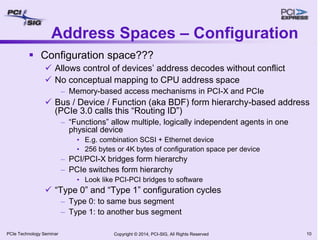

This document provides an overview of PCI Express (PCIe) basics and background. It begins with a brief history of PCI, PCI-X, and the revolutionary and evolutionary aspects of each. It then covers key PCI concepts like address spaces, configuration space, interrupts, split transactions, and transaction types. The document explains PCIe features such as its dual simplex serial connection, scalable link widths and speeds, packet-based protocol, and additional features like data integrity and flow control. It outlines the PCIe topology including endpoints, switches, and root complexes. Finally, it discusses the three methods for packet routing in PCIe and provides examples of programmed I/O and DMA transactions.

![PCIe Technology Seminar

Upcoming Events

Compliance Workshop #91 (Taipei)

Tomorrow

Compliance Workshop #92 (California)

December 2-5, 2014

PCI-SIG Developers Conference Israel

March 2-3, 2015

PCI-SIG Developers Conference

June 23-24, 2015

PCI-SIG Developers Conference APAC

[TBD] October 2015?

Copyright © 2014, PCI-SIG, All Rights Reserved 43](https://image.slidesharecdn.com/pciexpressbasicsbackground-220823090010-83fb36e0/85/PCI_Express_Basics_Background-pdf-43-320.jpg)