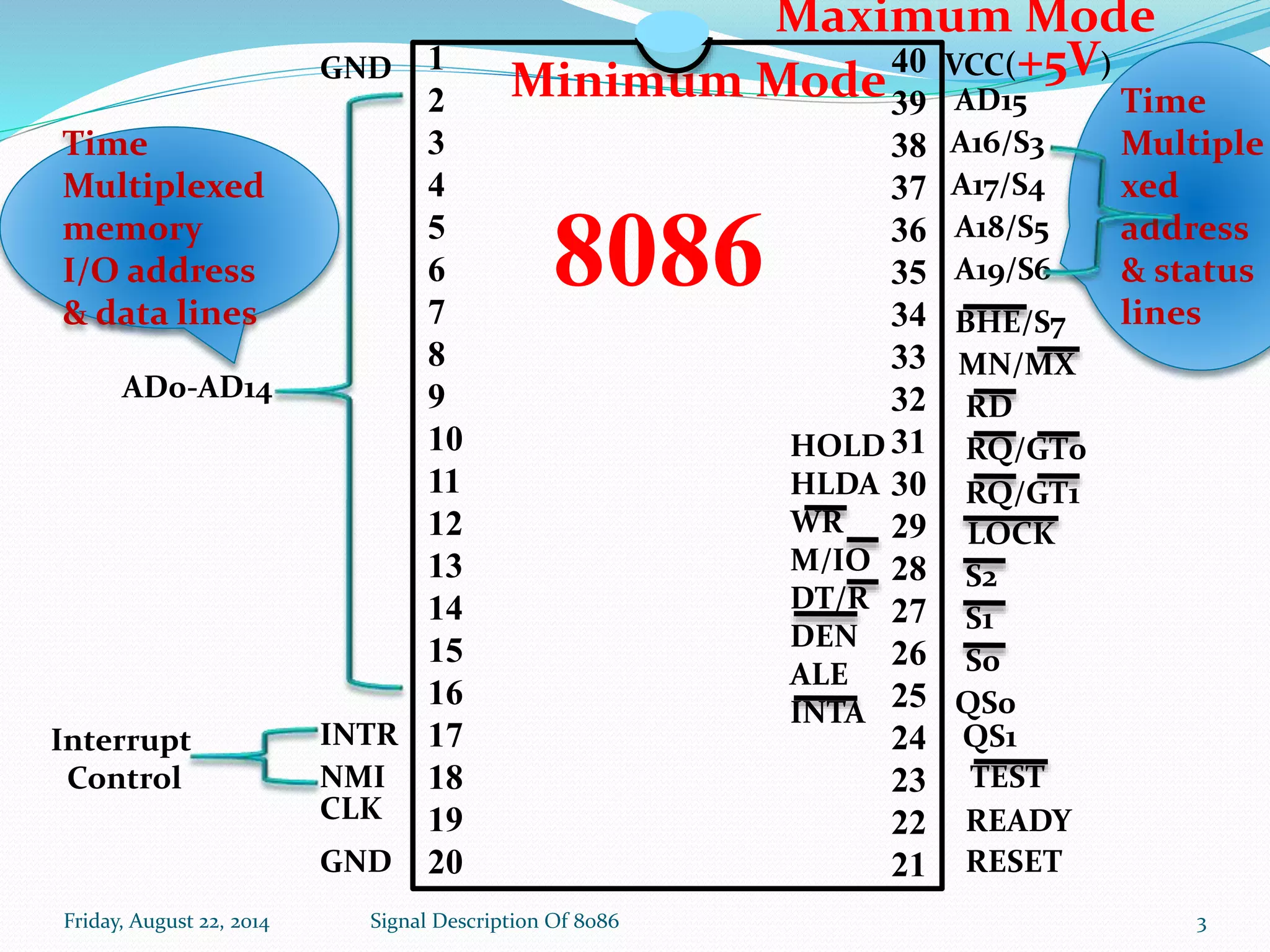

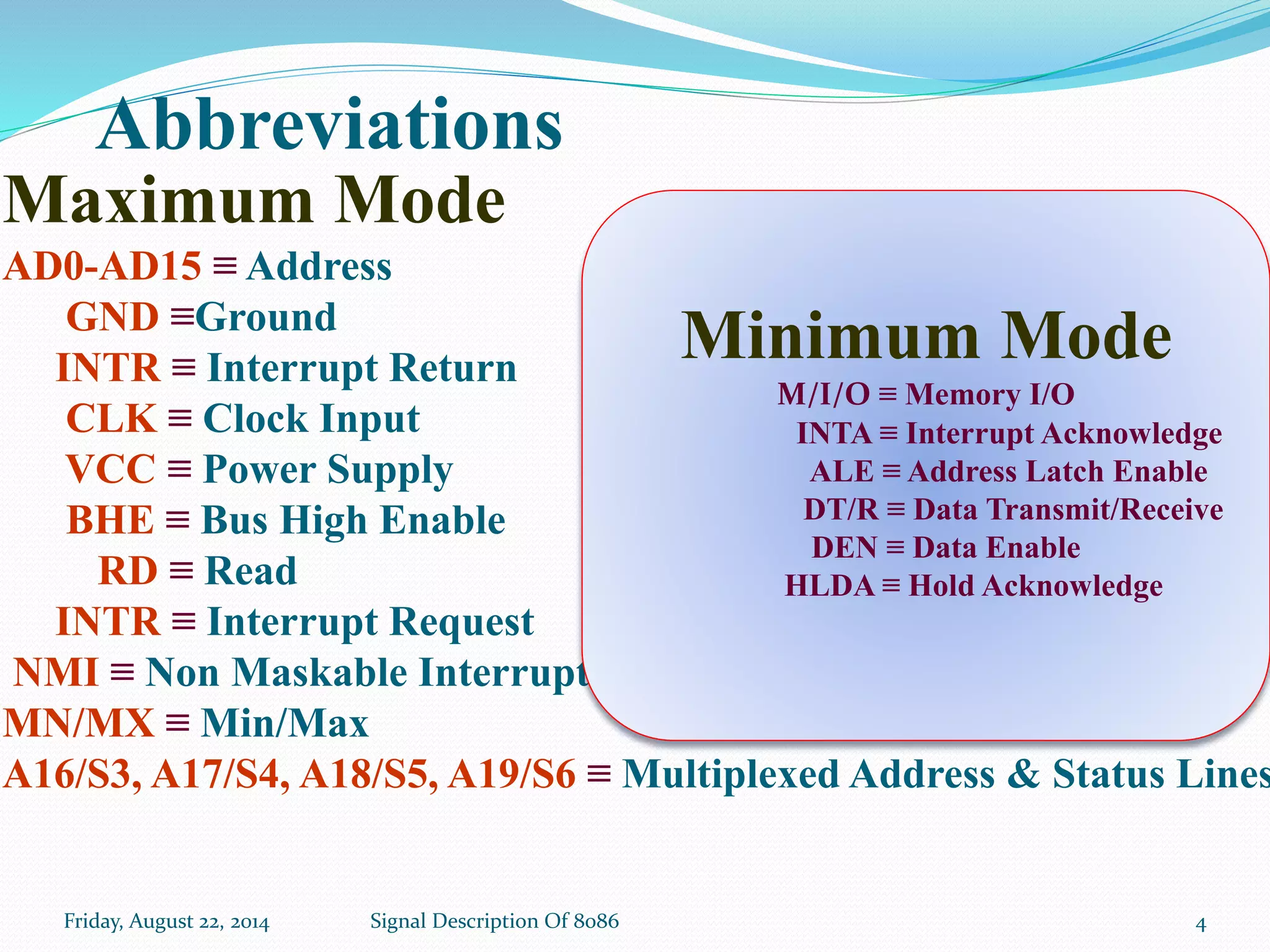

The document discusses the signal description of the 8086 microprocessor. It describes that the 8086 has 40 pins and can operate at 5, 8, or 10 MHz clock speeds. It operates in single or multiprocessor configurations. Some pins have different functions depending on whether it is in minimum or maximum mode. The document then lists the various signals, their abbreviations, and briefly describes the purpose of several important pins including CLK, RESET, VCC, GND, INTA, ALE, HLDA, DT/R and DEN.