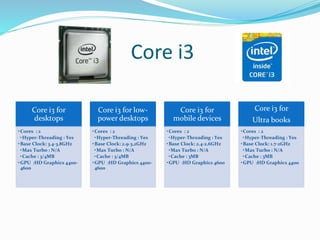

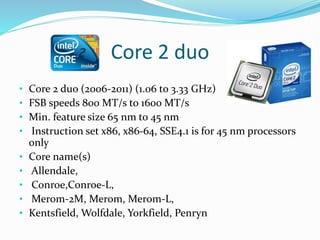

The document discusses the history and specifications of Intel Pentium processors from 1993 to the present. It describes the original Pentium processor and subsequent models including the Pentium II, Pentium III, and Pentium IV. It also discusses dual-core and Core 2 Duo processors, and provides details on the different Intel Core i3, i5, and i7 processors.

![Core I[x] Odd Chaos

Why does Intel produce core i3, core i5 and core i7

processors, but not core i2, core i4 or core i6 processors?

The information on letters and numbers is not longer

corresponding to a specific technical features or

technology on the Products.

This naming scheme is now divided as low-level units

(Core i3), mid-range units (Core i5) and high-end

performance processors (Core i7).

These names were selected only for marketing purposes.](https://image.slidesharecdn.com/sirazeempentium-160313060639/85/Pentium-processor-11-320.jpg)