The document discusses several topics related to embedded systems communication interfaces:

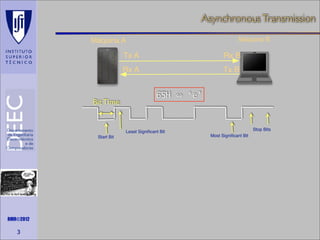

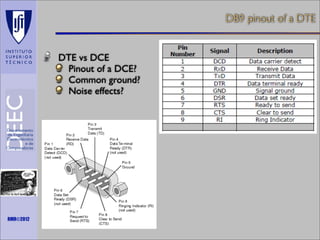

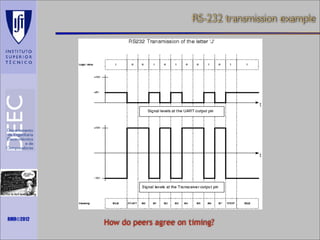

1) It introduces the Universal Asynchronous Receiver/Transmitter (UART) and describes asynchronous serial communication.

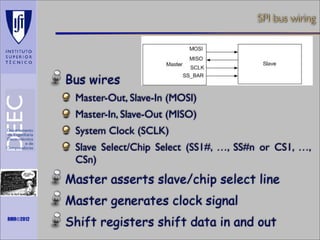

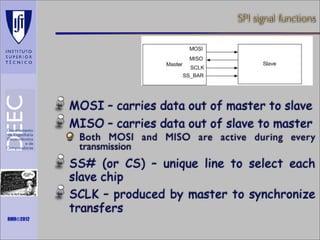

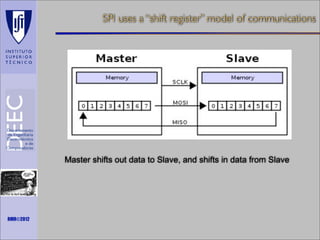

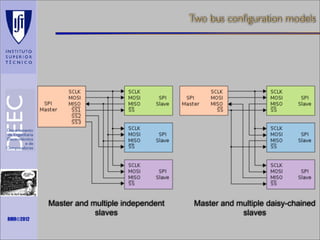

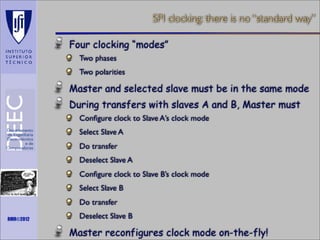

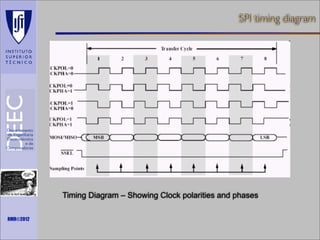

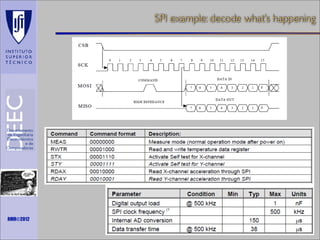

2) It then covers the Serial Peripheral Interface (SPI) in more detail, explaining what it is, its basic capabilities and wiring, communication protocol, and pros and cons.

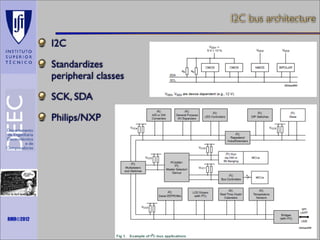

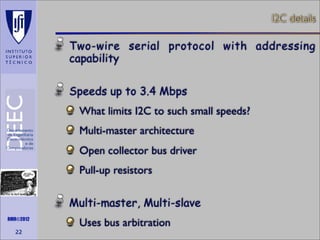

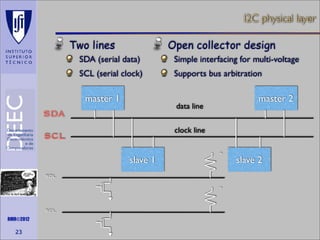

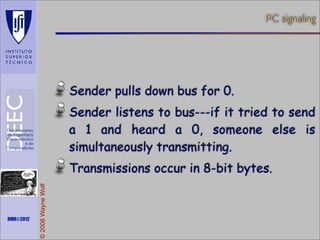

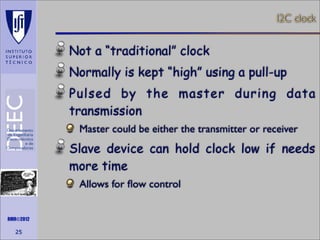

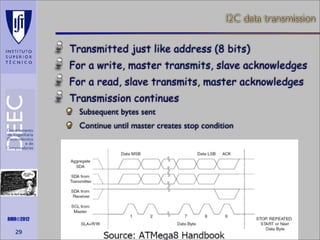

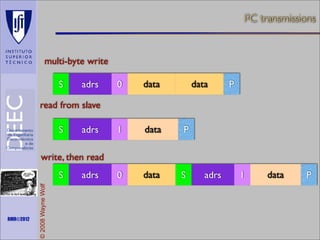

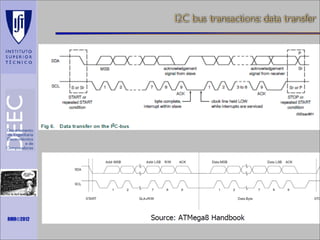

3) Finally, it discusses the Inter-Integrated Circuit (I2C) bus, providing an overview of its architecture, details on its physical layer, signaling, clocking, transactions including addressing and data transmission, bus arbitration, and examples of different transmission types.