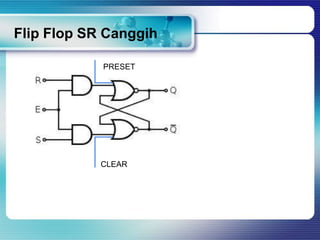

Dokumen tersebut membahas tentang rangkaian logika sekuensial yang merupakan rangkaian yang kondisi keluarannya dipengaruhi oleh kondisi input dan keadaan keluaran sebelumnya. Rangkaian utama dalam logika sekuensial adalah flip flop yang berfungsi sebagai pengingat data. Terdapat beberapa jenis flip flop seperti SR, JK, D, dan T yang memiliki tabel kebenaran masing-masing.