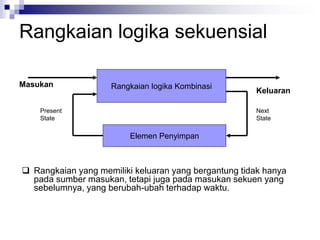

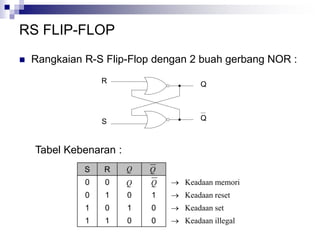

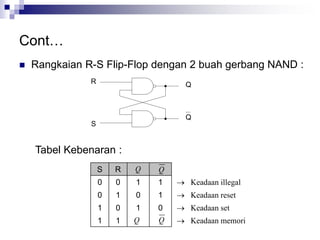

Dokumen tersebut membahas tentang rangkaian logika sekuensial yang menjelaskan konsep dasar rangkaian logika kombinasi dan sekuensial serta jenis-jenis flip-flop seperti RS flip-flop, D flip-flop, dan JK flip-flop beserta rangkaian dan tabel kebenarannya.