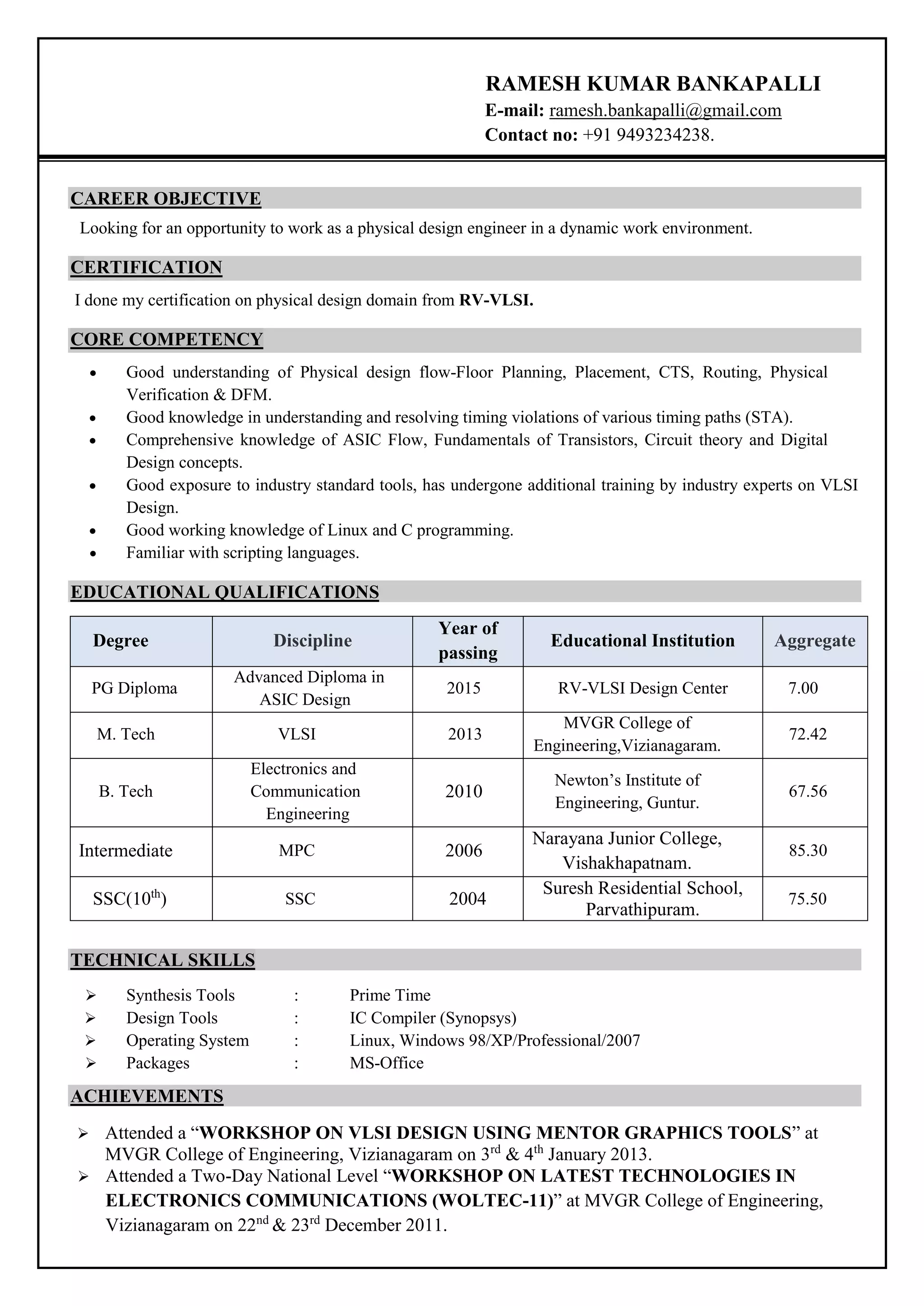

This document is a resume for Ramesh Kumar Bankapalli summarizing his objective, qualifications, skills and projects. He has a PG Diploma in ASIC Design from RV-VLSI Design Center and an M.Tech in VLSI. He has experience with synthesis tools like PrimeTime and design tools like IC Compiler. His projects include block level physical design of a torpedo subsystem and static timing analysis using 180nm technology.