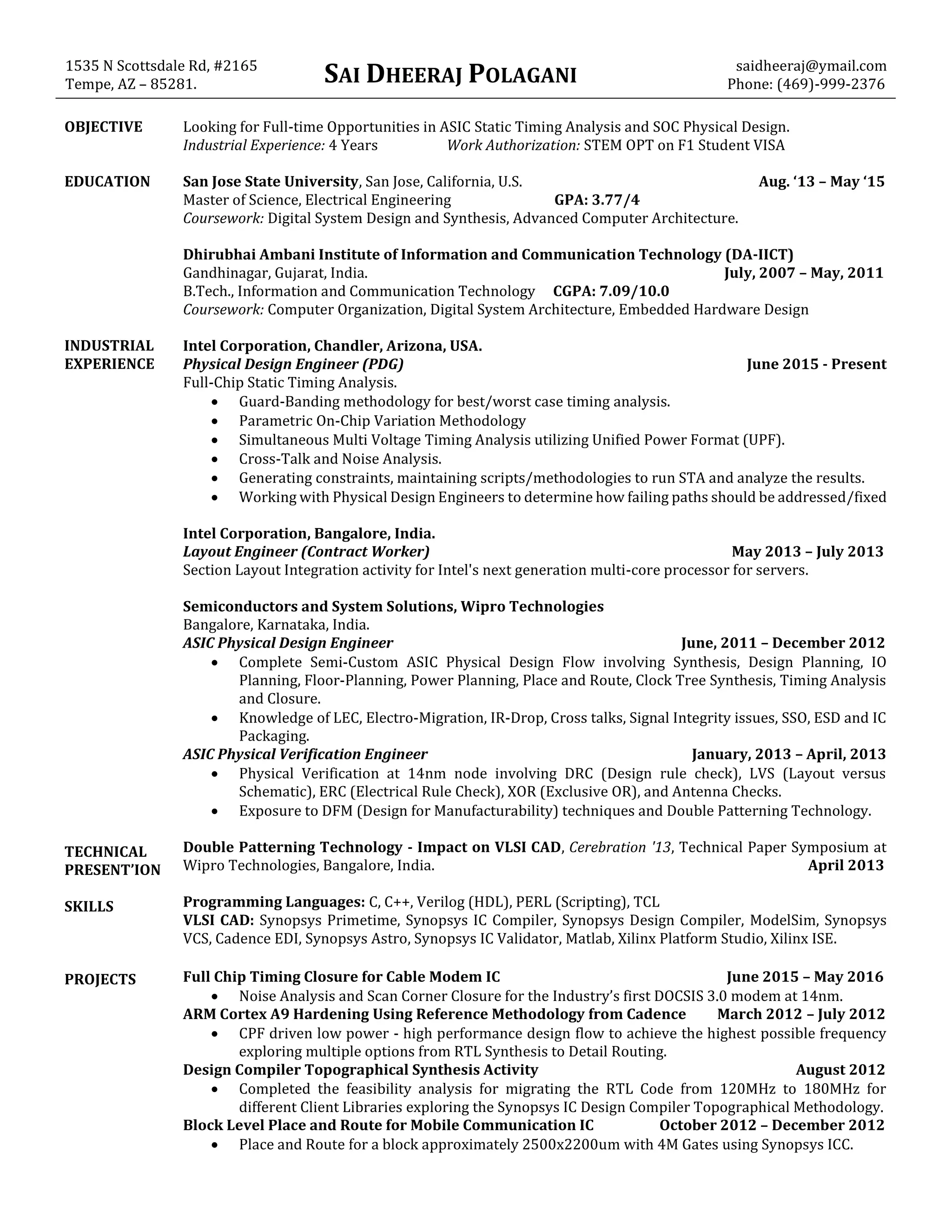

This document contains Sai Dheeraj Polagani's resume. It includes his contact information, objective, education history, industrial experience at Intel as a physical design engineer and layout engineer, previous experience at Wipro Technologies as an ASIC physical design and verification engineer, technical skills, projects completed and academic projects during his Master's program. His experience includes full-chip static timing analysis, noise analysis, cross-talk analysis, place and route, timing closure, and physical verification. He has a Master's in Electrical Engineering from San Jose State University and a Bachelors in Information and Communication Technology from DA-IICT, India.