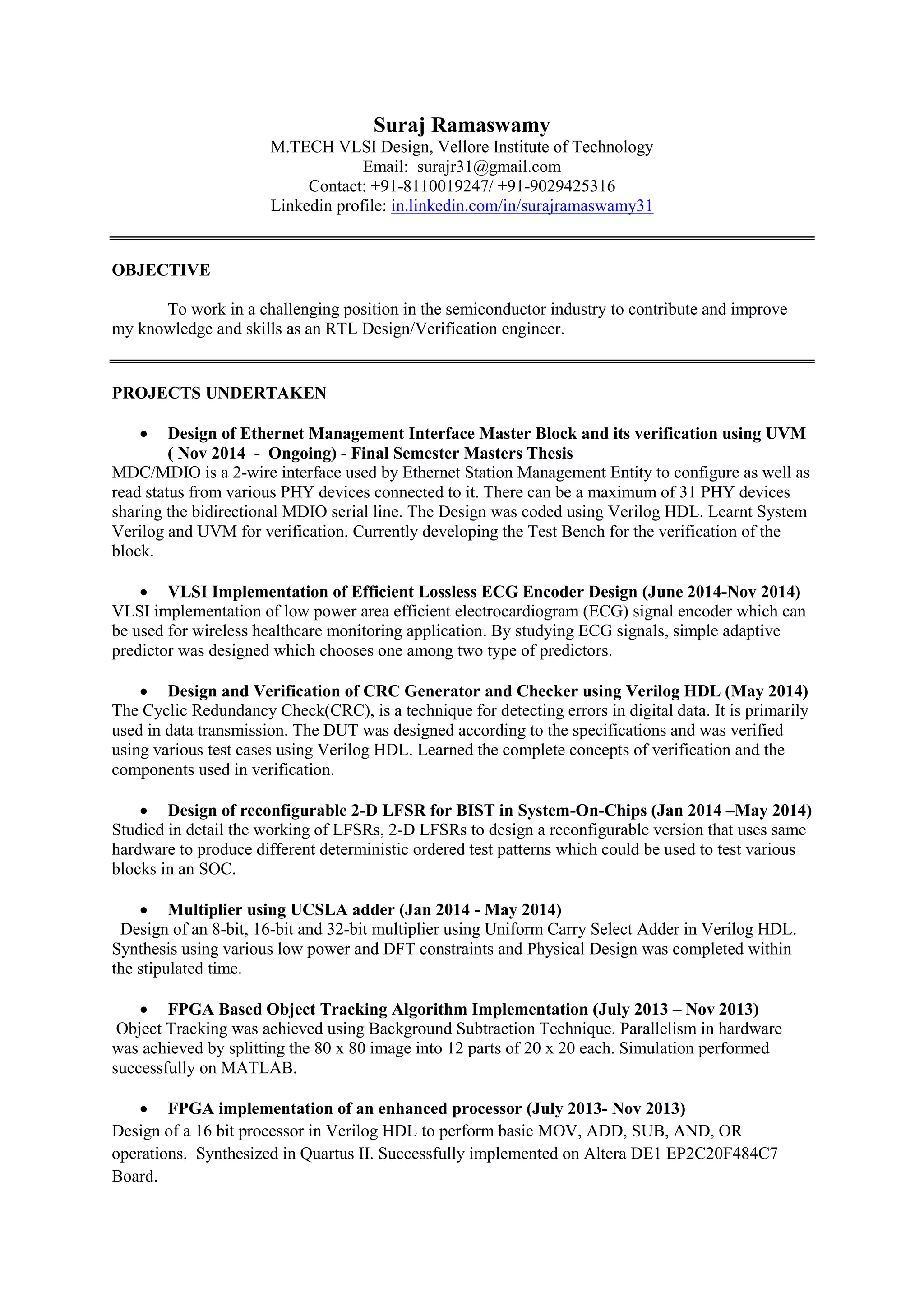

Suraj Ramaswamy is seeking a position in the semiconductor industry as an RTL Design/Verification engineer. He has a M.Tech in VLSI Design from Vellore Institute of Technology and has experience with projects involving Ethernet interface design and verification using UVM, ECG encoder design for healthcare applications, CRC generator/checker design and verification, reconfigurable LFSR design for BIST, and FPGA implementation of a basic processor and object tracking algorithm. His technical skills include Verilog, SystemVerilog, UVM, C, Java, MATLAB, and CAD tools from Cadence and Altera.