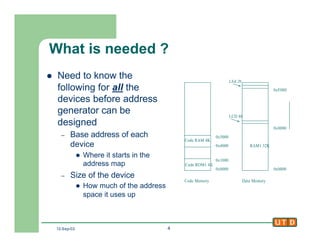

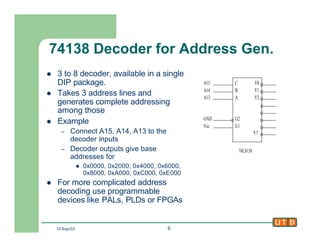

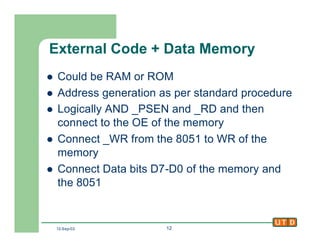

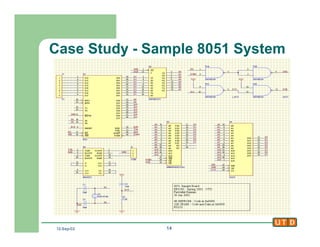

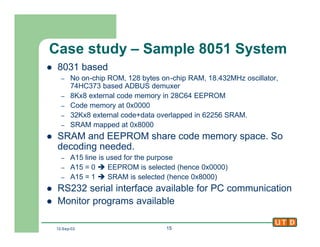

This document discusses address mapping techniques for interfacing external devices to an 8051 microcontroller. It explains that external devices can be mapped into the microcontroller's address space and accessed like memory, or interfaced through I/O ports. The document provides examples of generating chip enable signals to map devices at specific memory addresses and discusses using decoders like the 74138 for address decoding. It also covers interfacing external memory, non-memory devices, and a case study of a sample 8051 system with external memory and a serial interface.

![12-Sep-02 3

8051 – Address Generator

l Address Generator is a piece

of hardware that produces

unique addresses to each

interfaced device

l Each Interfaced Device can

use up 1 or more locations

from the address space of the

processor

– Memories typically use up in

Kilobytes (2K, 4K, 8K etc)

– Other devices typically use a

few (<16) addresses

l Addresses of devices should

not overlap

8051

A[15:0]

Addr. Gen

Device 1

Device 2

Device 3

CE

CE

CE

f1

f2

f3

D[7:0]

D[7:0]

D[7:0]

D[7:0]

A[15:0]

A[15:0]

A[15:0]](https://image.slidesharecdn.com/class6-141216232308-conversion-gate01/85/Class6-3-320.jpg)