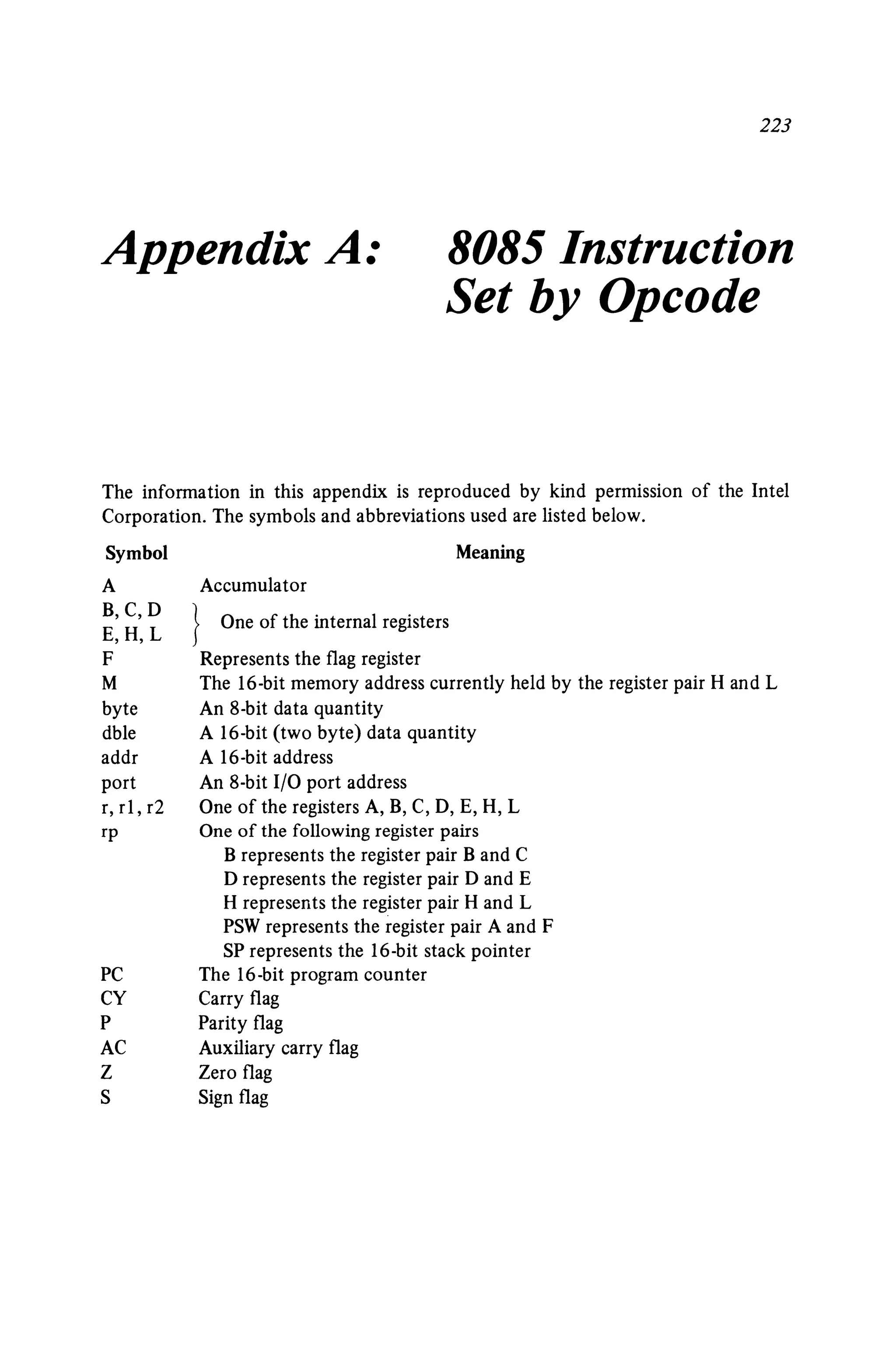

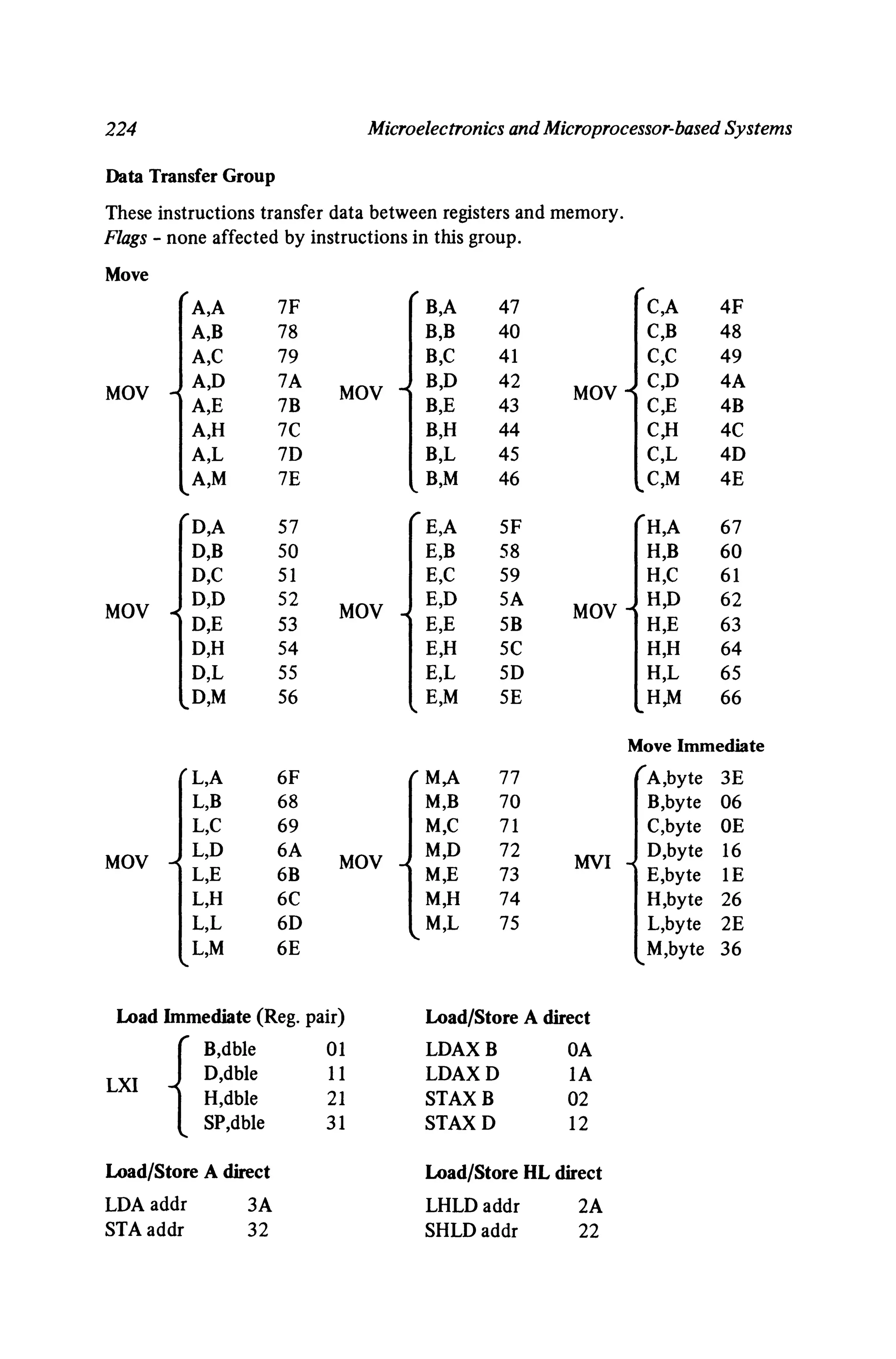

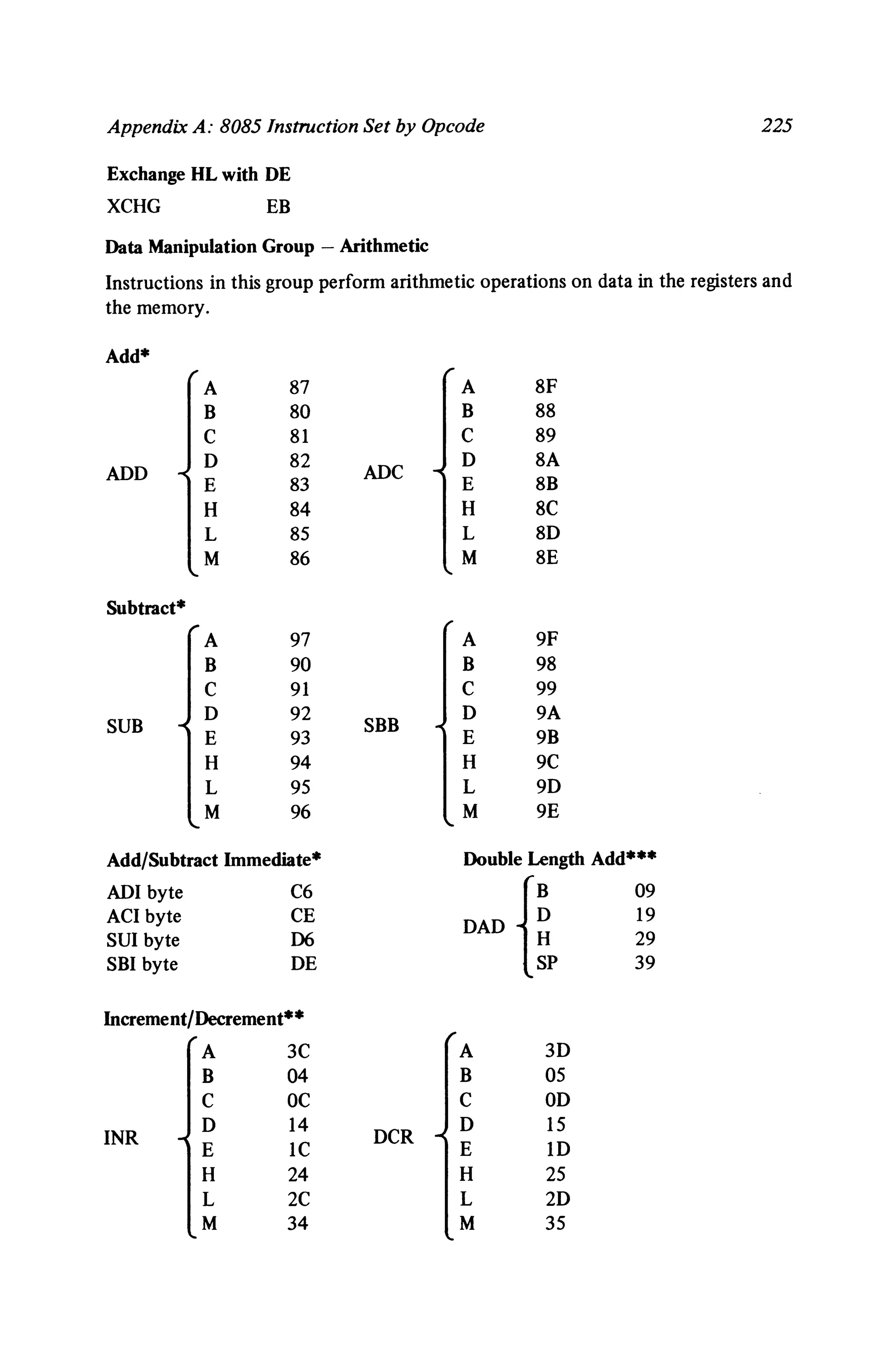

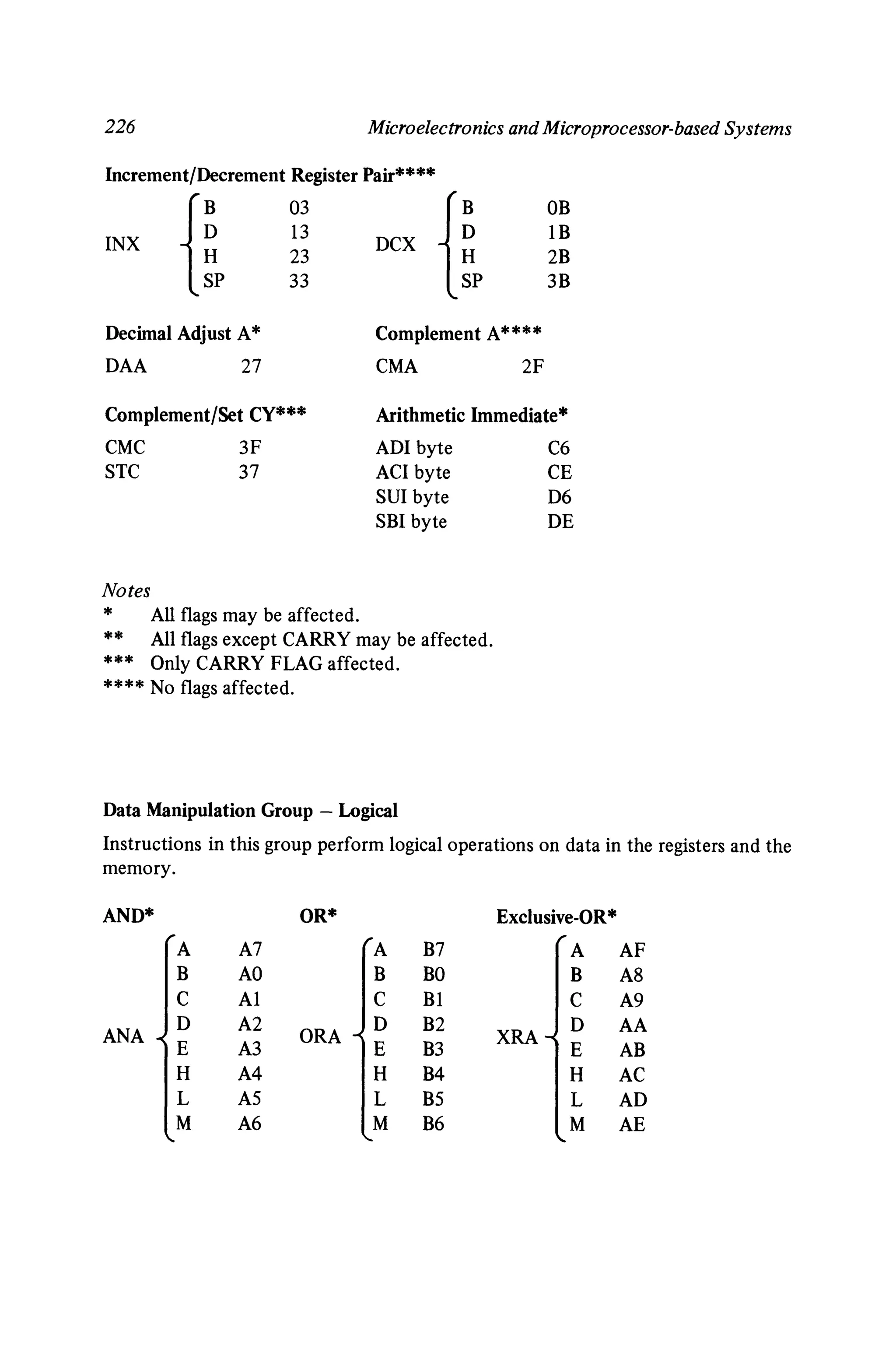

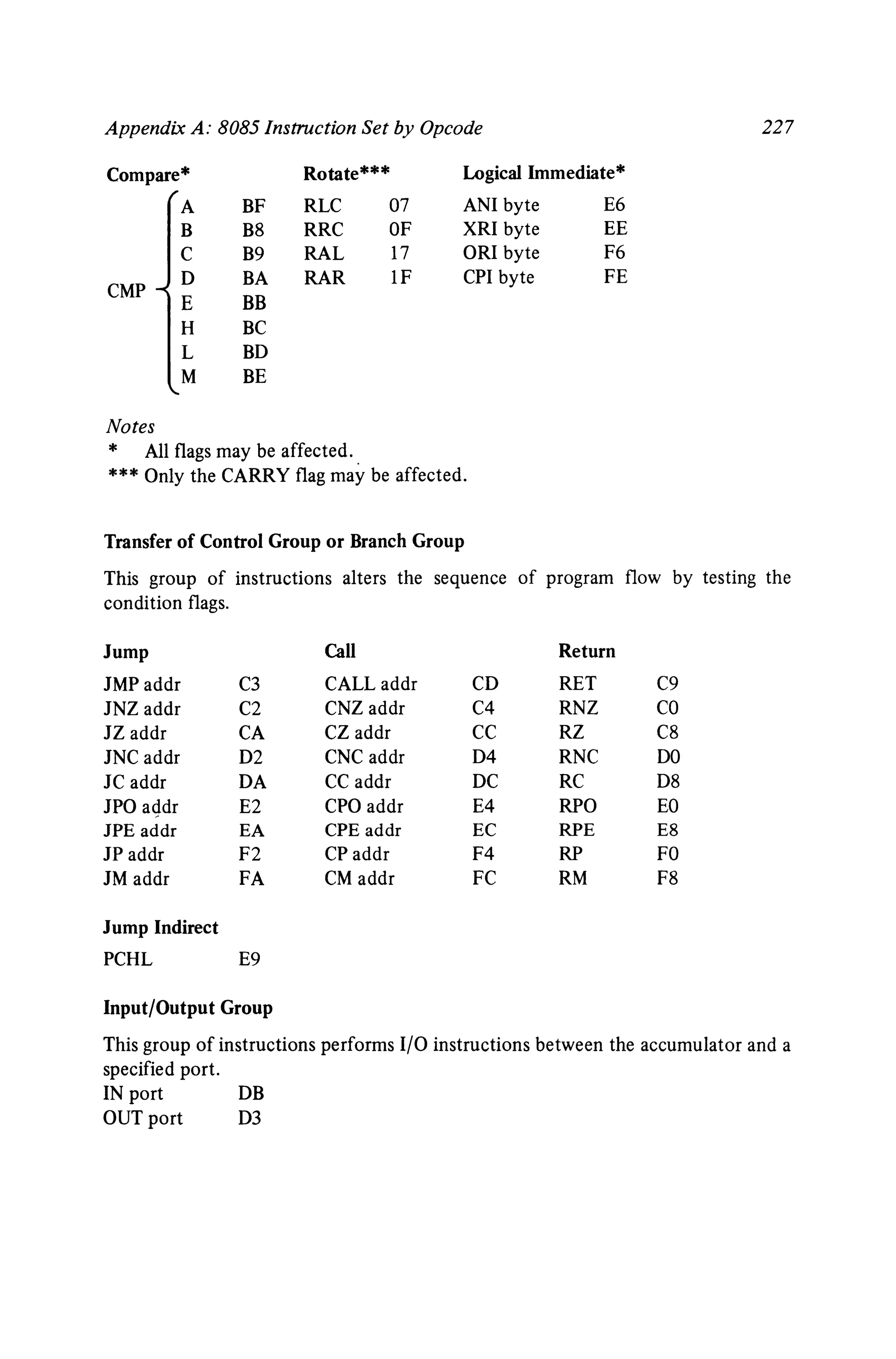

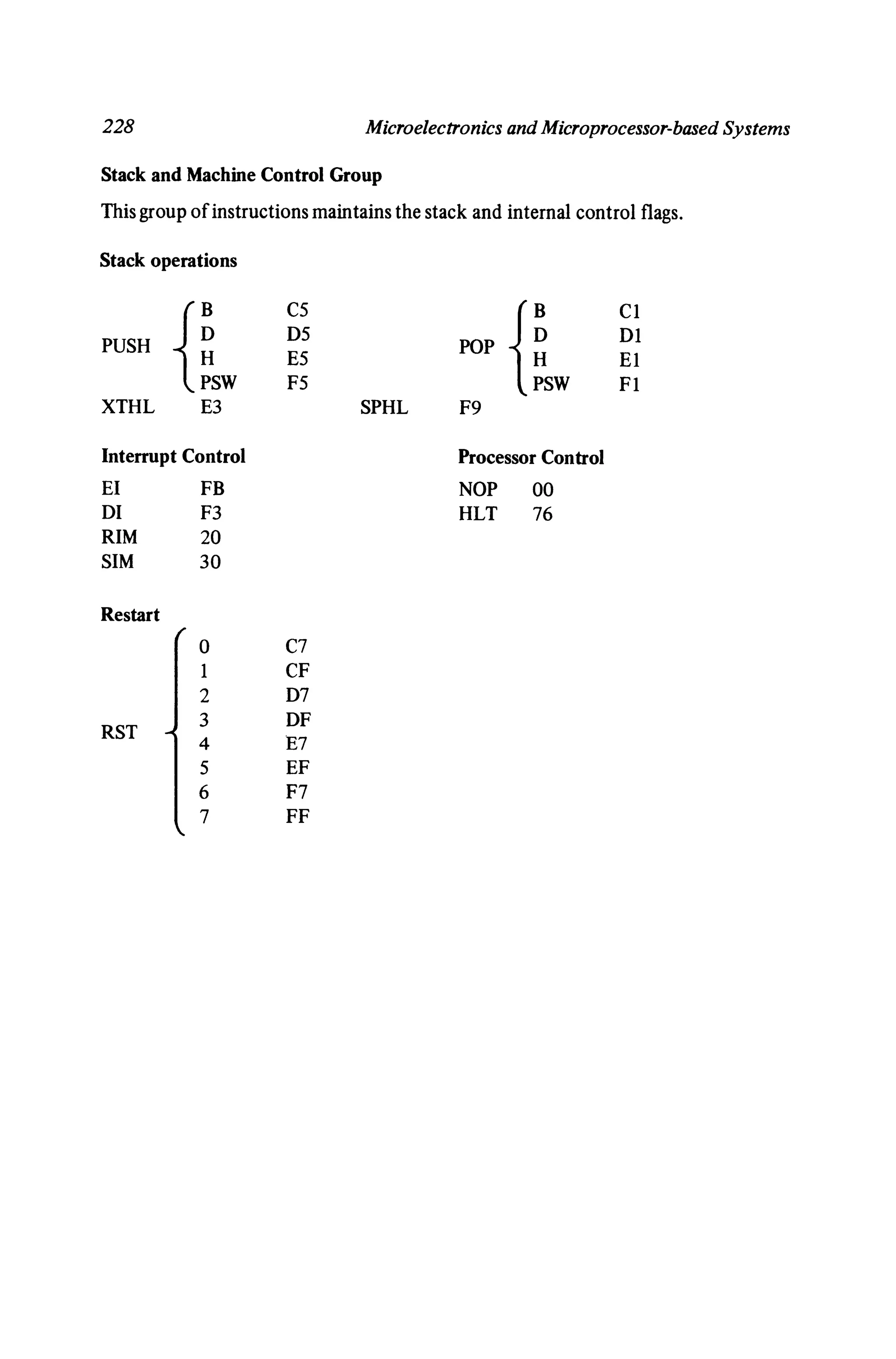

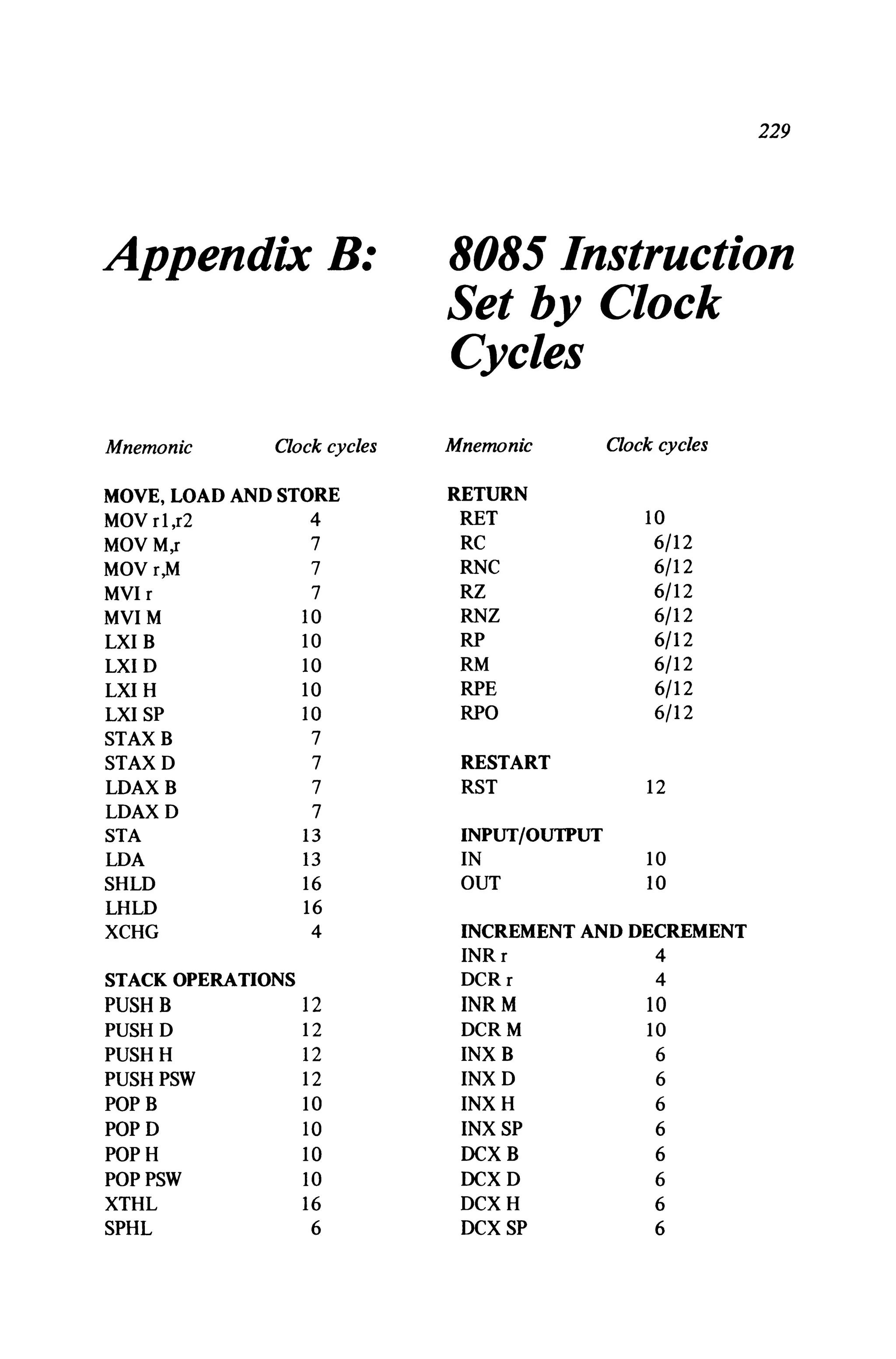

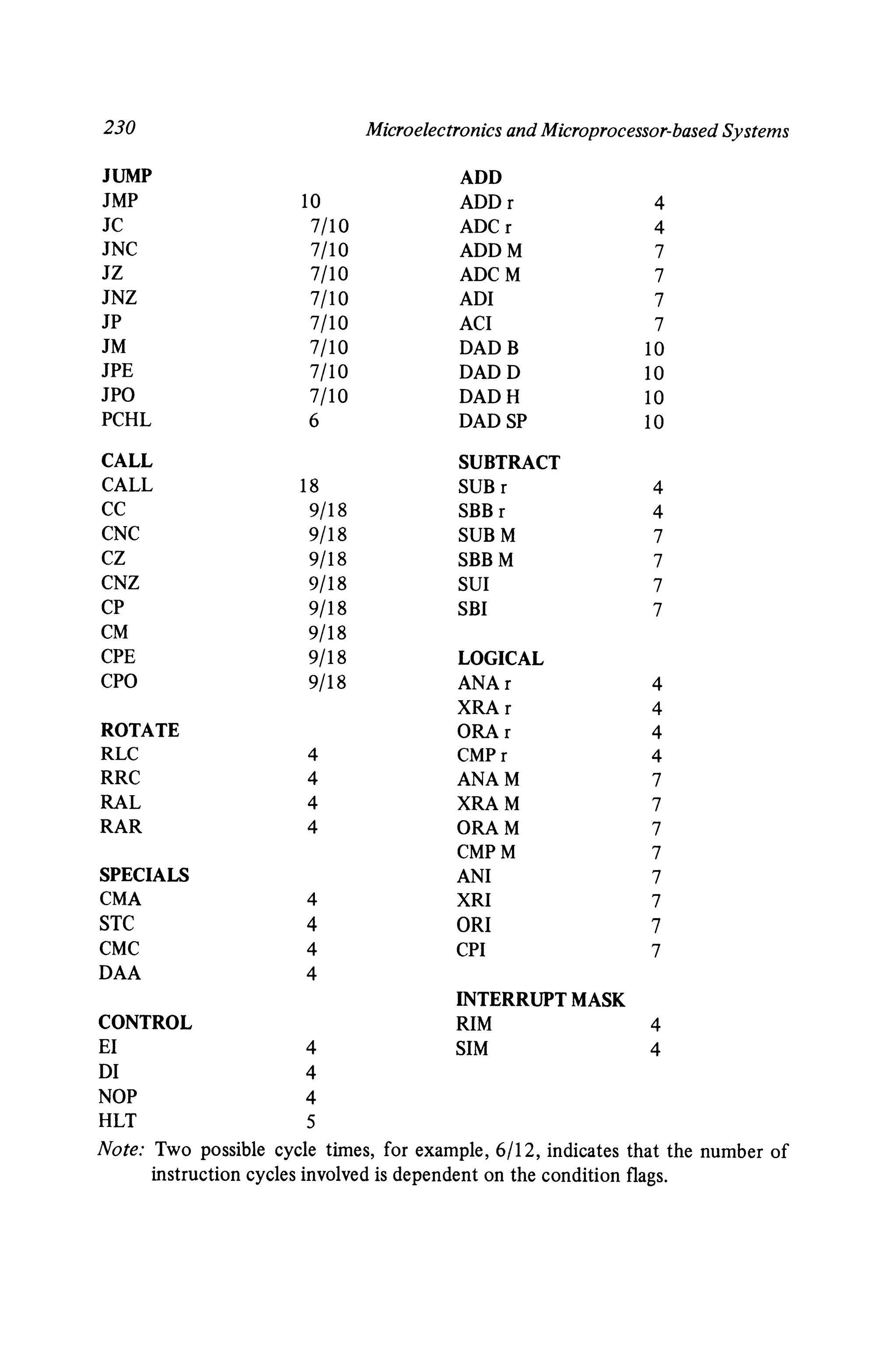

This document provides an appendix with information about the 8085 instruction set, including a table that lists each instruction opcode and a brief description. It includes sections on data transfer instructions, arithmetic instructions, logical instructions, branching instructions, I/O instructions, stack and machine control instructions, and interrupt control and processor control instructions. Tables are also provided that list the instruction set grouped by opcode and clock cycles.