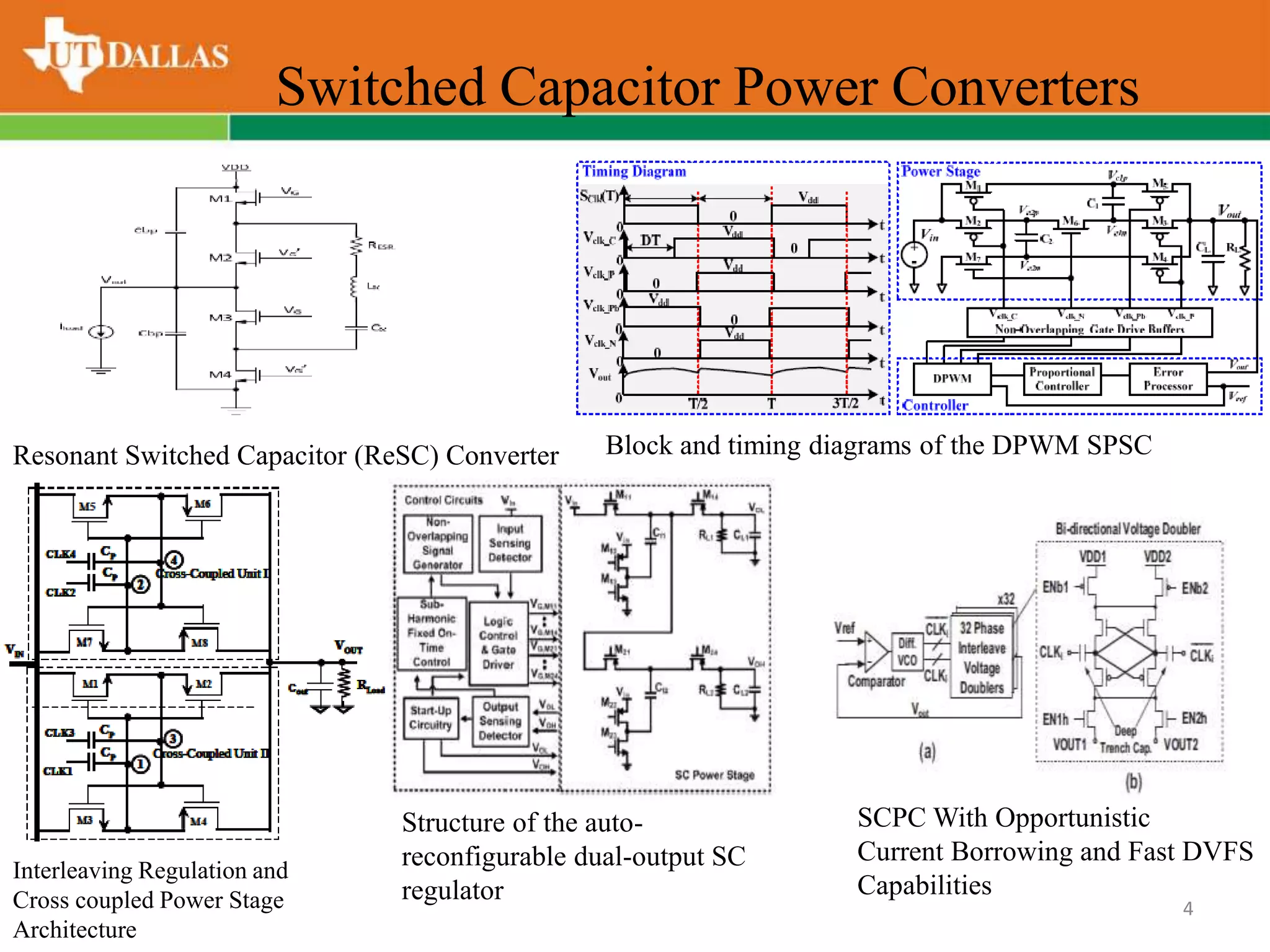

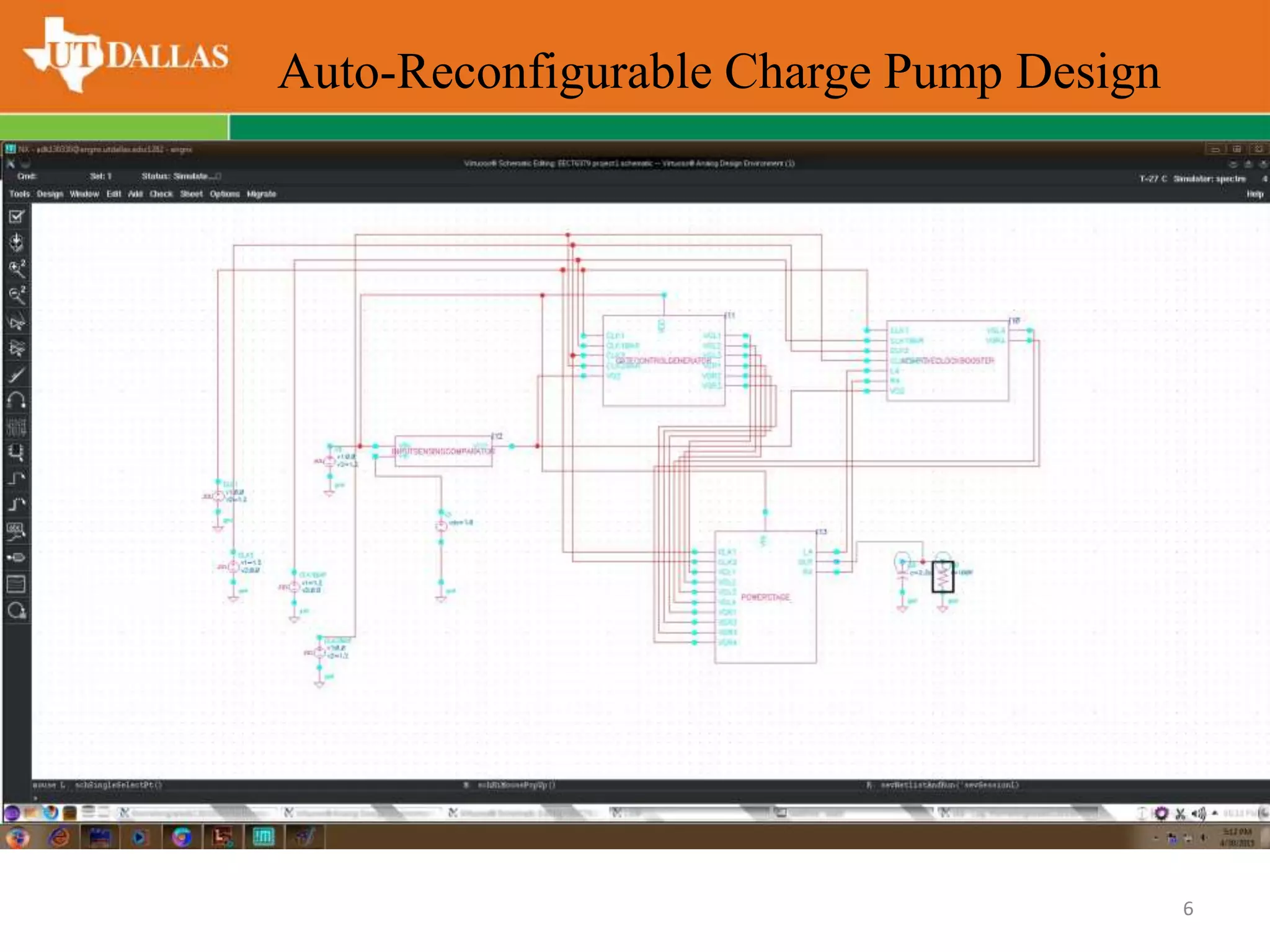

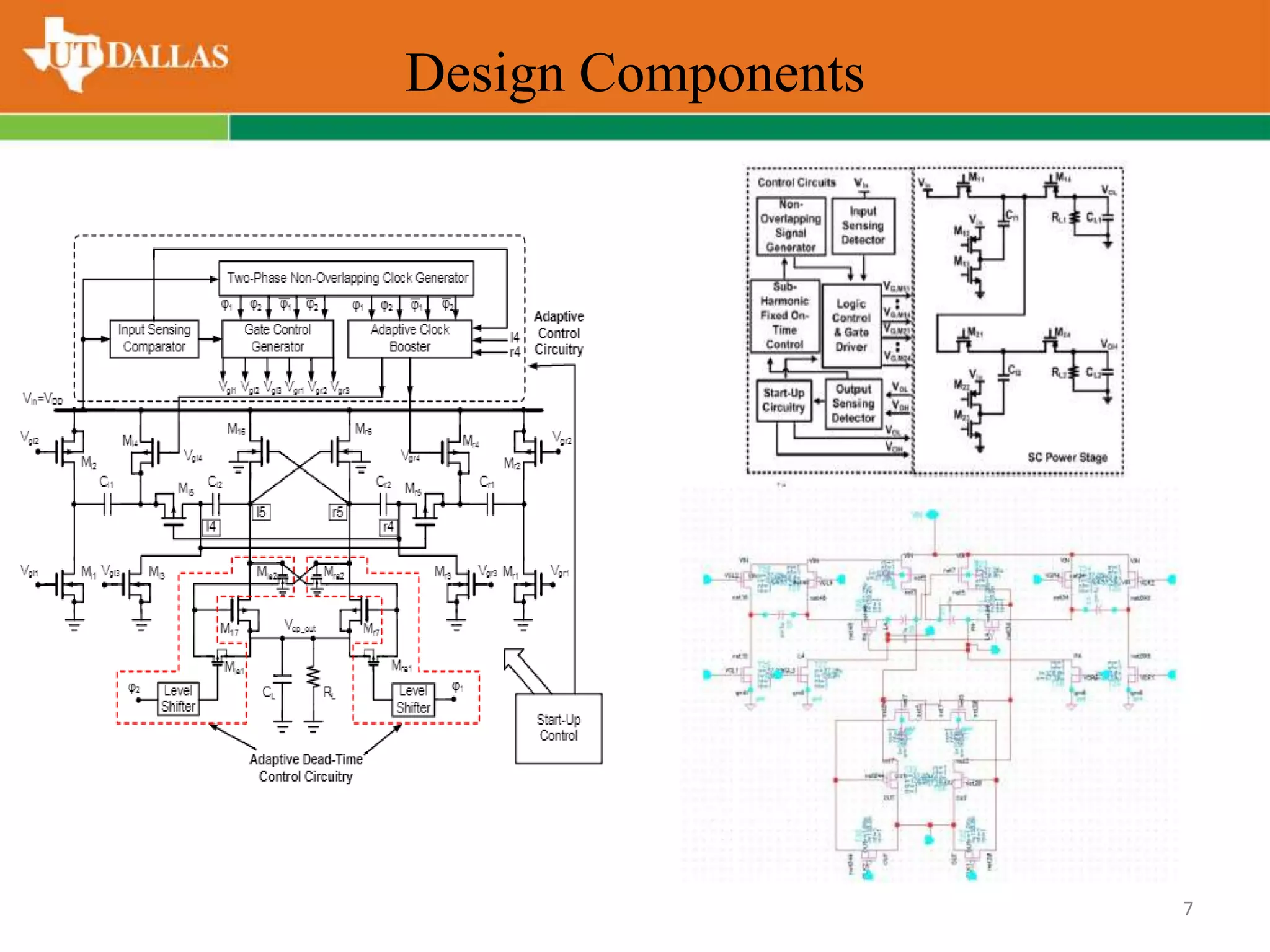

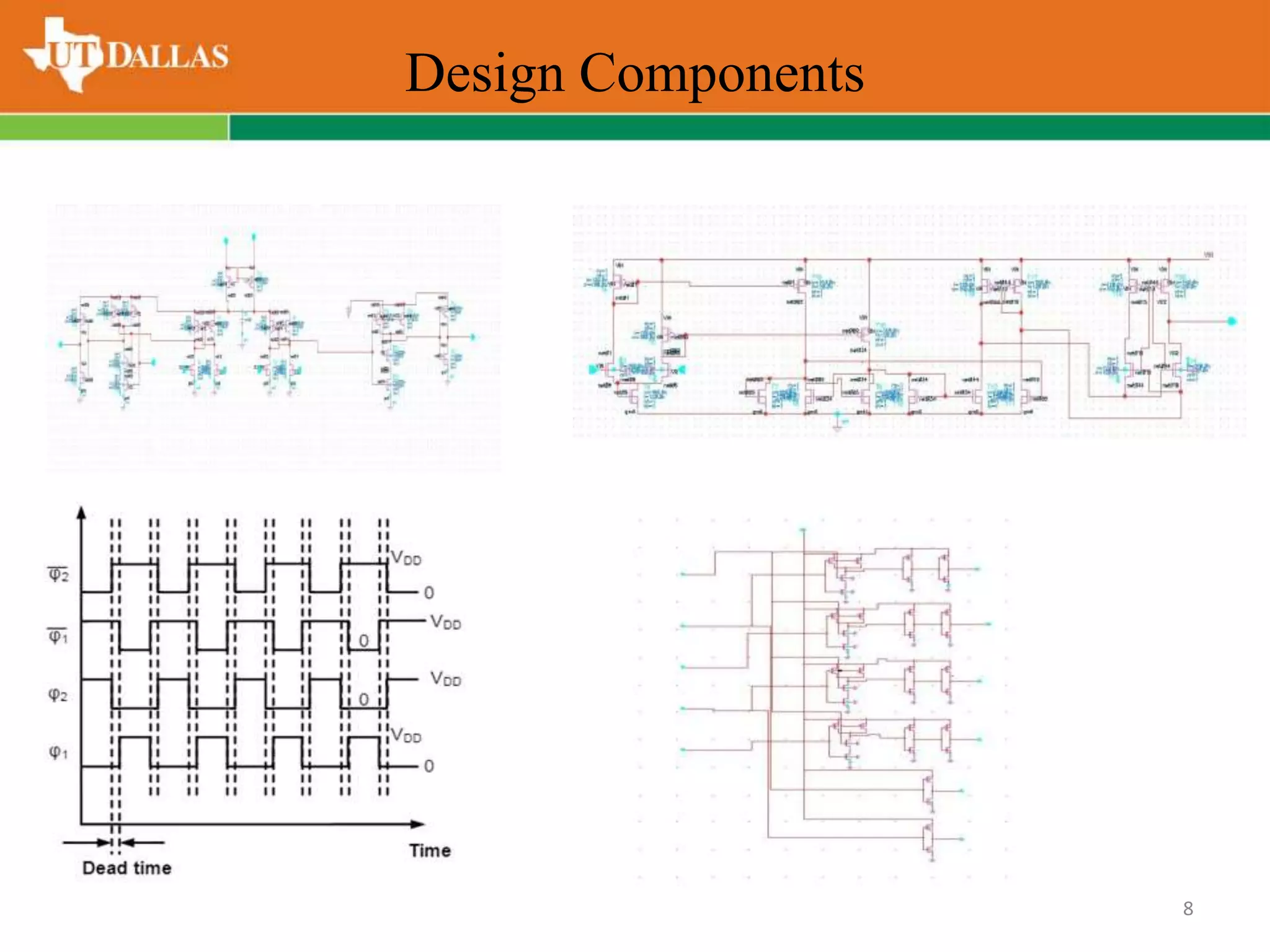

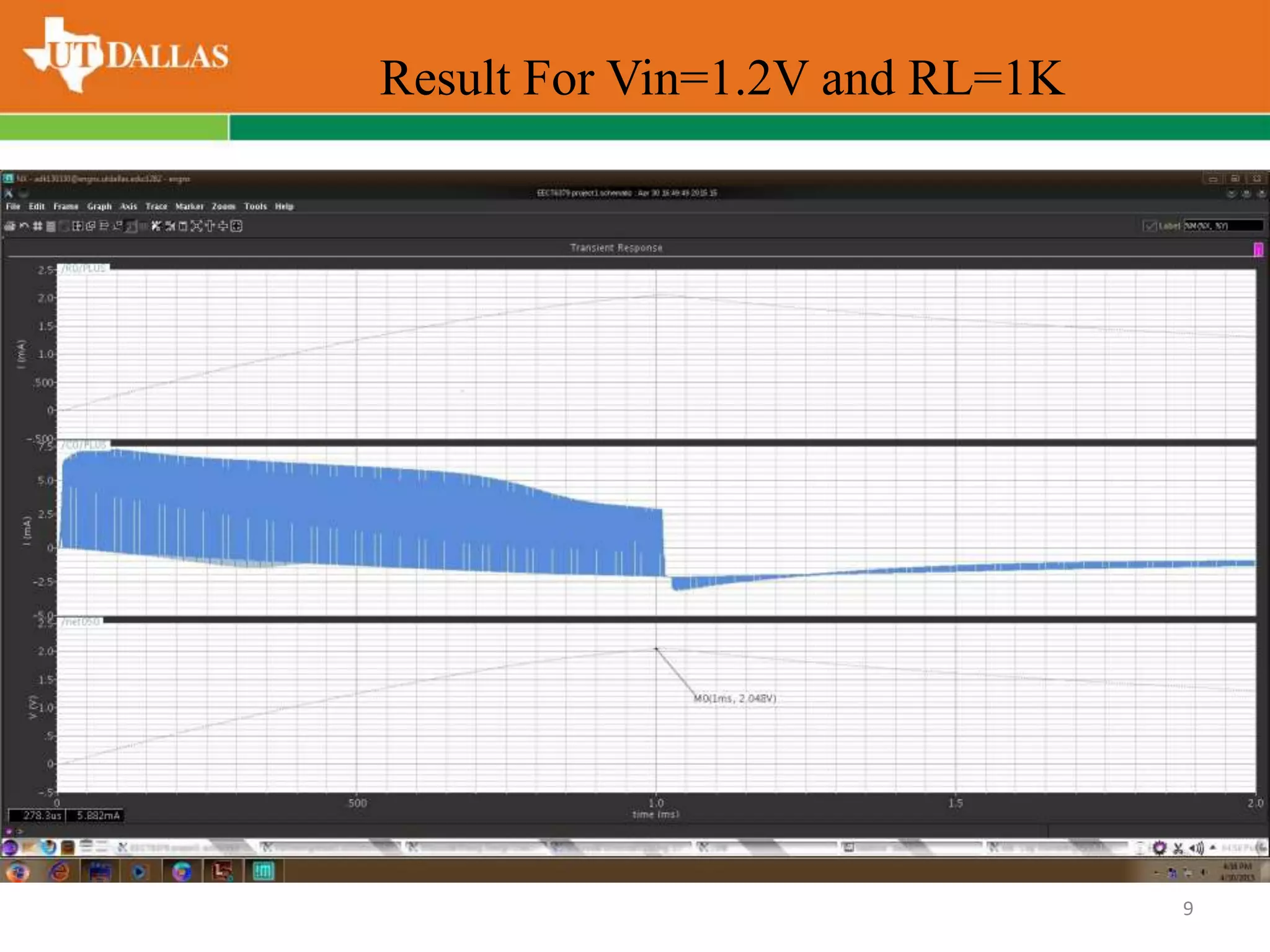

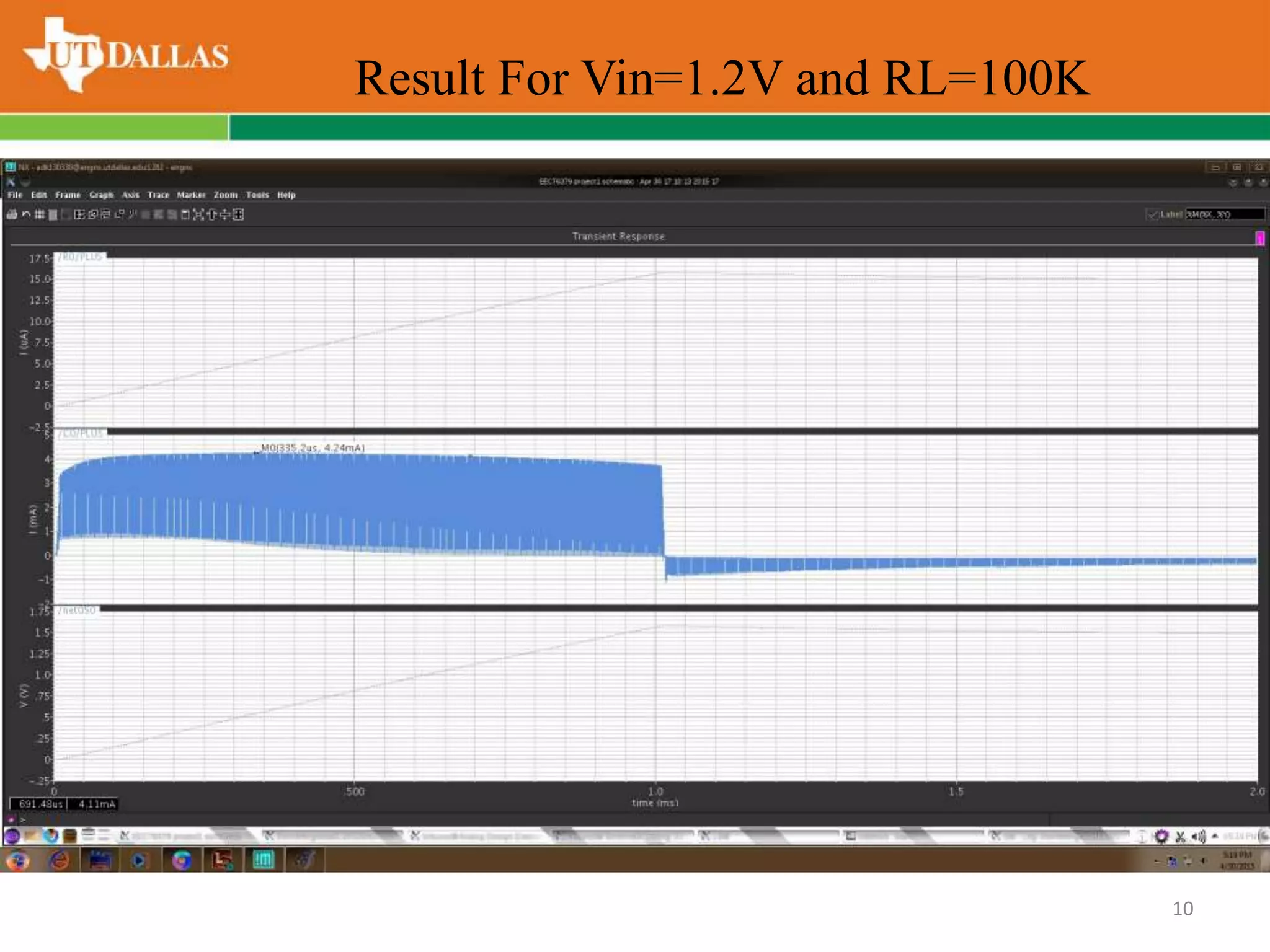

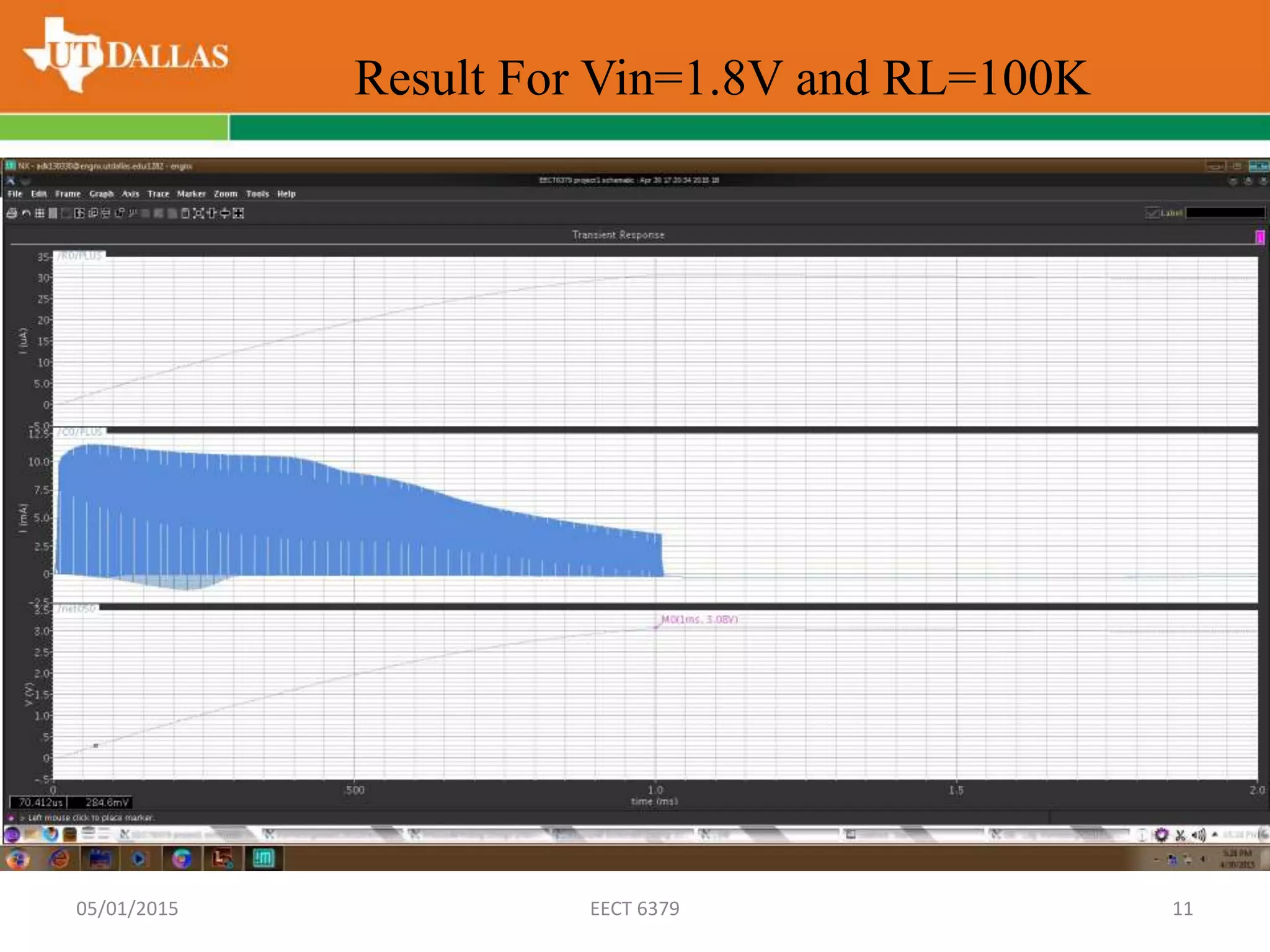

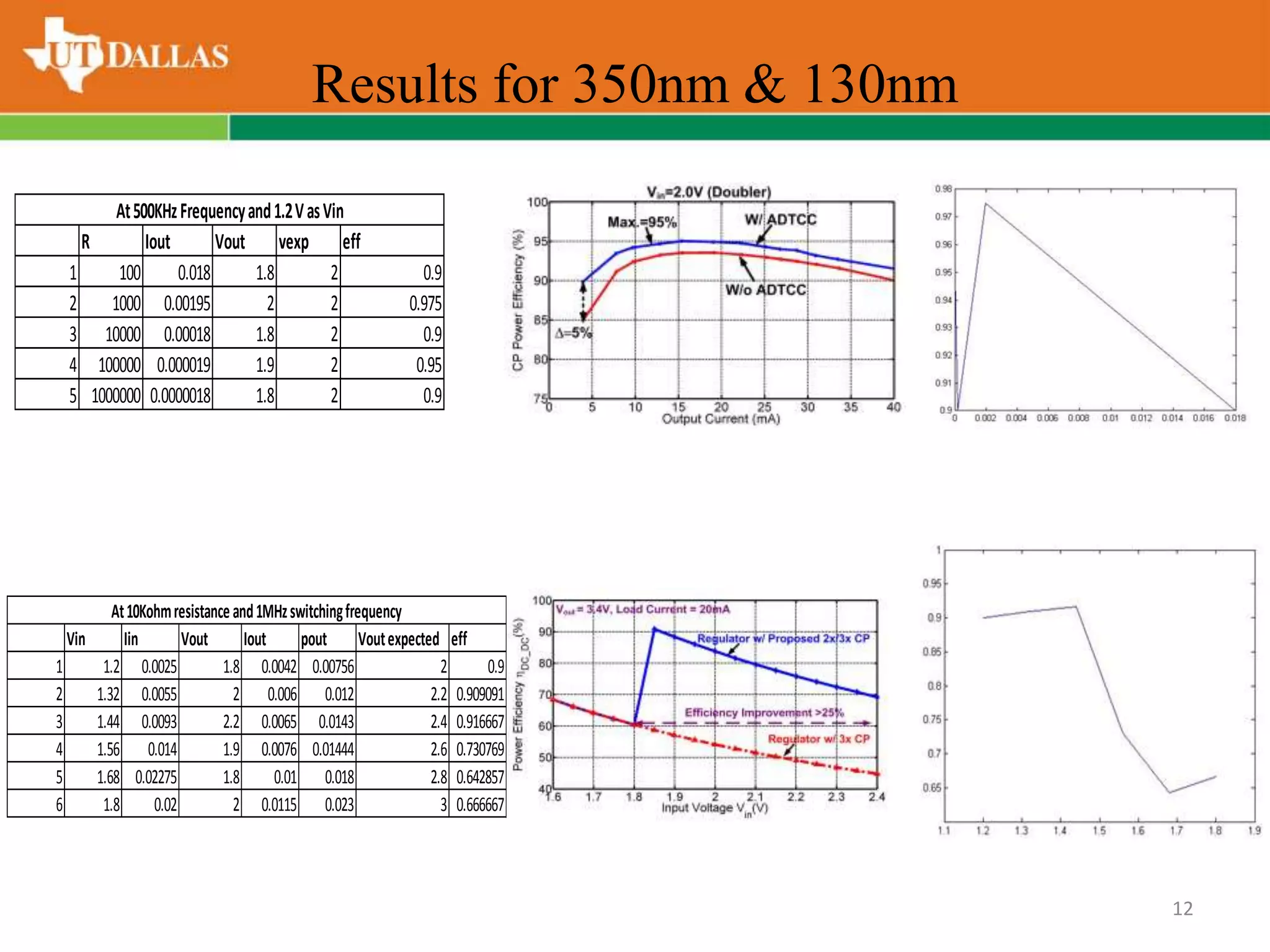

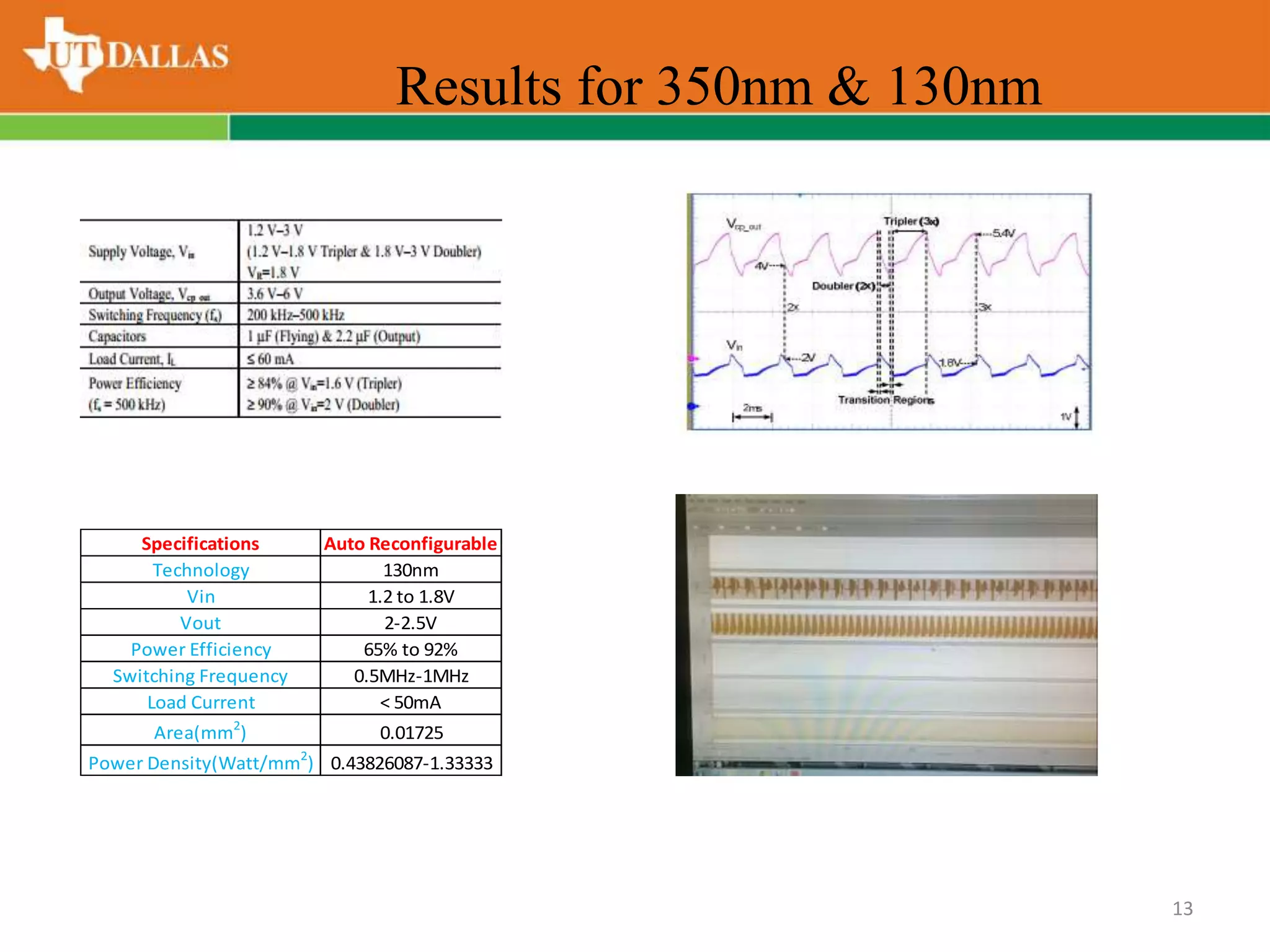

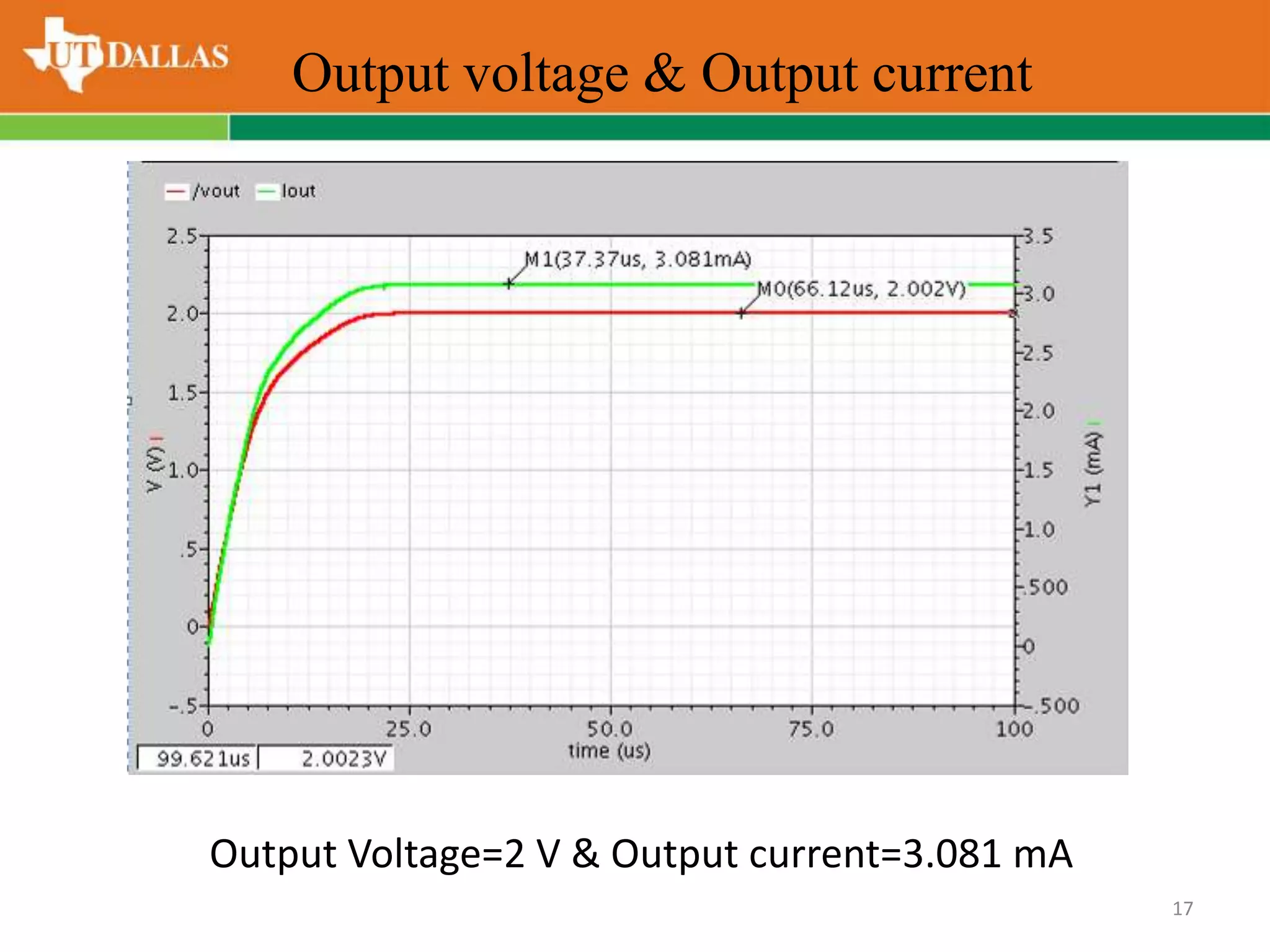

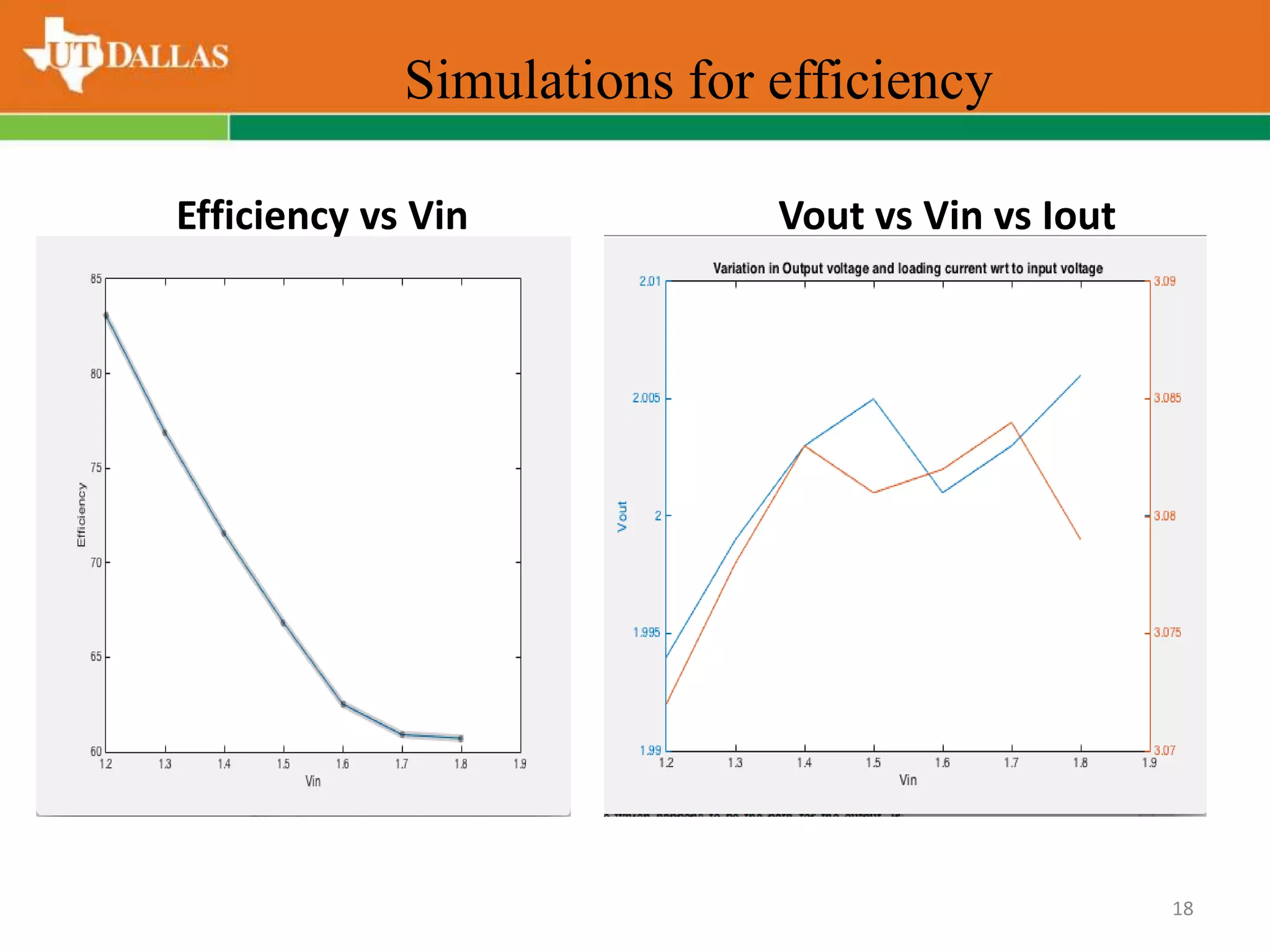

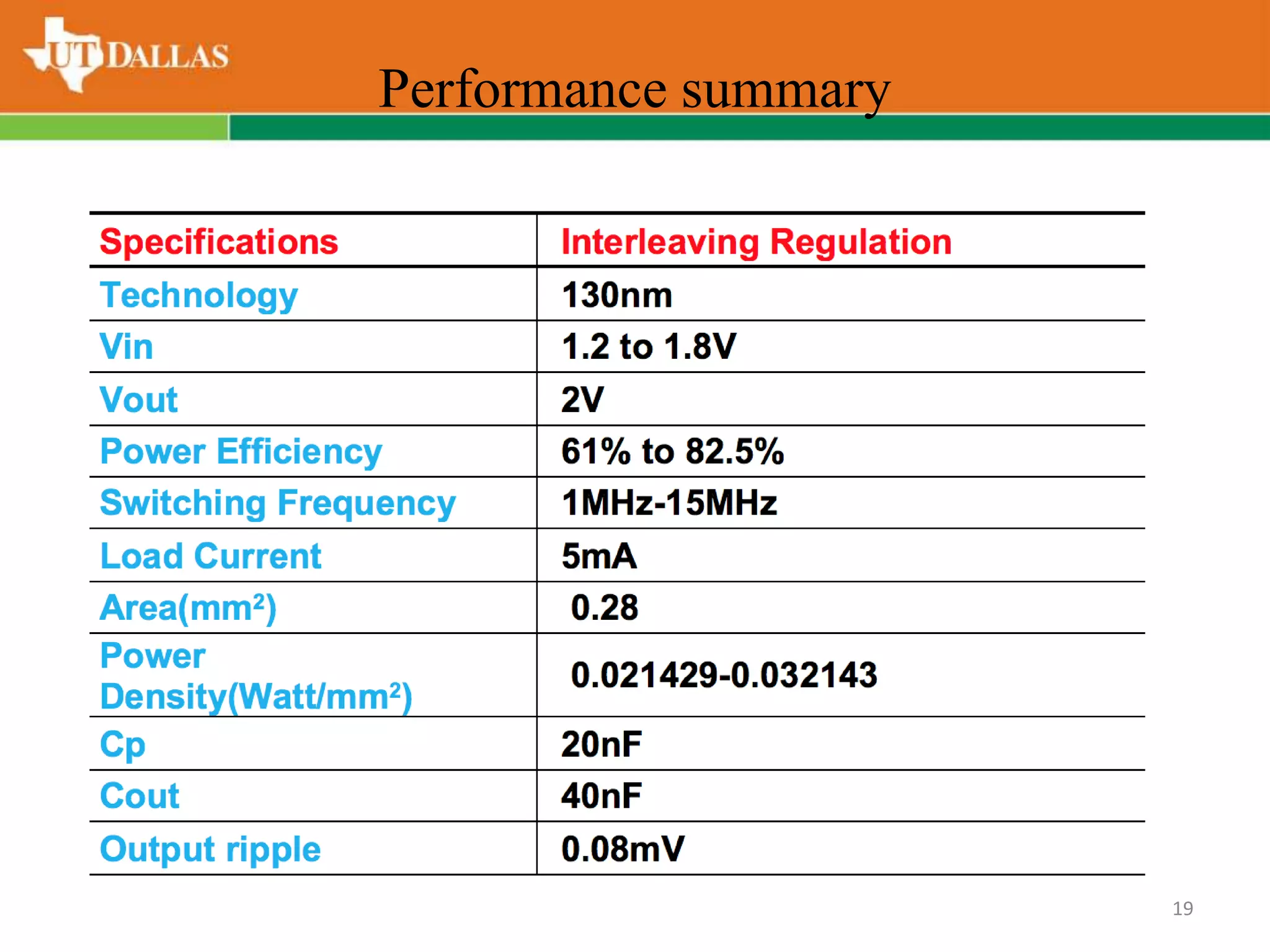

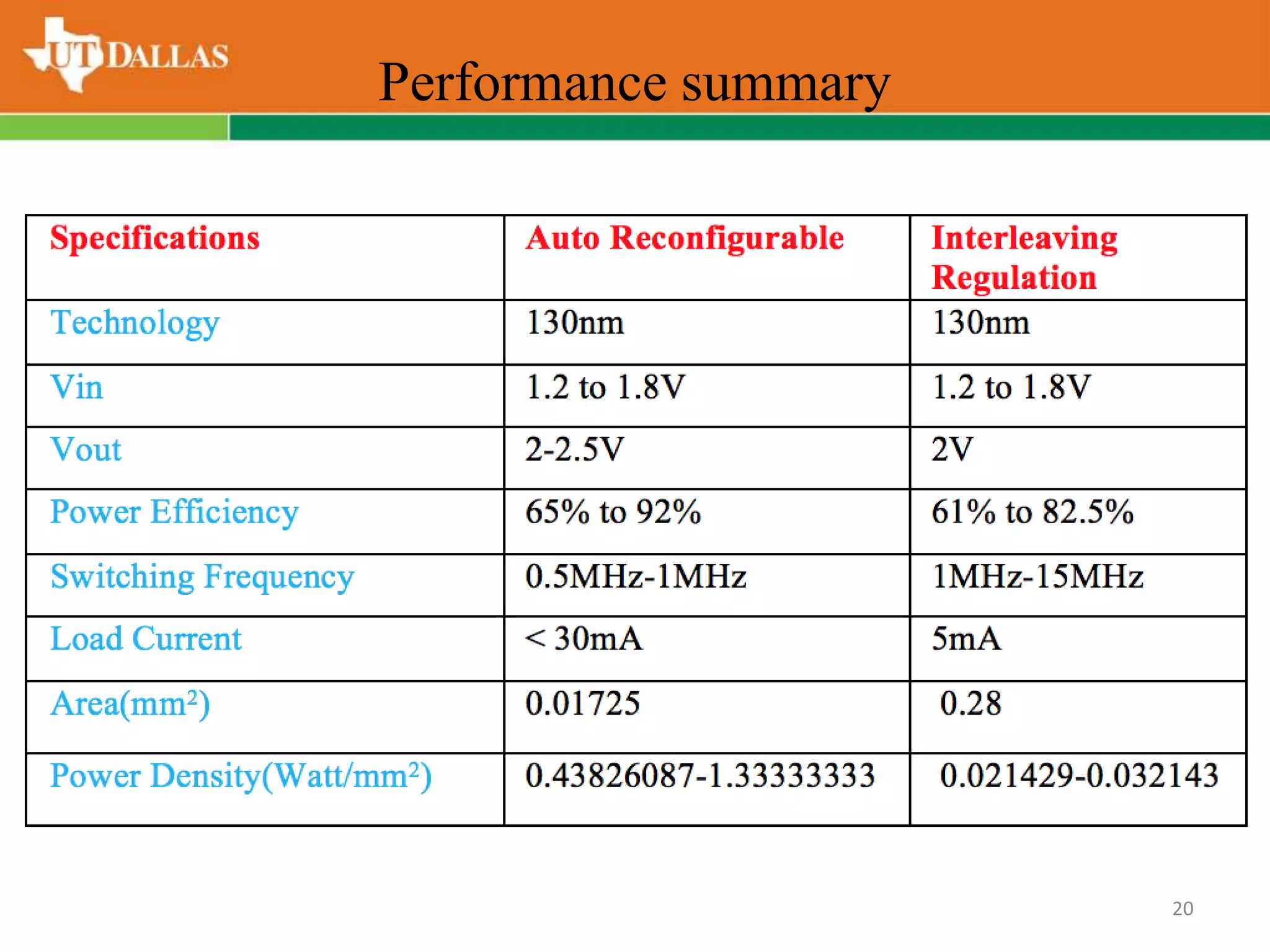

The document presents an analysis and characterization of high-density on-chip switched-capacitor power converters designed using 130nm technology. It focuses on the development of auto-reconfigurable converters, highlighting innovations in minimizing capacitor sizes while maximizing power delivery efficiency. Results demonstrate significant improvements in efficiency across varying input and load conditions, indicating promising applications for dynamic voltage frequency scaling.