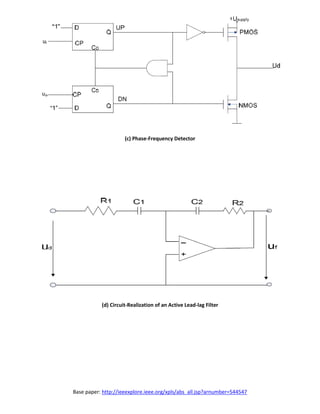

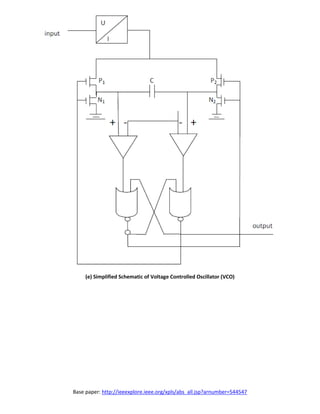

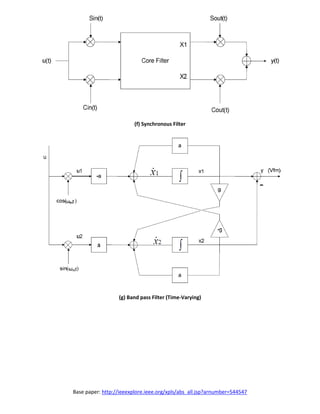

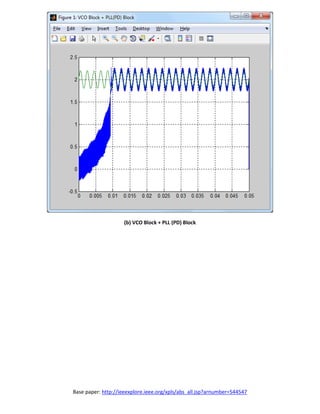

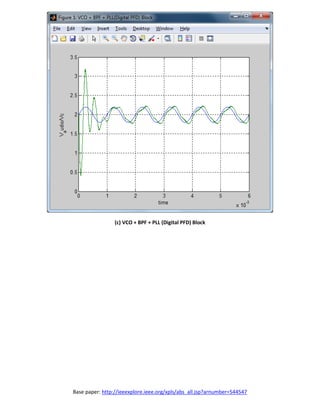

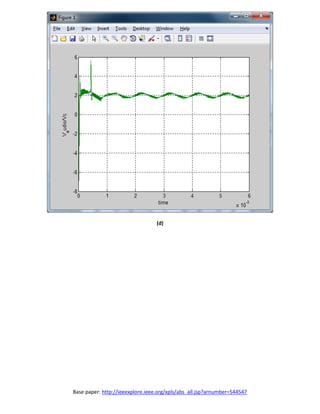

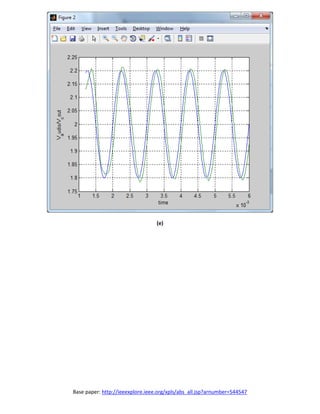

This document discusses the design and implementation of a phase-locked loop (PLL) frequency modulation (FM) demodulator. The key components of the demodulator are the PLL block and an optimum time-varying filter block. The PLL block contains three sub-blocks: a phase-frequency detector, loop filter, and voltage-controlled oscillator. Circuit diagrams and equations for these components are presented. Additionally, a bandpass filter is designed and integrated with the PLL block to improve FM signal quality by recovering the demodulated signal. Simulation results showed the demodulator successfully recovered the FM signal.