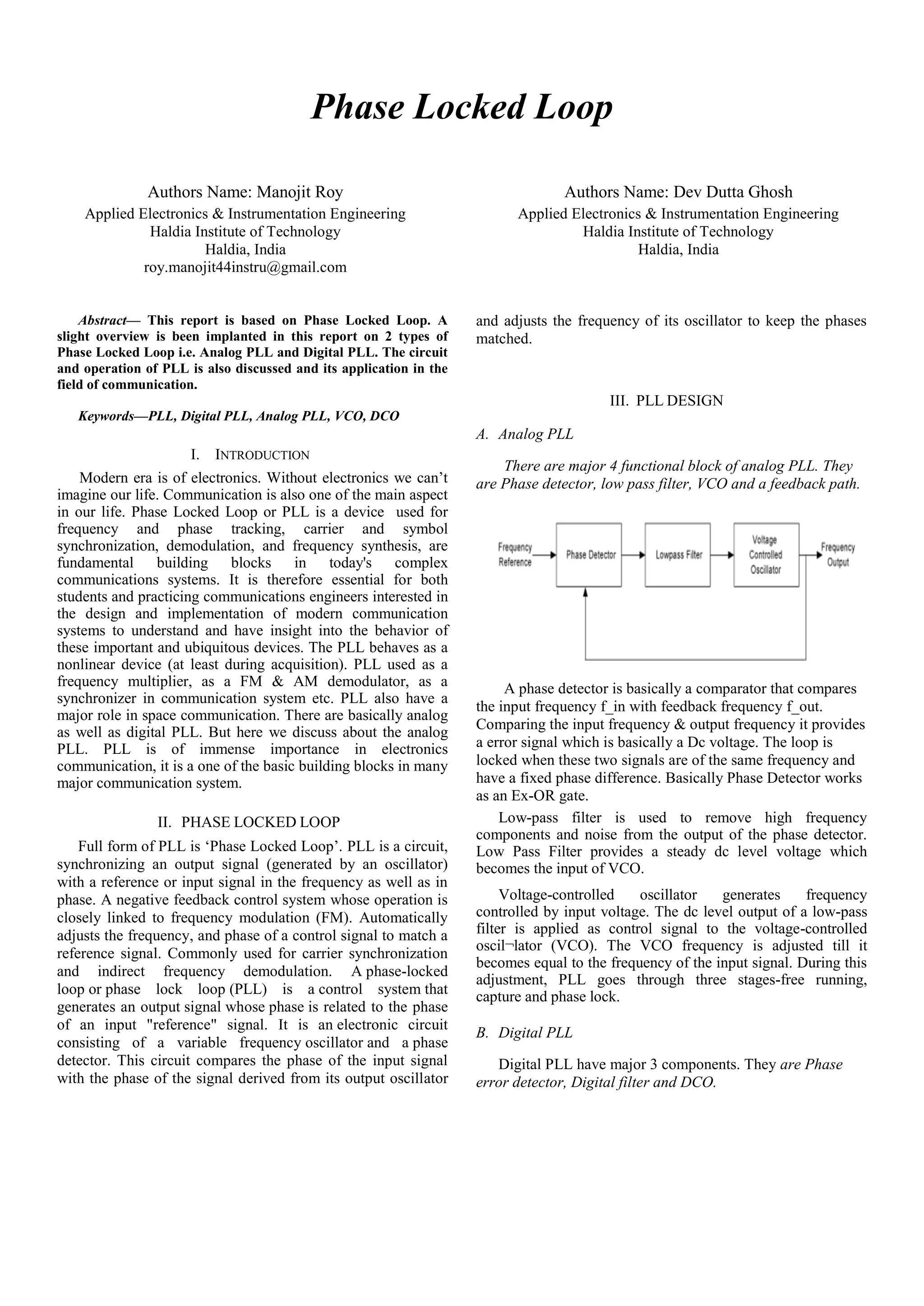

This document discusses phase locked loops (PLLs). It provides an overview of analog and digital PLLs. Analog PLLs have four main components: a phase detector, low pass filter, voltage controlled oscillator (VCO), and feedback path. Digital PLLs have three main components: a phase error detector, digital filter, and digitally controlled oscillator (DCO). The document also describes the three stages of PLL operation: free running, capture, and phase locked. PLLs are important for applications such as frequency synthesis, carrier synchronization, and demodulation in communication systems.

![Counter - starts counting on the positive-going edge of the

flip-flop waveform. The content of the counter, No, which is

proportional to the phase error, is applied to digital filter. The

output of the digital filter K controls the period of the DCO.

DCO - programmable divide-by-K counter.

IV. PLL OPERATION

A. Free Running Stage

When no input is applied at the phase detector, then due to

VCO, PLL works in Free Running Stage. The output

frequency of this stage is dependent on the free running

frequency of VCO.

B. Capture Stage

When a input frequency is applied at the phase detector,

then due to feedback mechanism PLL tries to track the output

with respect to input. This stage is called Capture Stage.

C. Phase Locked State

Due to feedback mechanism, the frequency comparison

stops as soon as the output frequency become equal to the

input frequency. This stage is called Phase Locked State.

ACKNOWLEDGMENT

Apart from the efforts of myself, the success of any project

depends largely on the encouragement and guidelines of many

others. I take this opportunity to express my gratitude to the

people who have been helpful in the successful completion of

this report. I want to express my gratitude to all the people

who have given their heart whelming support to finish this

report. I would like to thanks whole Applied Electronics &

Instrumentation Department for their support.

REFERENCES

[1] Mao Lai and Michino Nakano, “ Special Section on Phase Locked Loop

Techniques”, Guest Editorial, IEEE Transactions on Industrial

Electronics,Vol 43, No 6, December 1996.

[2] Guan Chyun Hsich and James C Hung, “Phase Locked Loop Techniques

–A Survey”, IEEE Transactions on Industrial Electronics, Vol 43, No 6,

December 1996.

[3] F.M Gardner, “Phase Locked Loop Techniques”, 2nd edition; New

York; Wiley 1979

[4] William C Lindsey and Chak Chie, “ A survey of Digital Phase Locked

Loops”, Procedings of the IEEE, vol 69, No 4, April 1981

[5] Silicon Laboratories, “Introduction to FPGA based ADPLL”, rev

0.13/11, An 575, 2011

[6] R.E Best, “Phase Locked loops, theory Design and Applications”, New

York; Mc Graw Hill, 1993, 2nd edition.

[7] J R Cessna, “Digital phase locked loops with sequential loop filters. A

case for coarse quantization”, In proc. Int. Telemetering Conf; vol VIII,

pp 136-148, October 1972

[8] A Yamamoto and S Mori, “ Performance of a binary quantized all digital

phase locked loop with a new class of sequential filter”, IEEE

Transactions on Information Theory, Vol IT-18, pp 488-493, July 1972

[9] Liangge Xu, Saaka Lindfors, Kari Stadius and Jussi Ryynanen, “ A

2.4GHz low power all digital phase locked loop”, IEEE Transactions on

solid state circuits, Vol 45, No 8, August 2010.](https://image.slidesharecdn.com/pllieee-160531193134/85/Pll-ieee-Format-2-320.jpg)