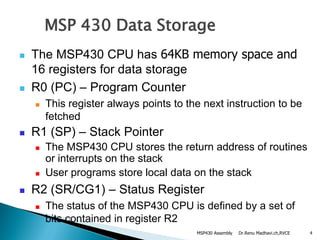

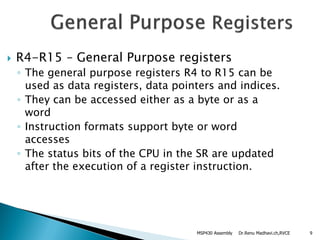

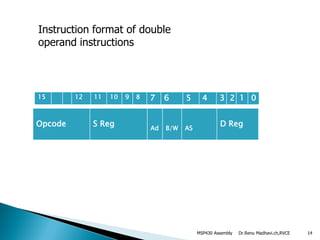

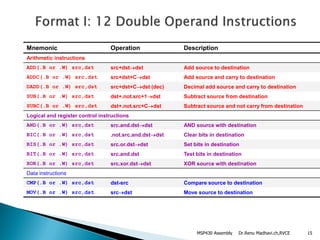

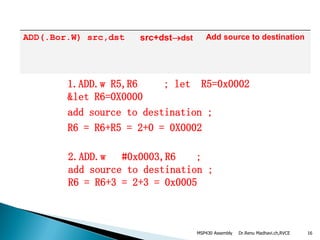

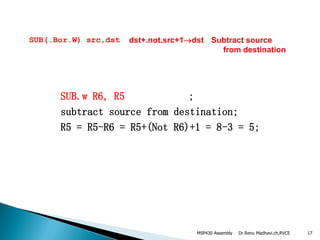

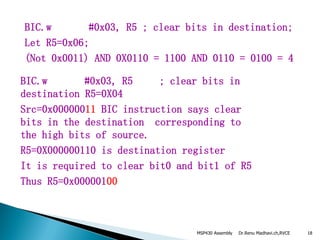

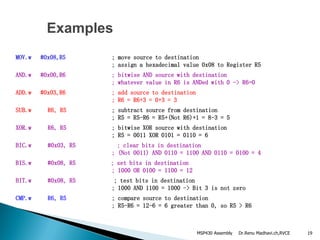

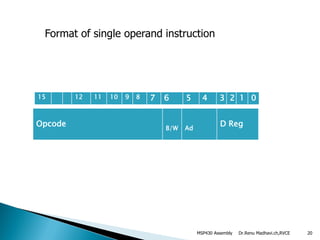

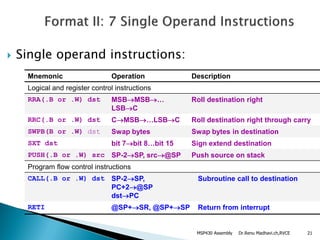

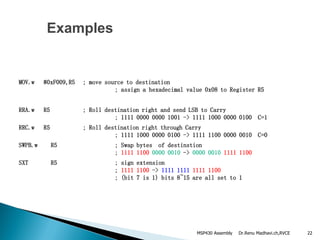

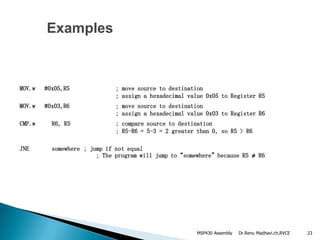

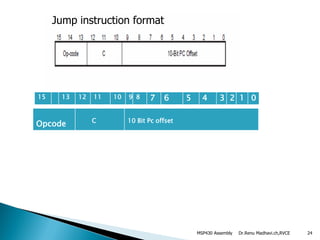

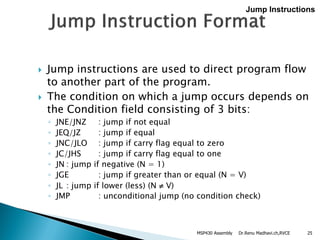

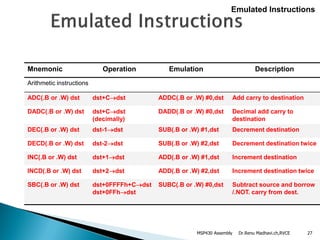

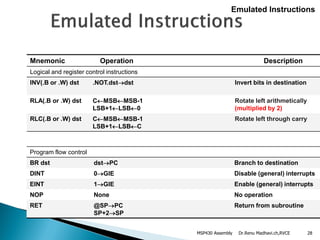

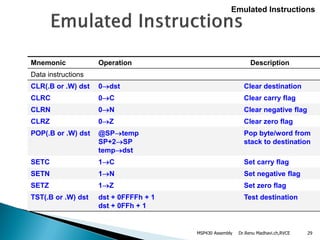

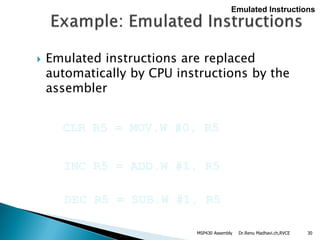

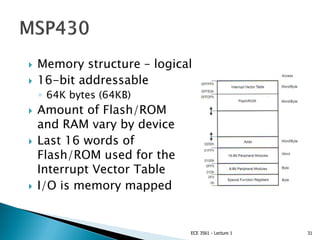

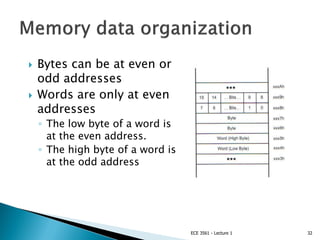

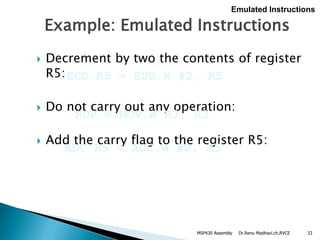

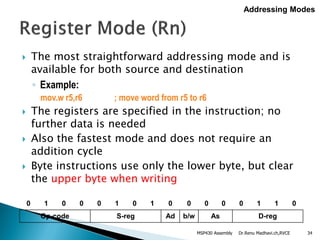

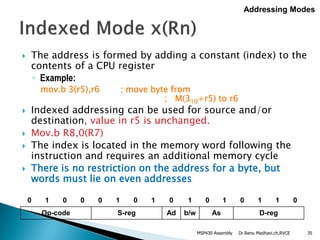

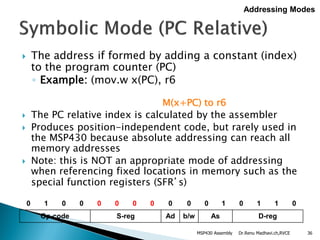

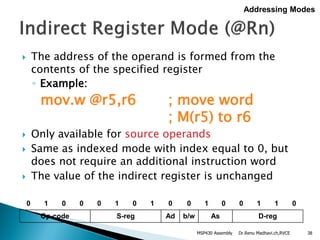

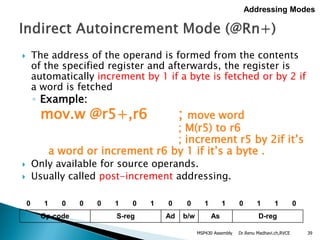

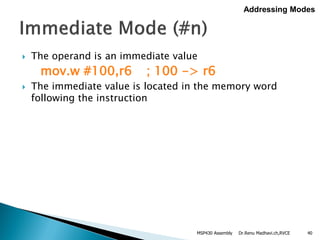

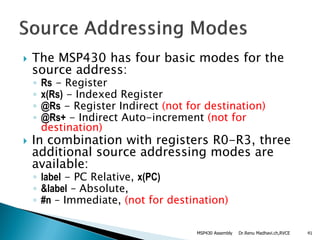

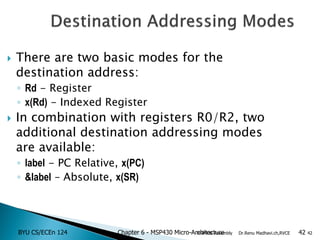

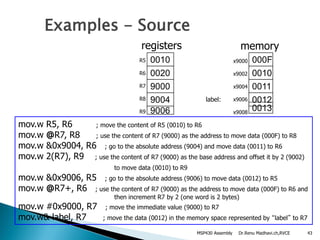

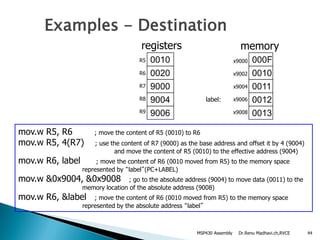

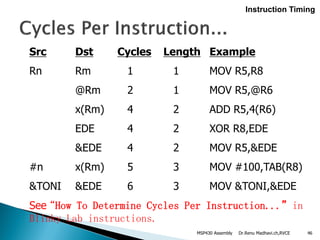

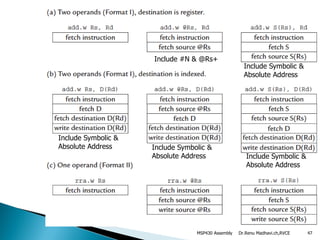

The document discusses MSP430 assembly language. It covers topics like MSP430 data storage in registers, double operand instructions, single operand instructions, jump instructions, and emulated instructions. Examples of various instructions like ADD, SUB, BIC, MOV, CALL etc. are provided. It also discusses MSP430 memory structure and explains that words are only stored at even addresses with the low byte at the even address and high byte at the next odd address.