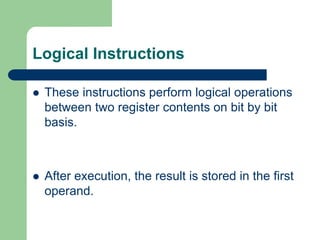

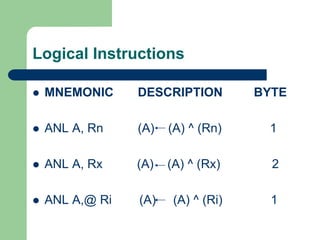

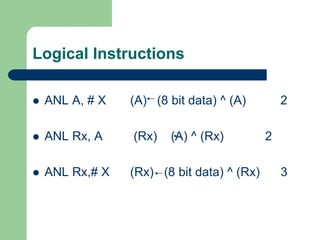

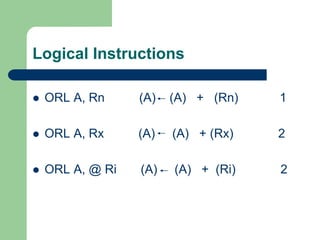

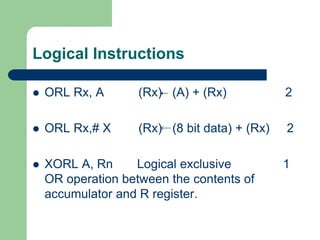

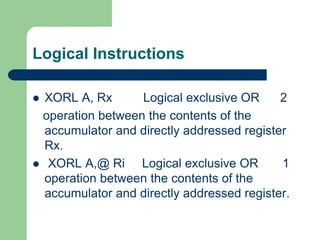

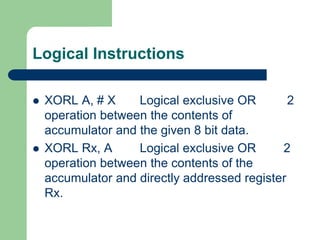

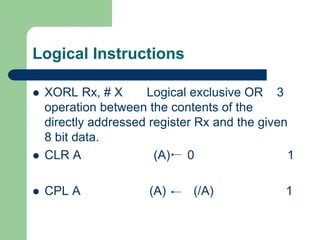

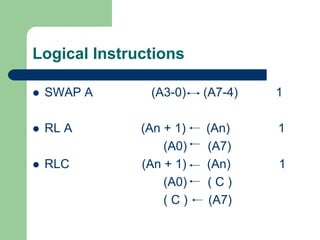

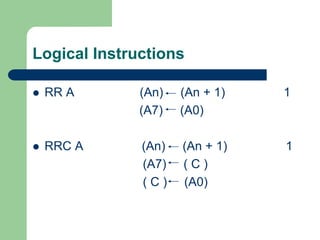

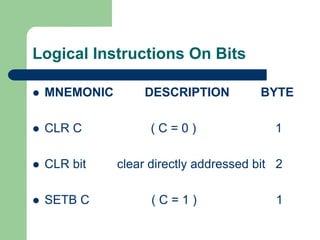

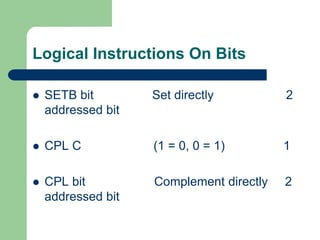

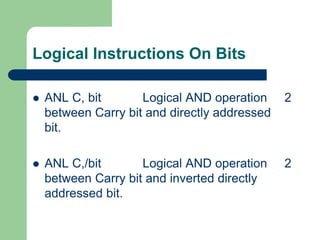

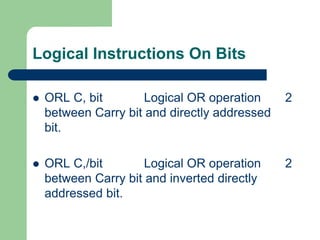

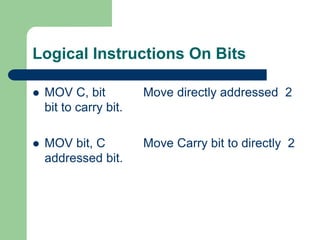

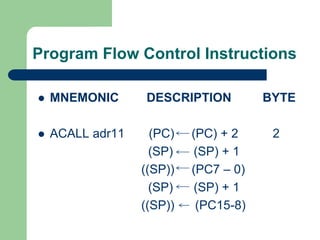

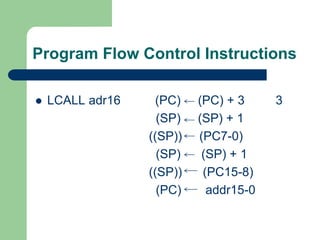

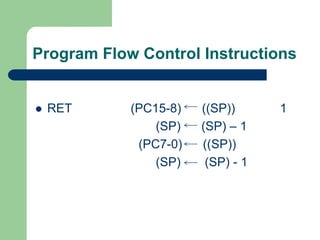

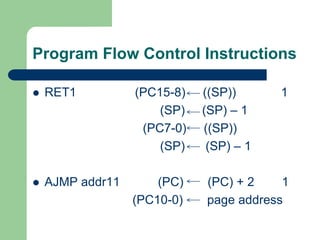

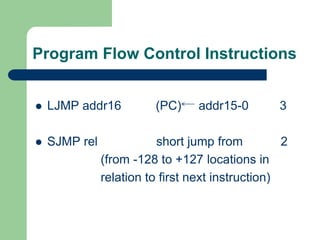

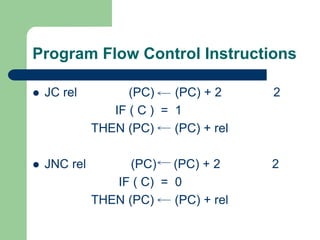

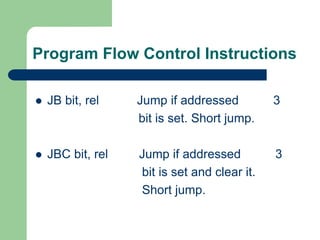

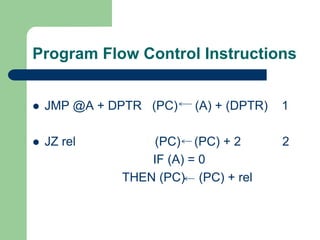

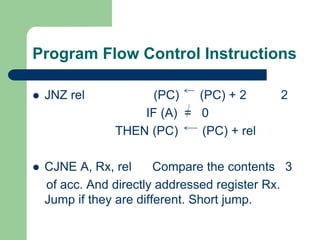

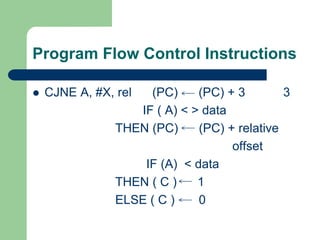

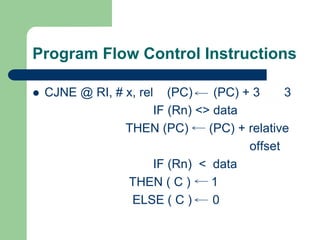

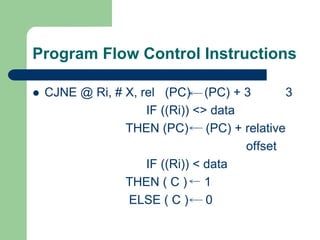

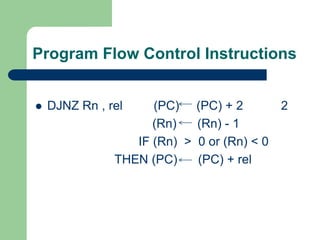

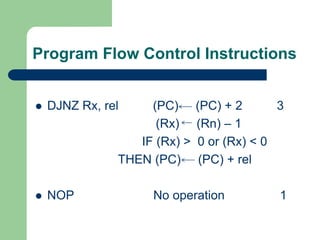

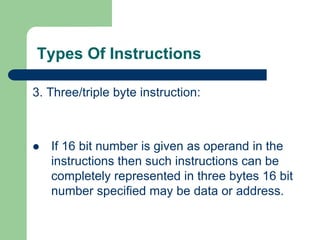

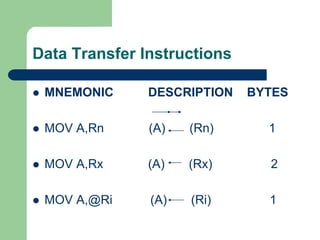

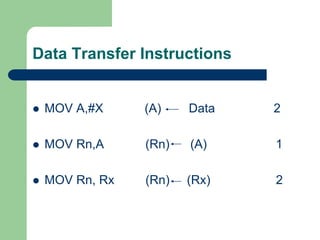

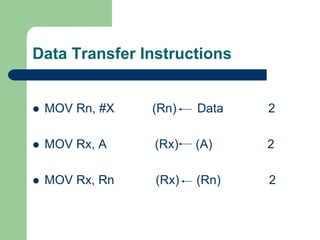

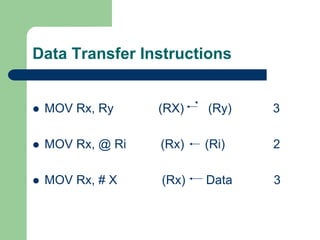

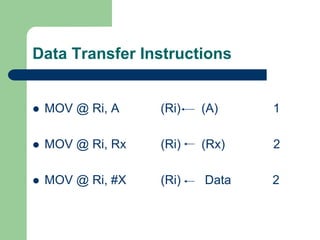

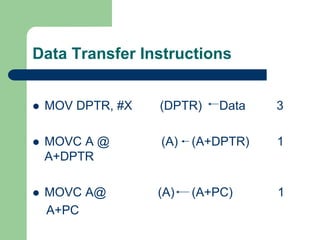

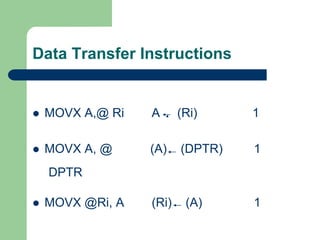

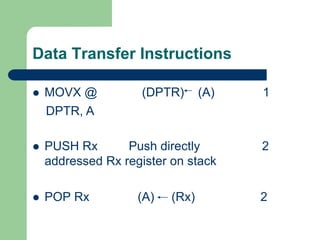

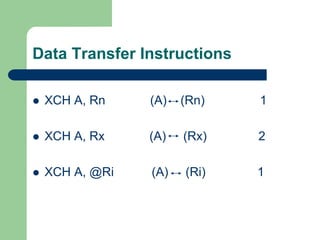

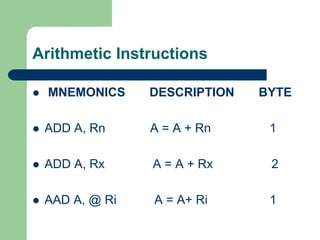

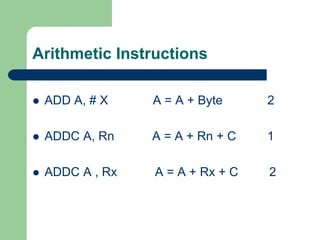

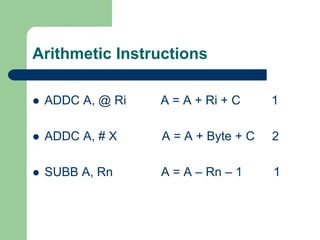

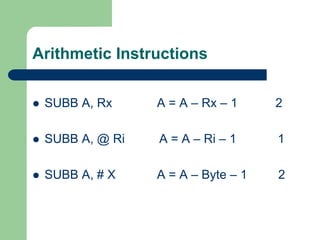

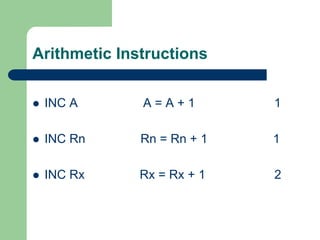

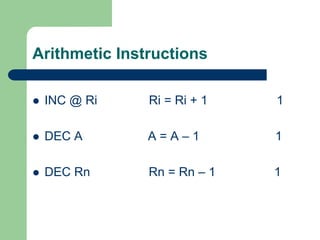

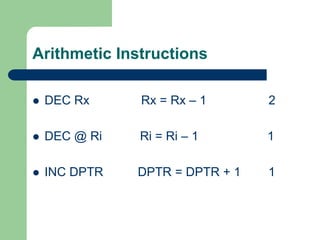

This document describes the instruction set of the 8051 microcontroller. It discusses the three types of instructions - single byte, double byte, and triple byte - based on the number of bytes needed to represent the instruction. It provides examples of different types of instructions, including data transfer, arithmetic, logical, logical bit, and program flow control instructions. Each instruction is defined by its mnemonic, description, and number of bytes.

![Arithmetic Instructions

MUL AB B:A = A * B 1

DIV AB A = [A/B] 1

DA A Decimal adjustment of 1

accumulator according to BCD code](https://image.slidesharecdn.com/instructionsetof8051-230121061102-f71afe2d/85/Instruction-set-of-8051-ppt-27-320.jpg)