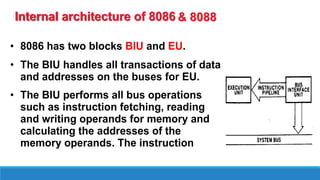

The Intel 8086 is a 16-bit microprocessor that can access up to 1 MB of memory. It has two main units: the Bus Interface Unit (BIU) which handles bus operations like instruction fetching and memory access, and the Execution Unit (EU) which decodes and executes instructions. The BIU and EU work asynchronously using pipelining to improve performance. The 8086 uses segmentation to access different types of memory segments like code, data, stack, and extra. It has 16 general purpose registers including flags, pointer and index registers that are used by the EU during execution.