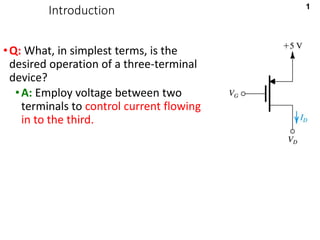

The document discusses the structure and operation of MOSFET transistors. It describes how applying a voltage between the gate and source terminals can induce a conducting channel between the drain and source, allowing current to flow. The relationship between drain current and drain-source voltage depends on whether vDS is smaller than, equal to, or greater than the overdrive voltage vOV. In saturation, when vDS exceeds vOV, further increasing vDS no longer affects the drain current.