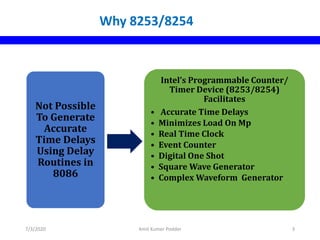

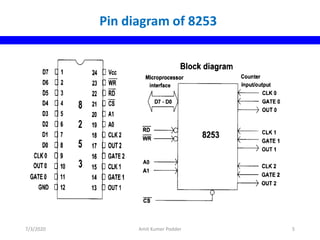

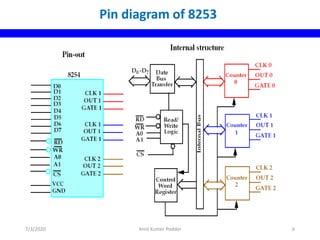

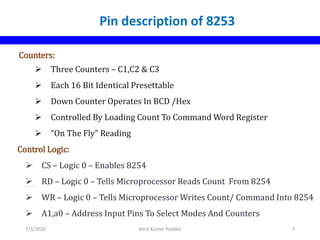

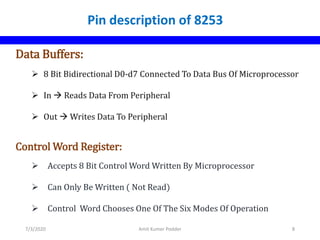

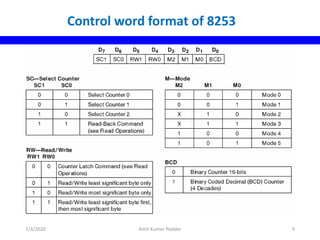

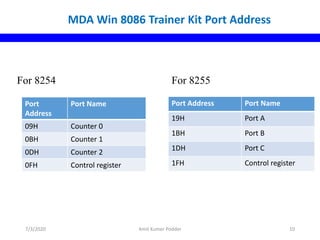

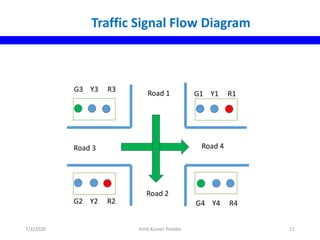

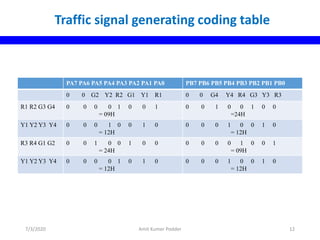

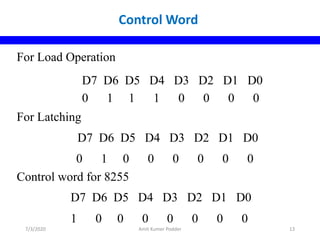

This document discusses using the 8253/8254 programmable interval timer and 8255 programmable peripheral interface (PPI) to implement a traffic controller for a microprocessor experiment. It describes the functions and advantages of the 8253/8254 timer, including its ability to generate accurate time delays and complex waveforms. The document provides details on the timers' pins, counters, control logic, data buffers, control word format, and port addresses when used with the 8086 microprocessor. It also includes a traffic signal flow diagram and coding tables for generating traffic signals using the 8255 PPI and controlling the latch, load, and operation of the counters.