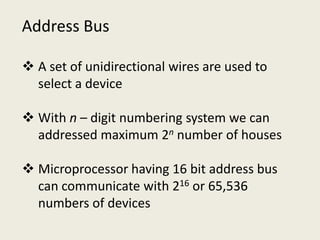

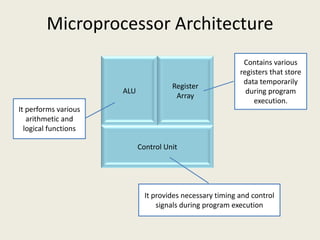

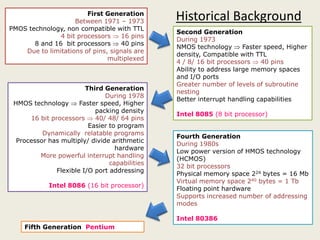

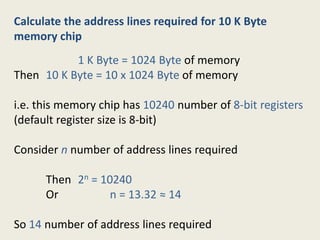

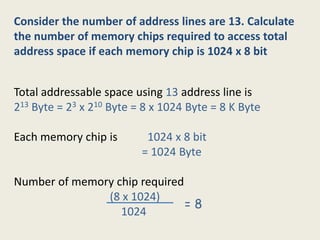

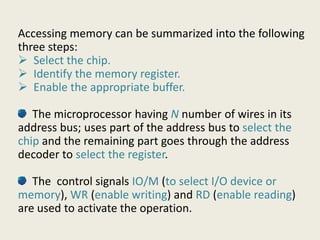

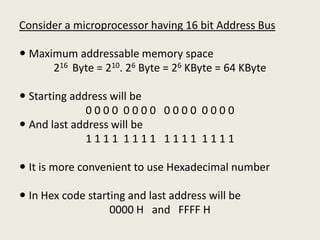

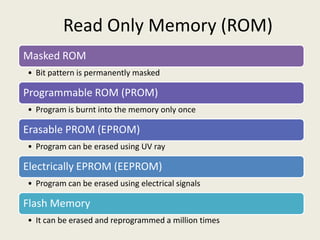

This document discusses microprocessor architecture and memory interfacing. It provides an overview of the basic parts and operations of a microprocessor-based system including the CPU, memory, and I/O devices. It describes the different types of buses (address bus, data bus, control bus) and how they transfer data and signals. It also explains memory interfacing and addressing, different types of memory (RAM, ROM), and how microprocessors access memory using an address bus.