Embed presentation

Download as PDF, PPTX

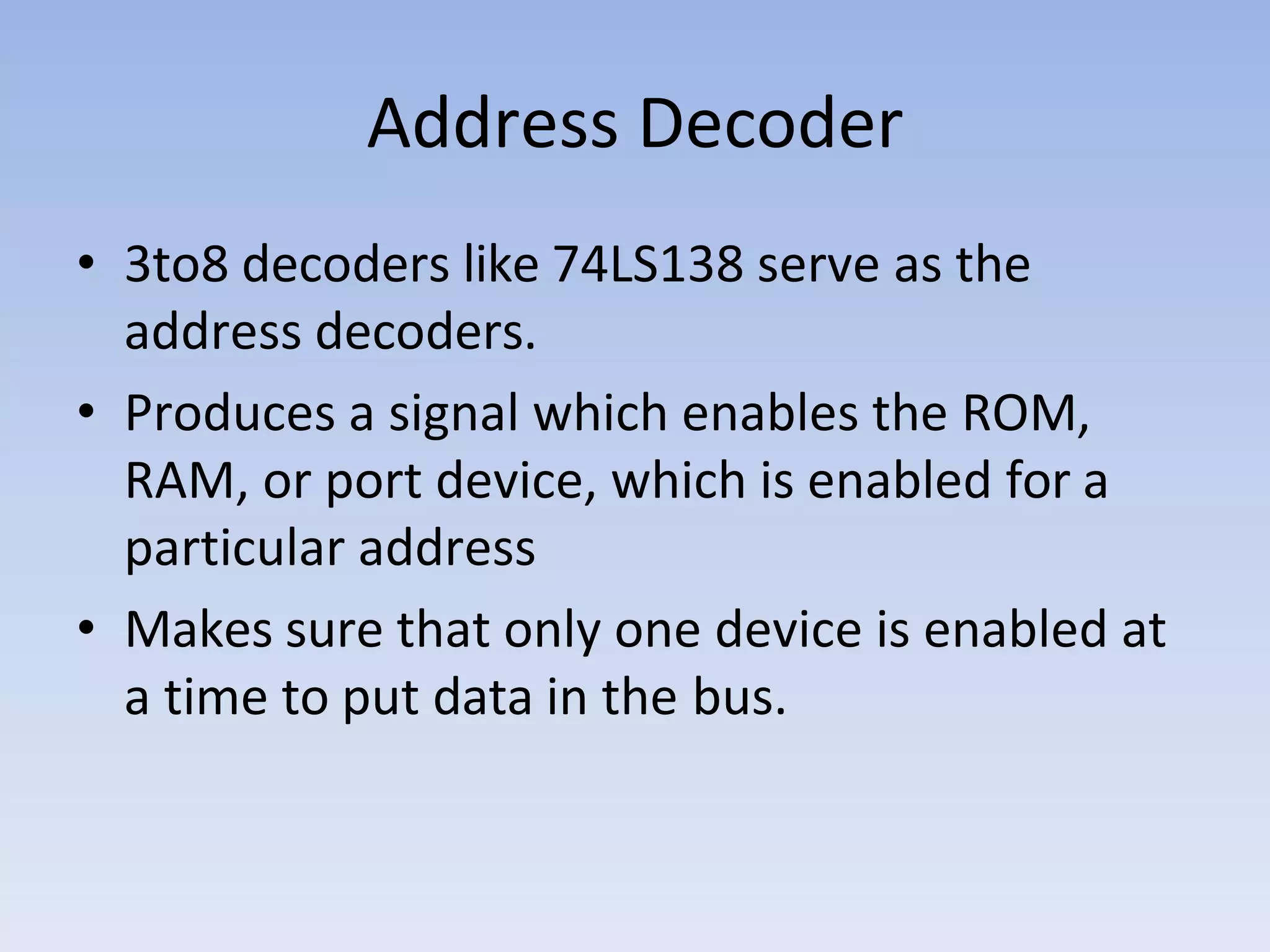

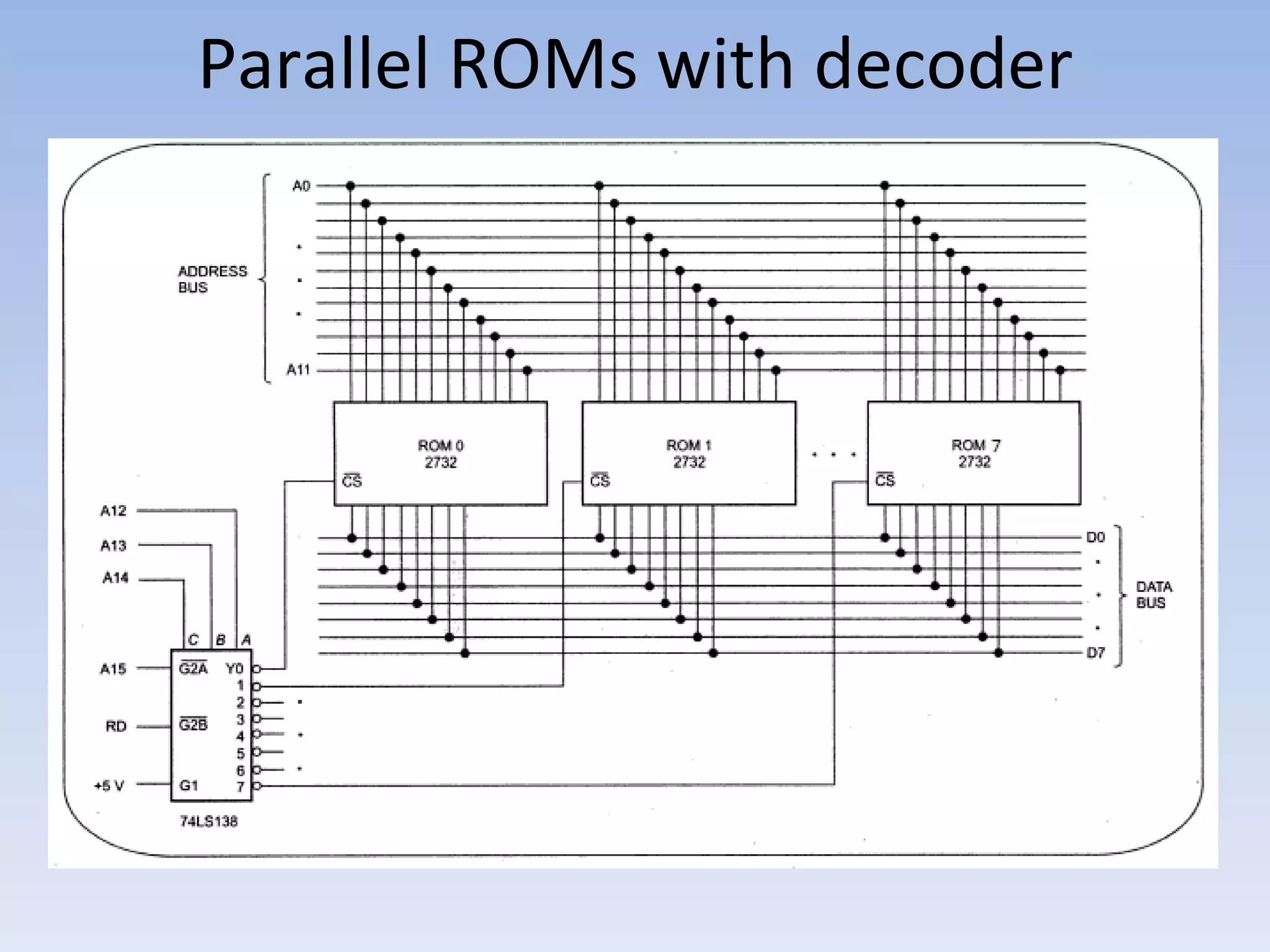

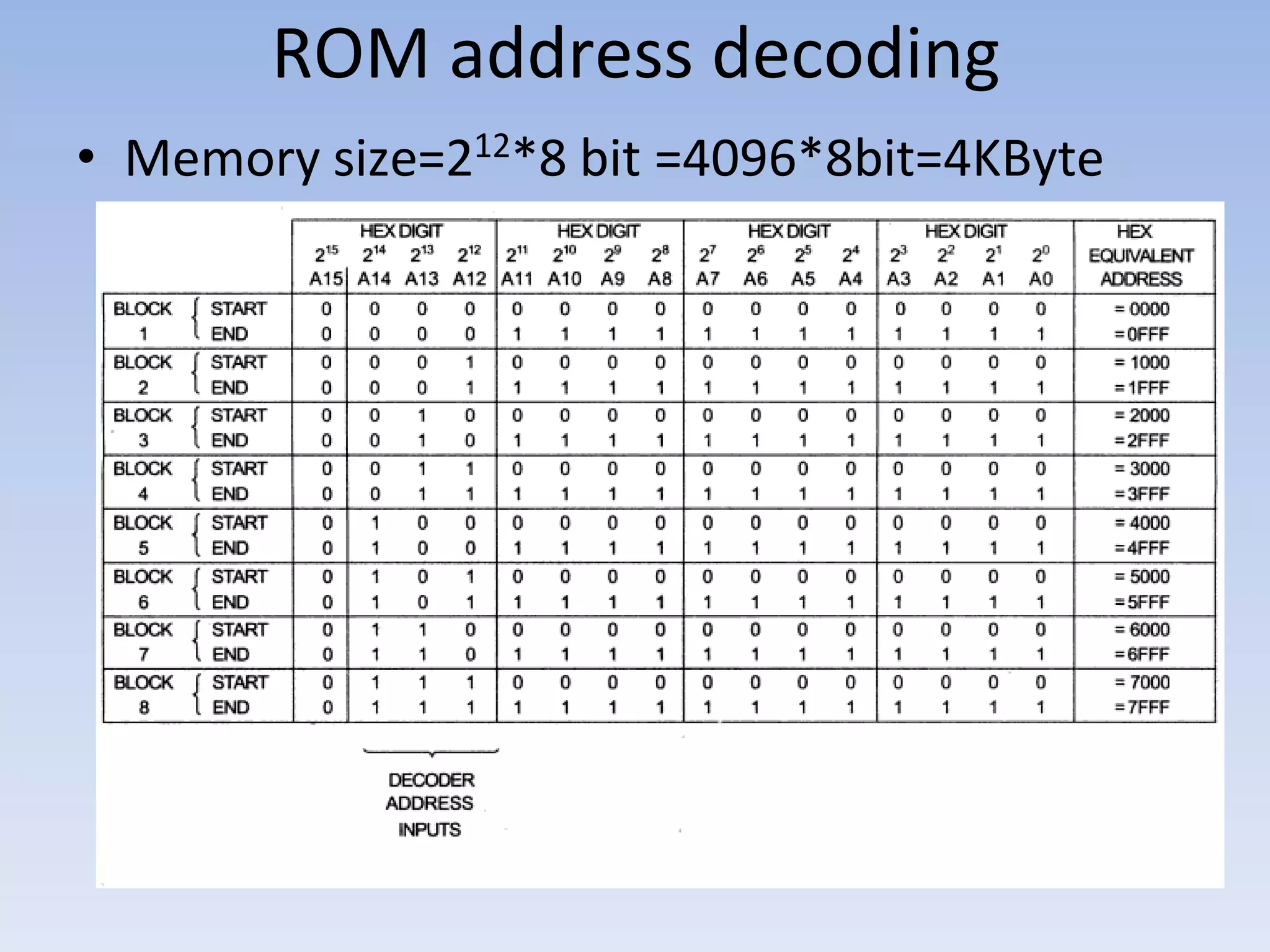

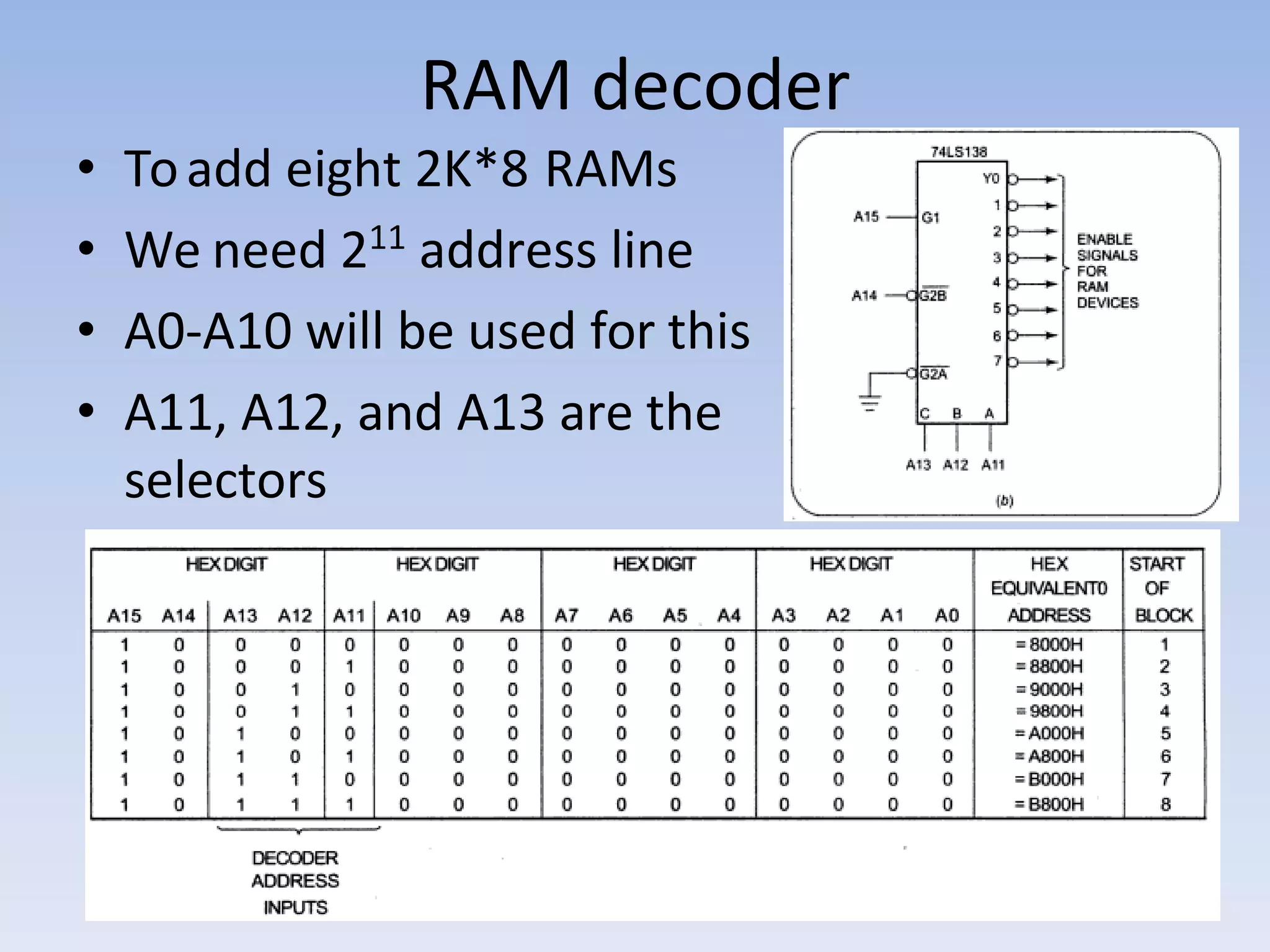

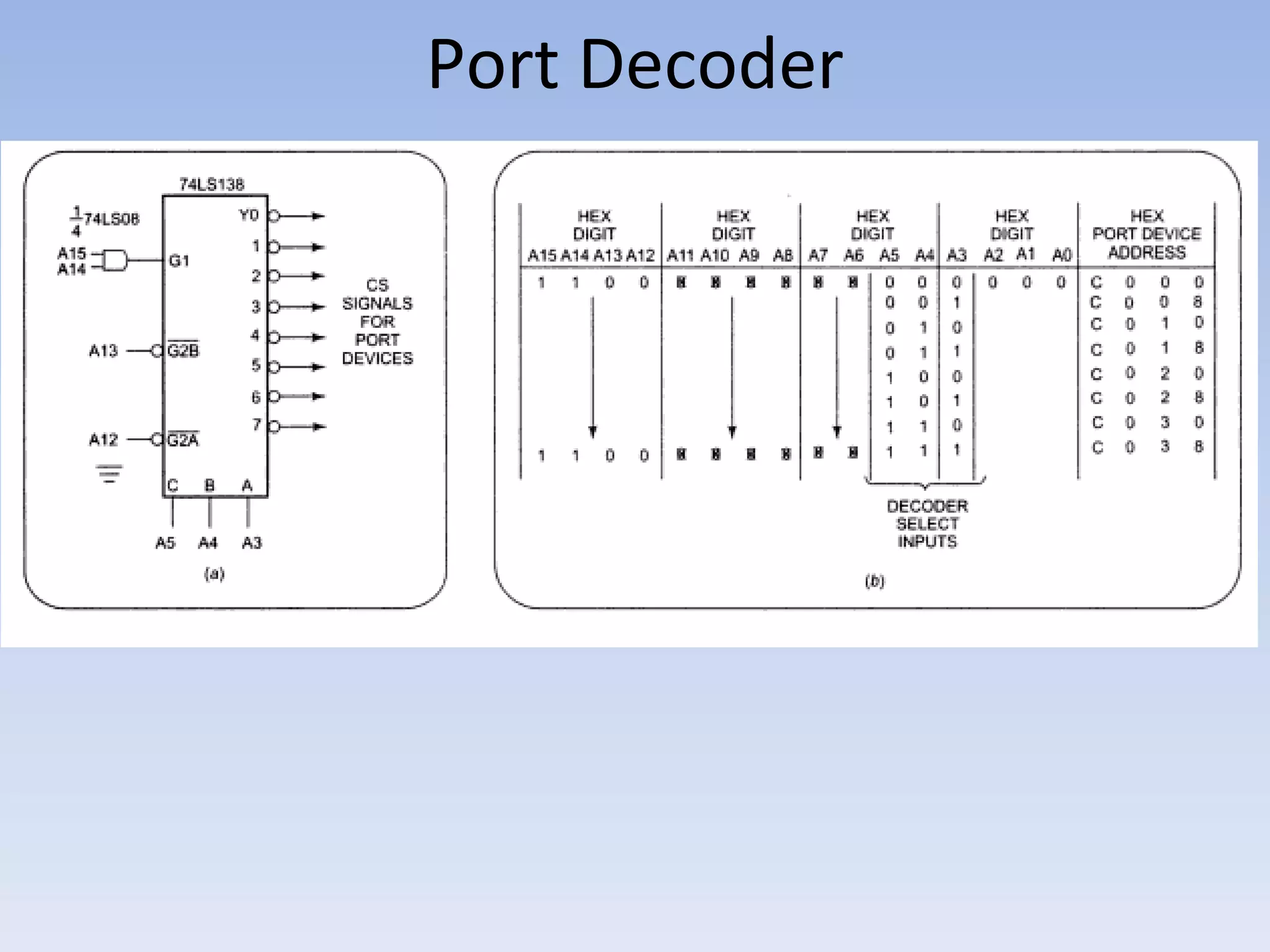

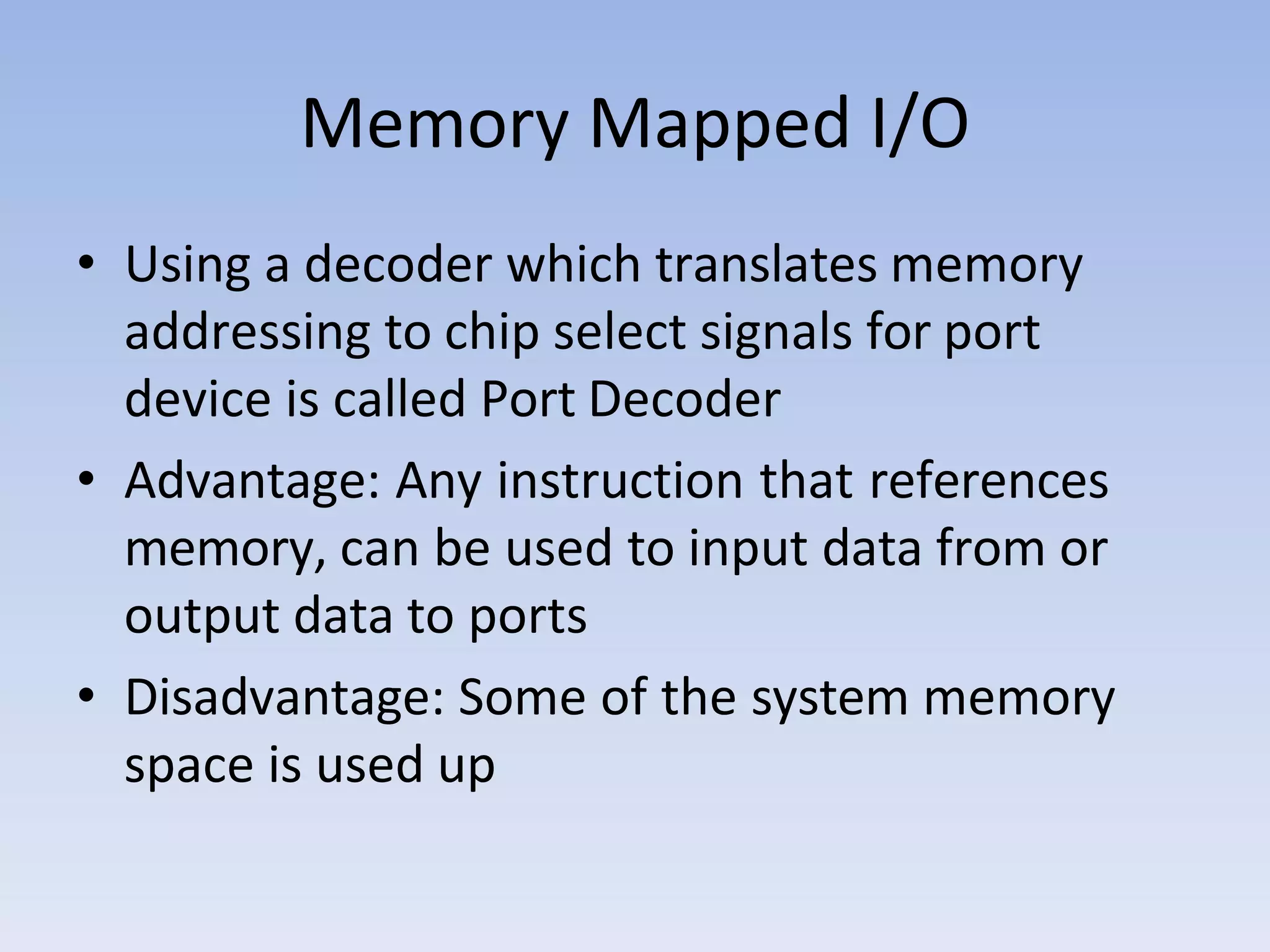

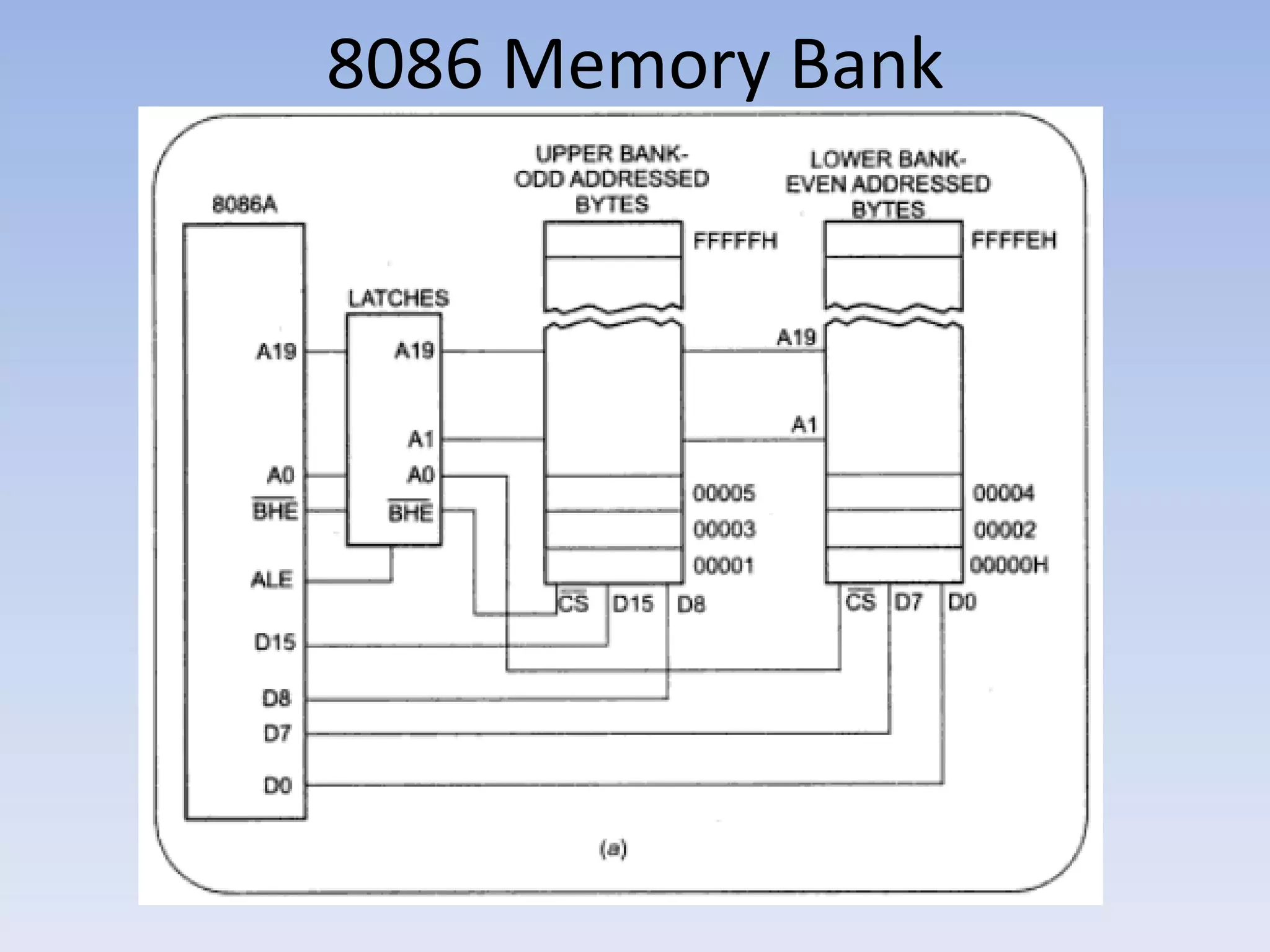

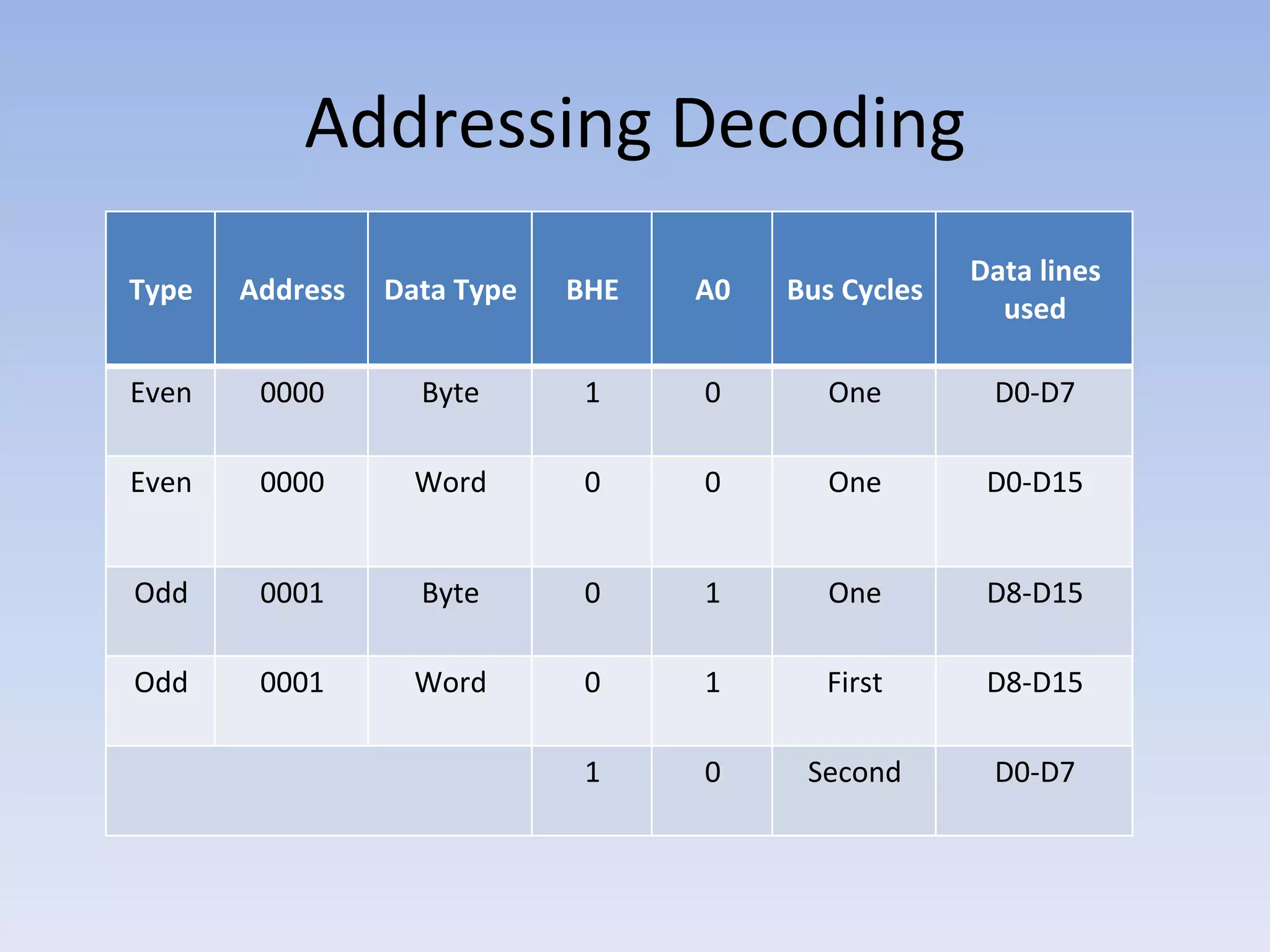

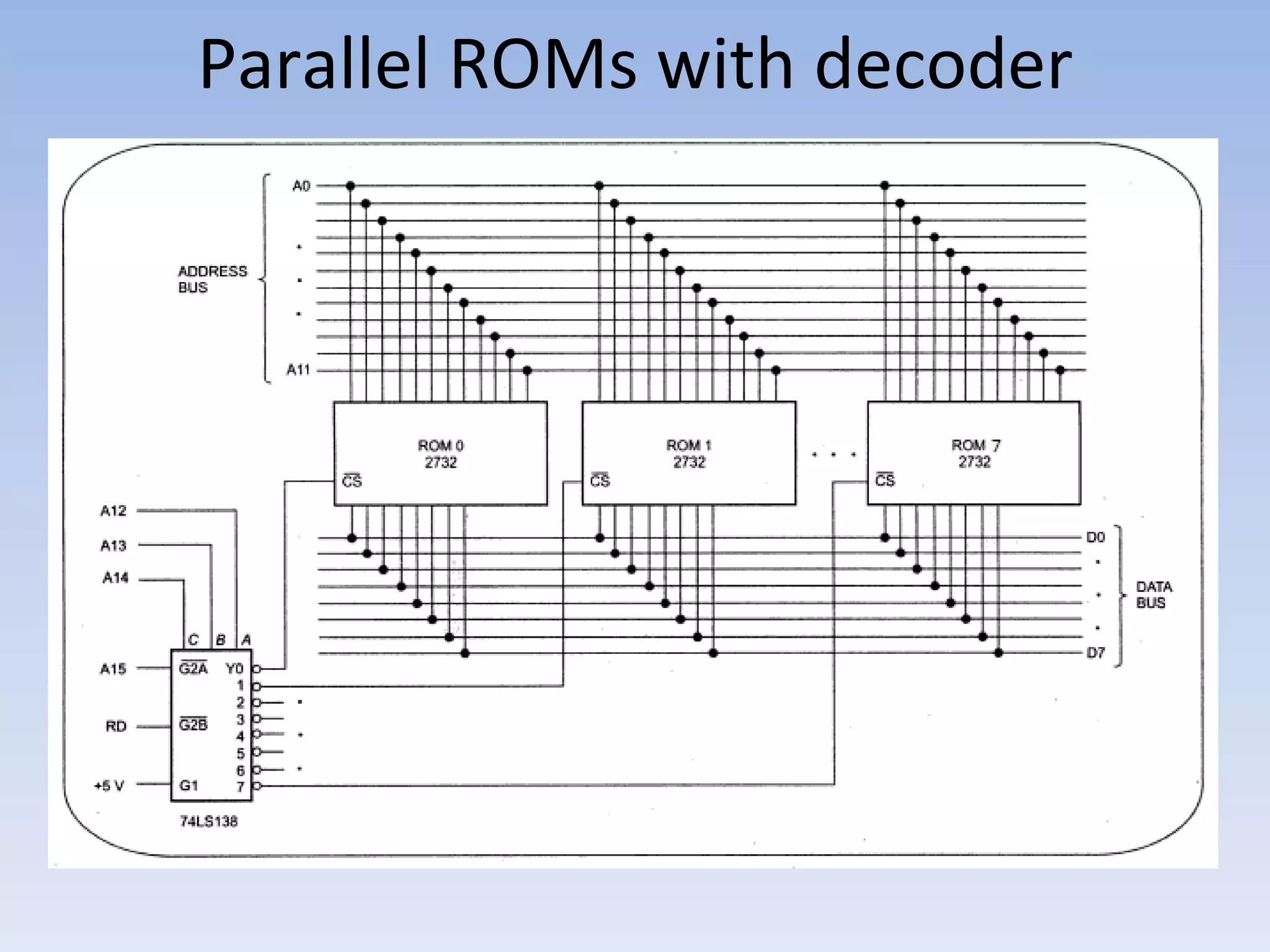

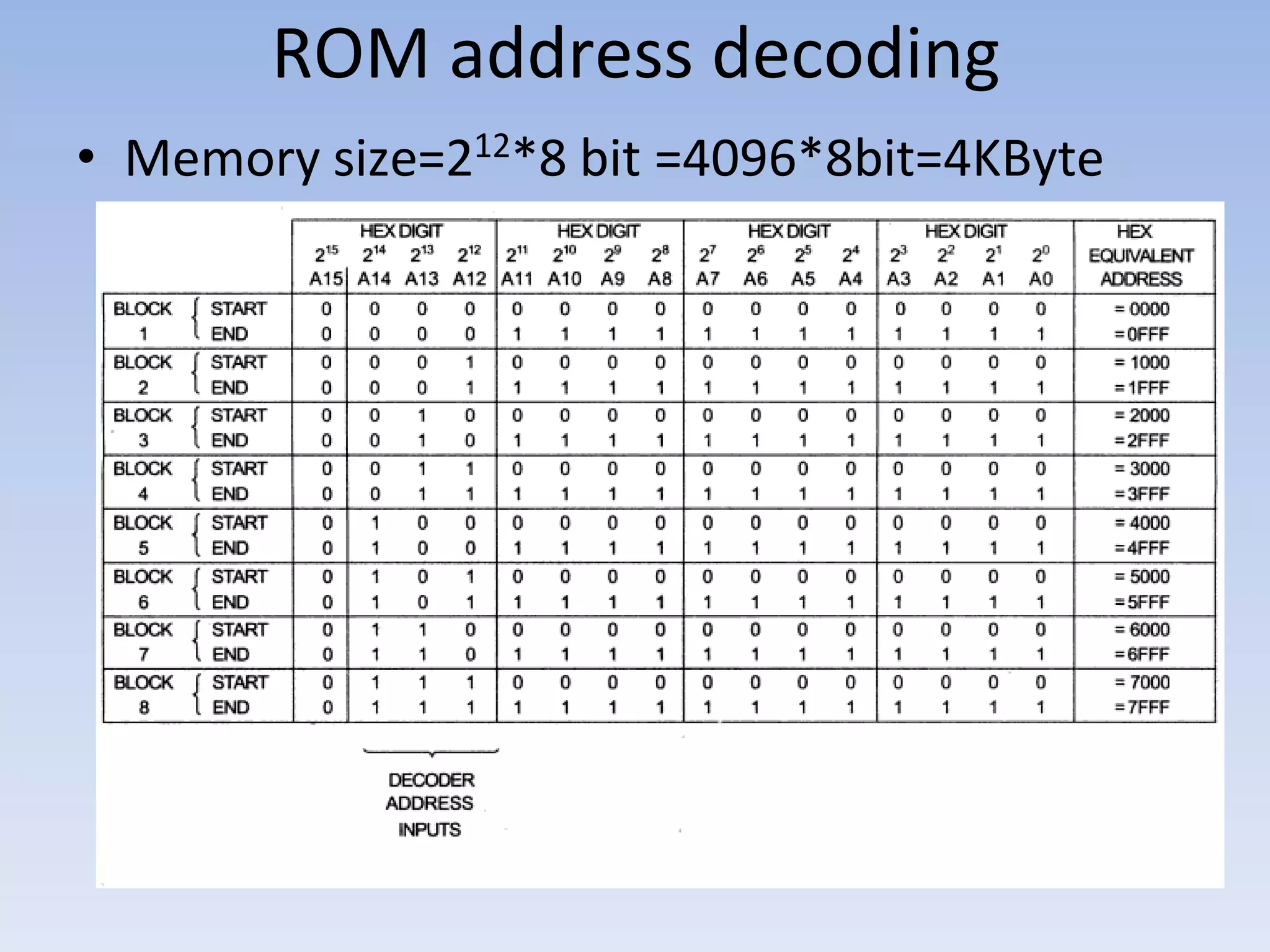

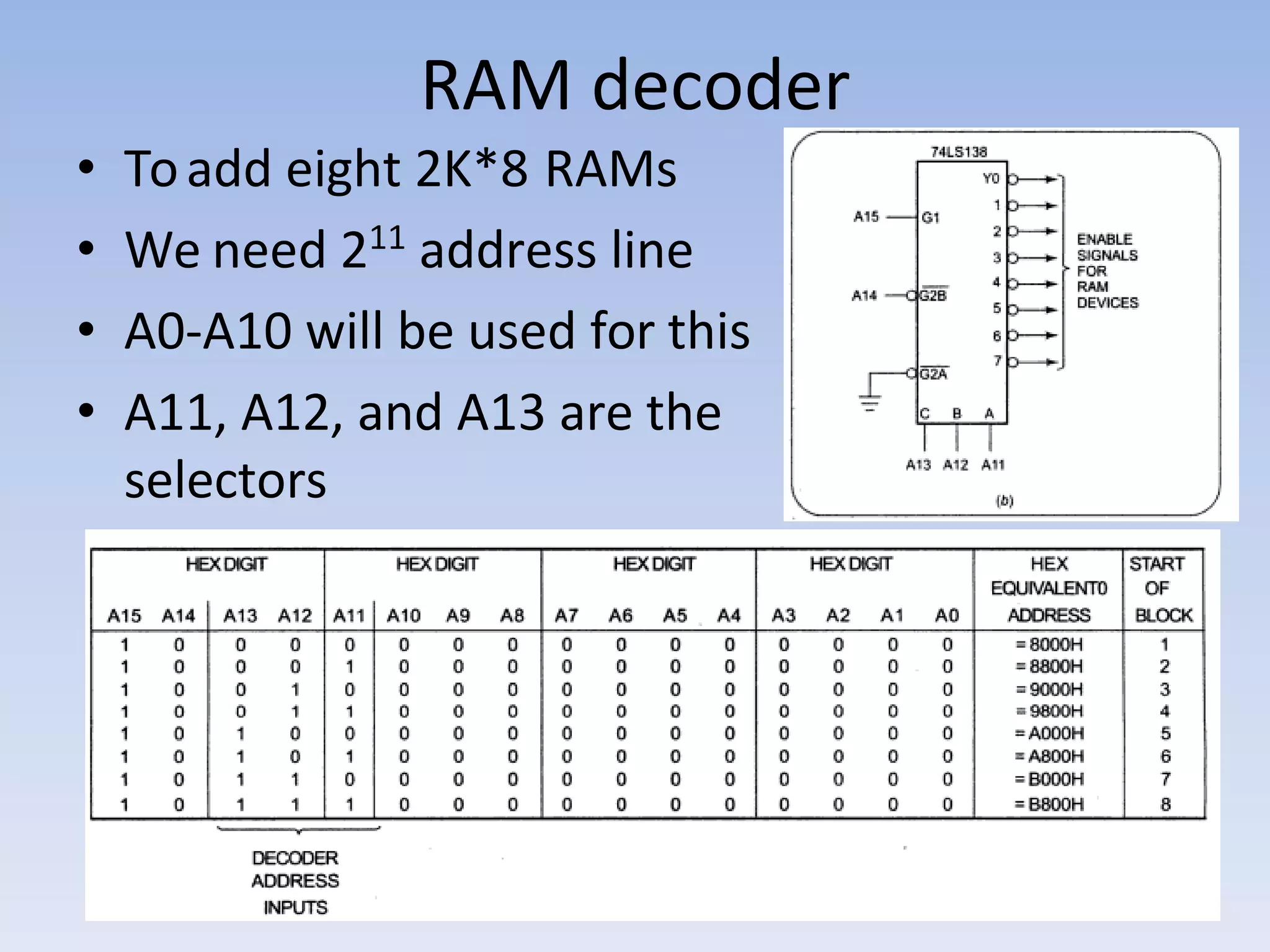

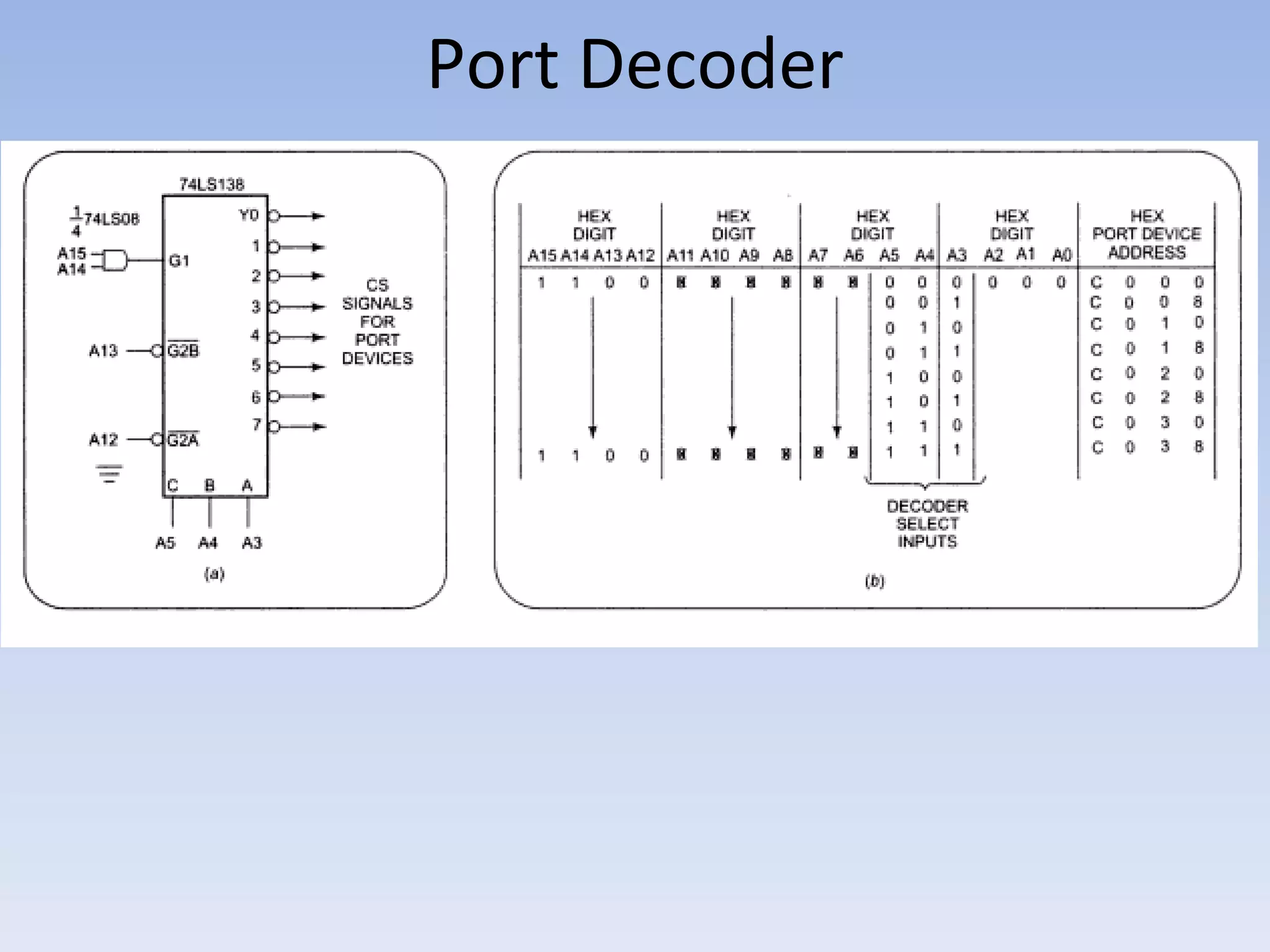

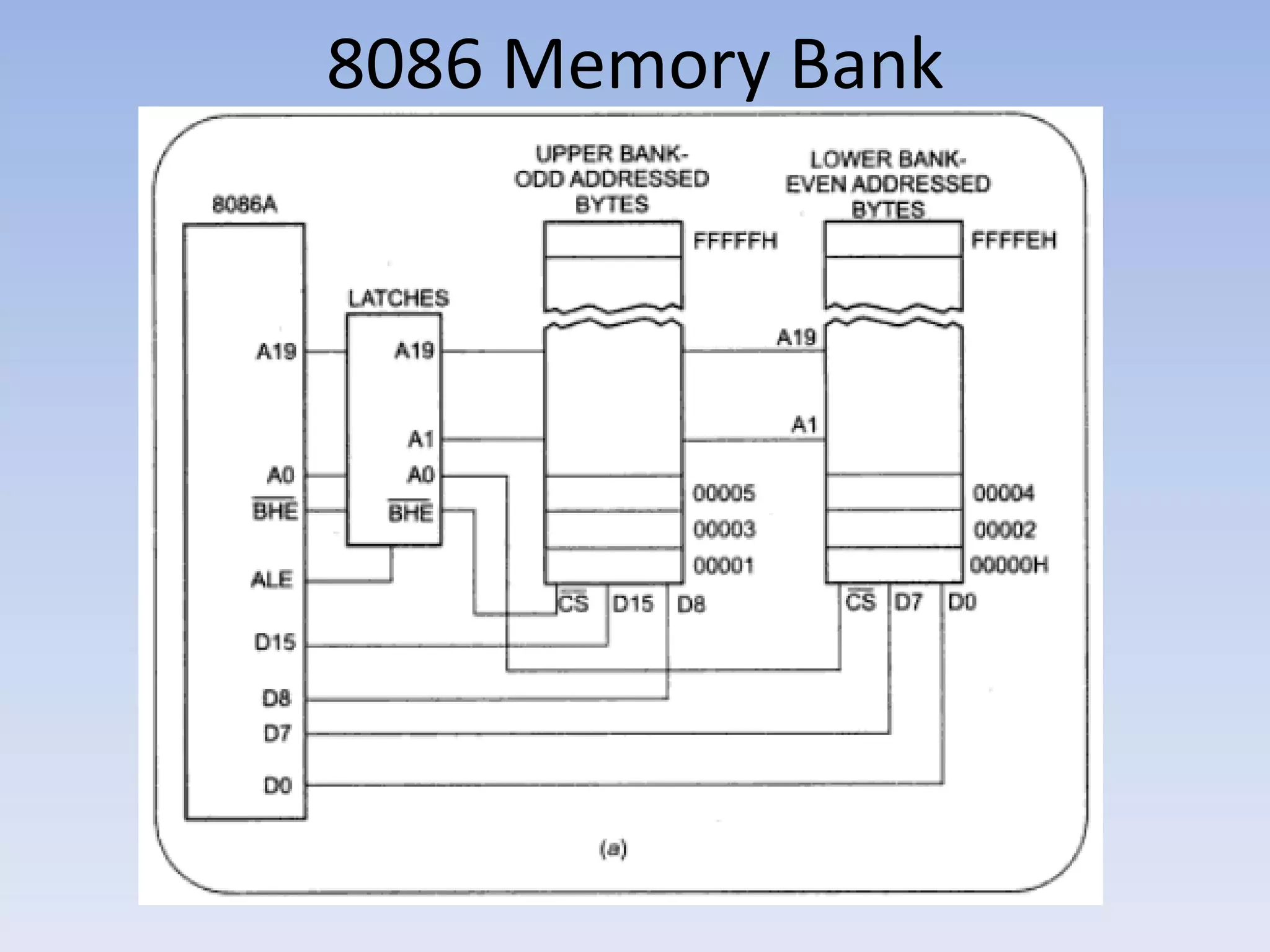

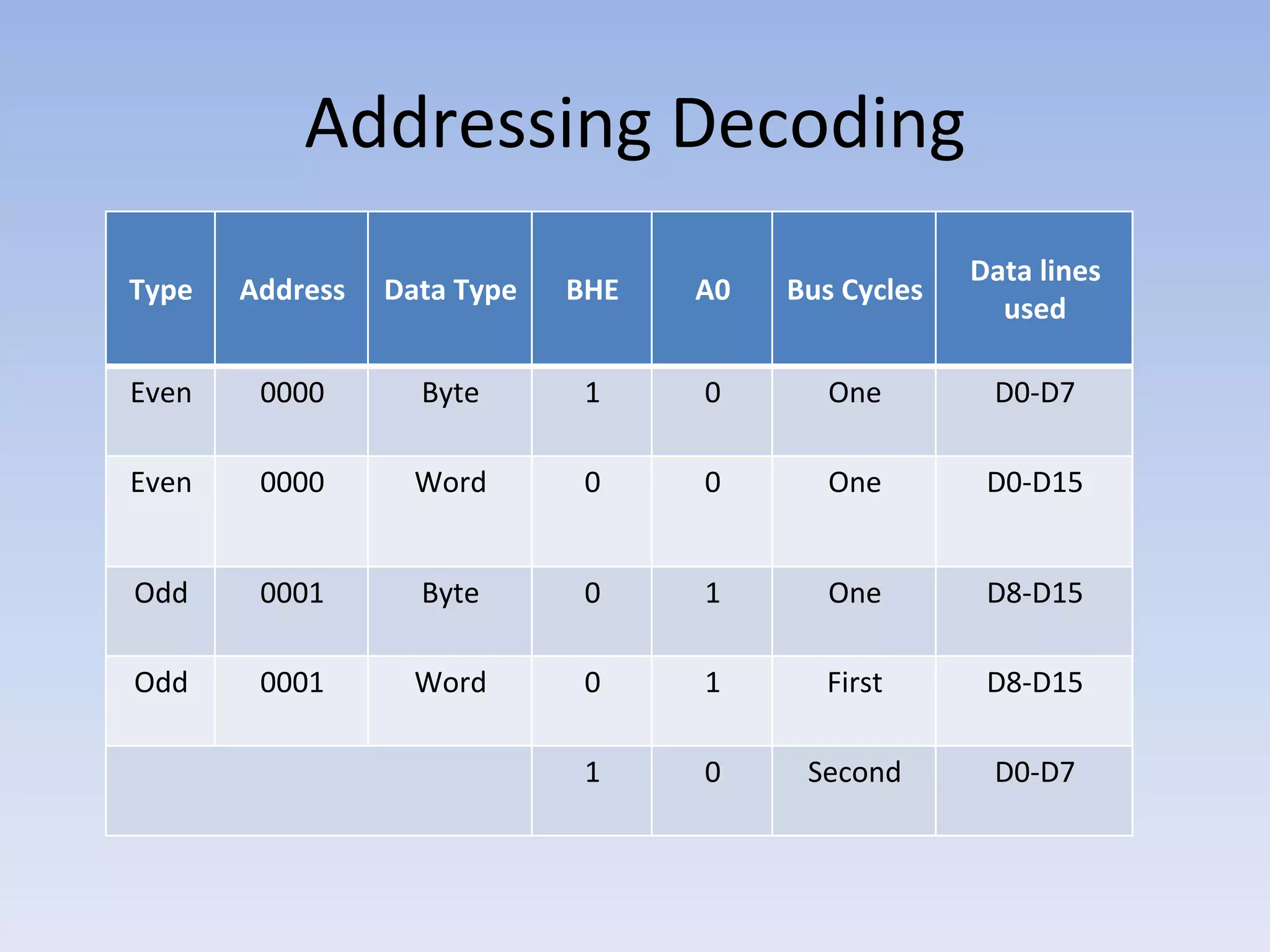

This document discusses addressing memory and ports through the use of decoders. It describes how 3-to-8 decoders are used as address decoders to enable specific ROM, RAM, or port devices based on the address. Parallel ROMs are addressed using decoders, with a 12-bit address allowing up to 4KB of memory. RAM decoders allow up to 8 RAM chips to be addressed using 11 address lines. Port decoders translate memory addresses to select signals for input/output ports, allowing ports to be accessed using memory instructions. Memory banks for the 8086 use address lines A1-A19 to select memory within the bank, and A0 and a bus enable line to separately address the lower and upper banks.