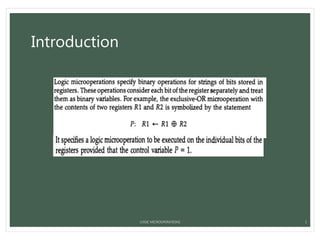

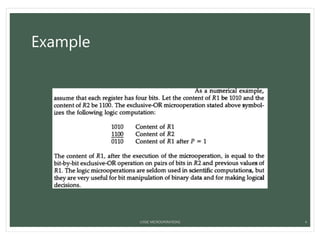

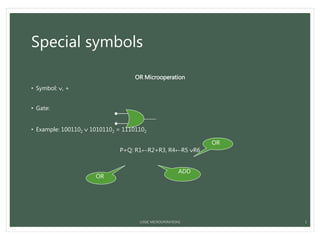

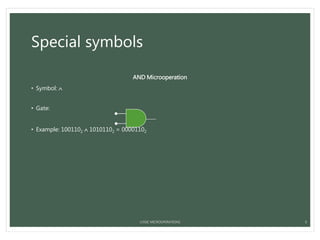

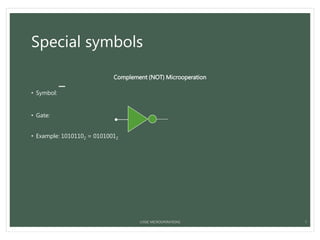

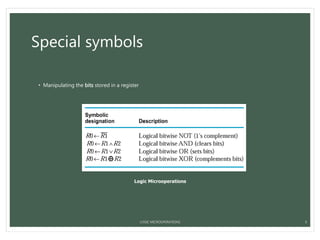

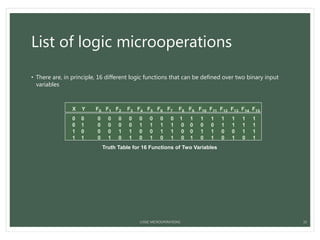

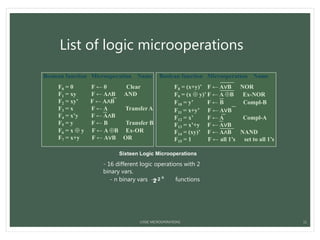

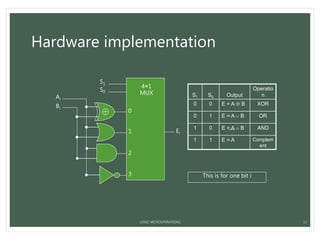

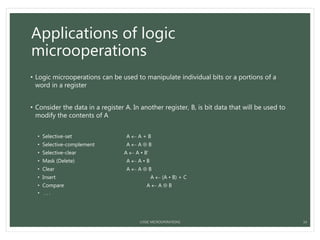

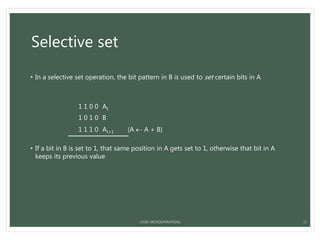

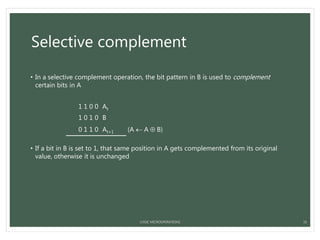

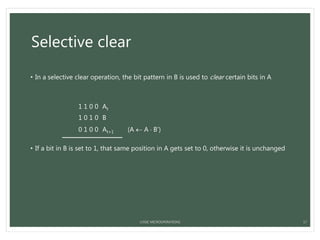

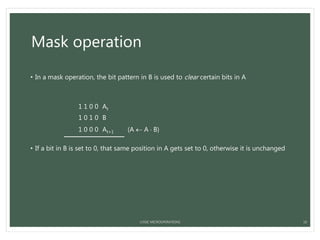

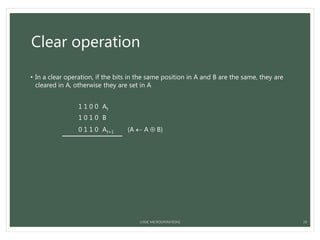

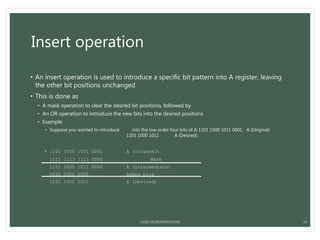

The document provides an overview of logic microoperations in computer organization and architecture, detailing special symbols, the list of operations, and hardware implementation. It explains various logic functions and their representations, such as AND, OR, XOR, and their uses for manipulating individual bits in registers. Additionally, it discusses applications like selective set, complement, clear, mask operations, and insert operations for managing data within registers.