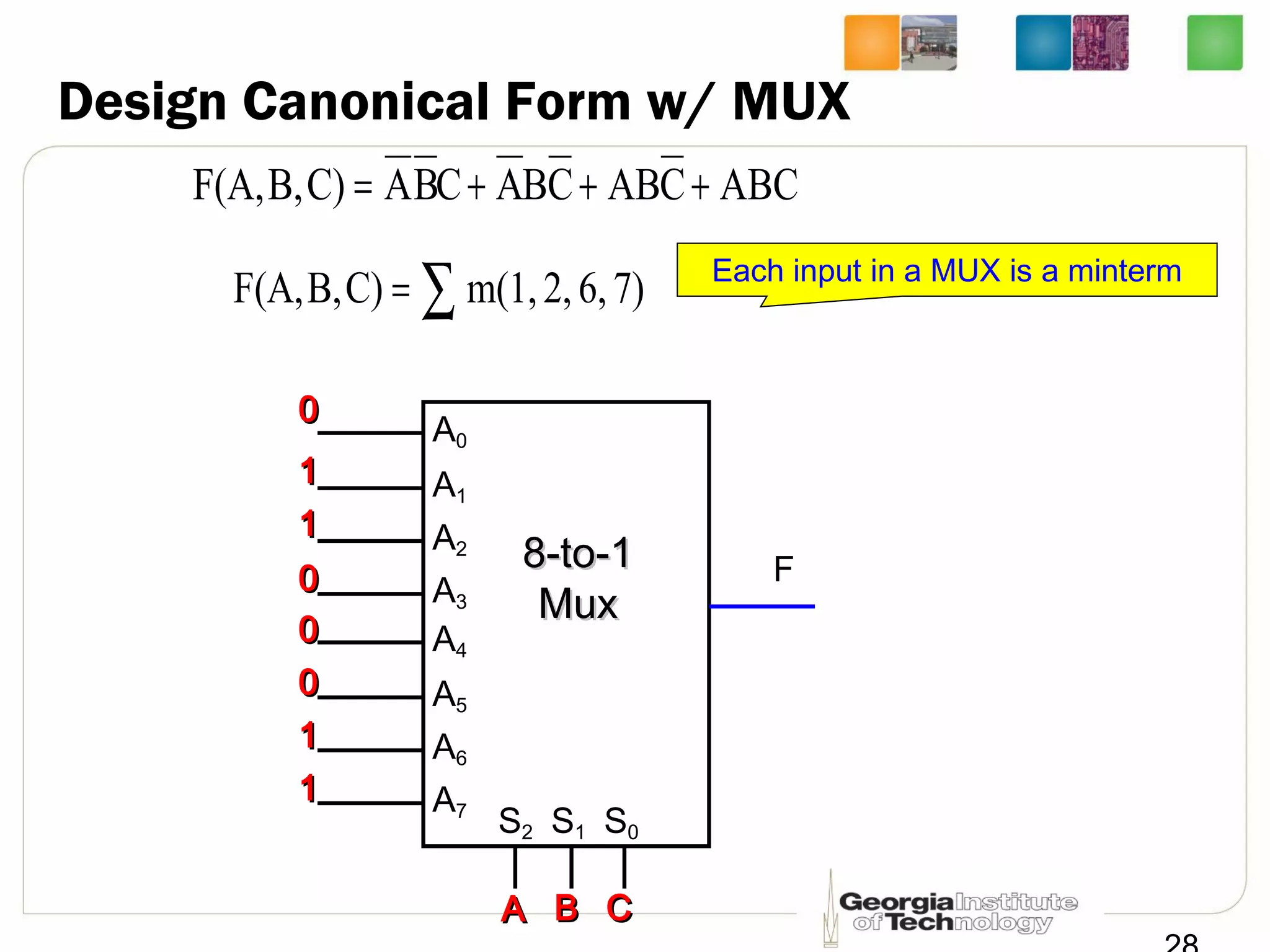

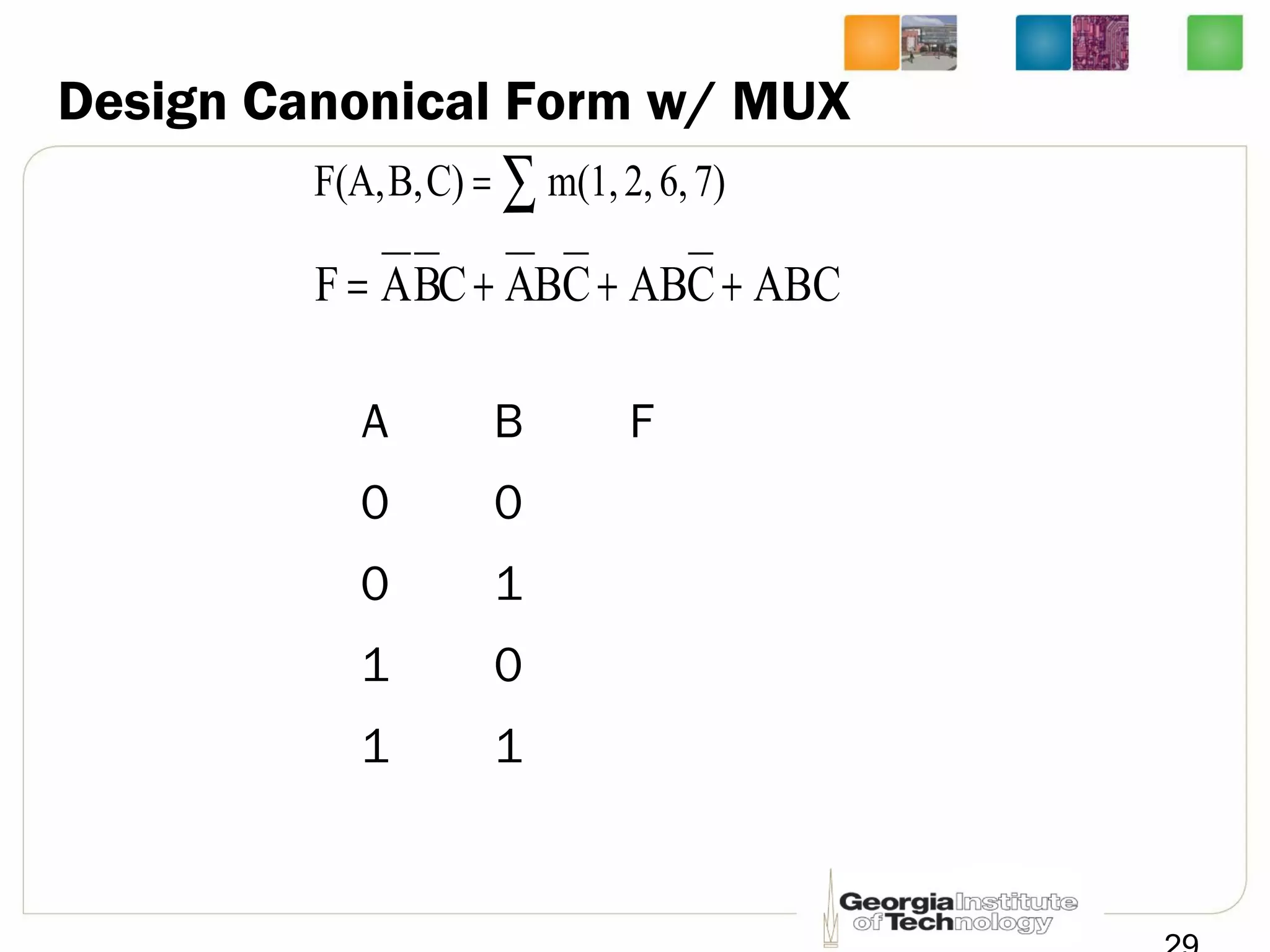

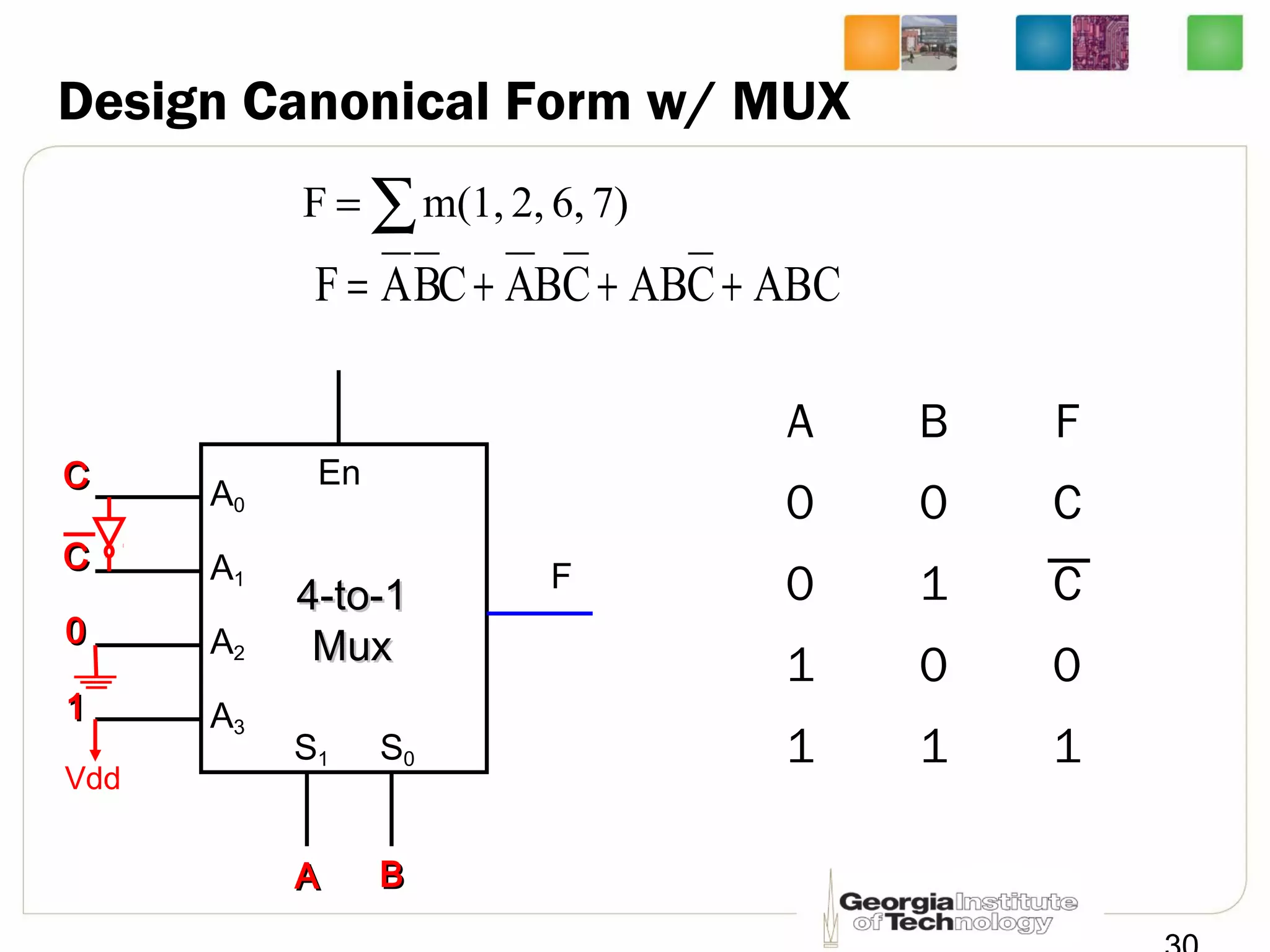

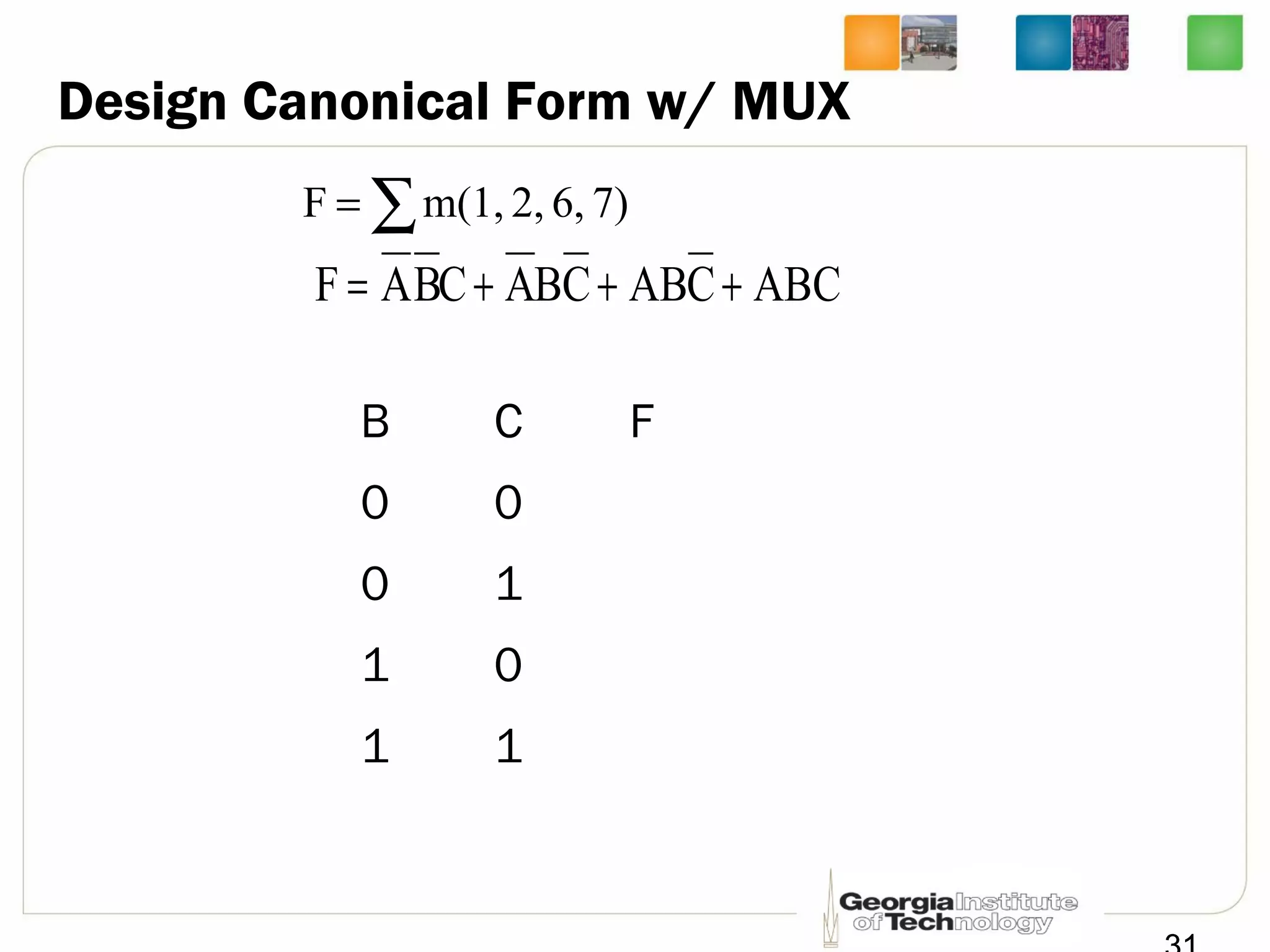

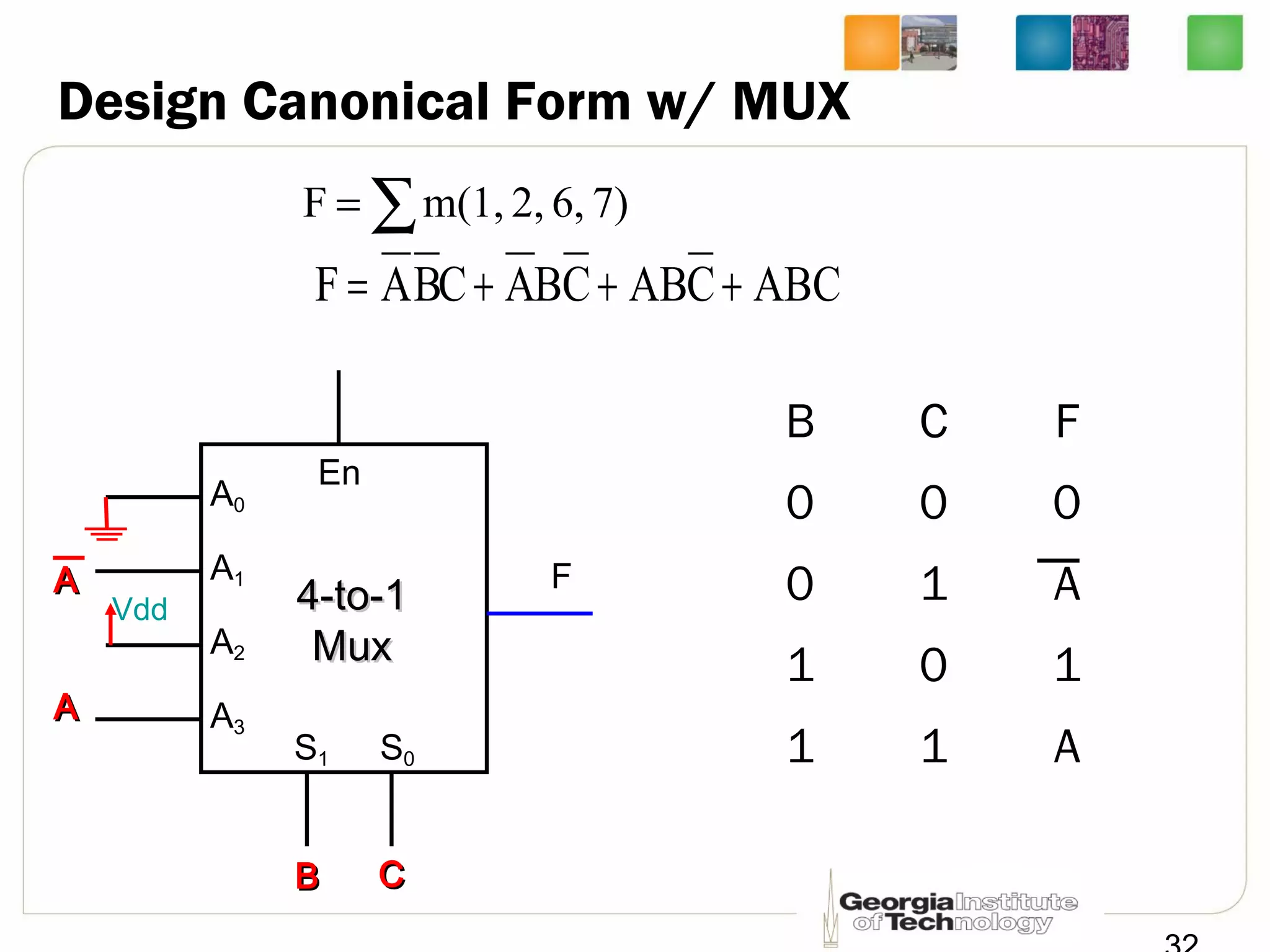

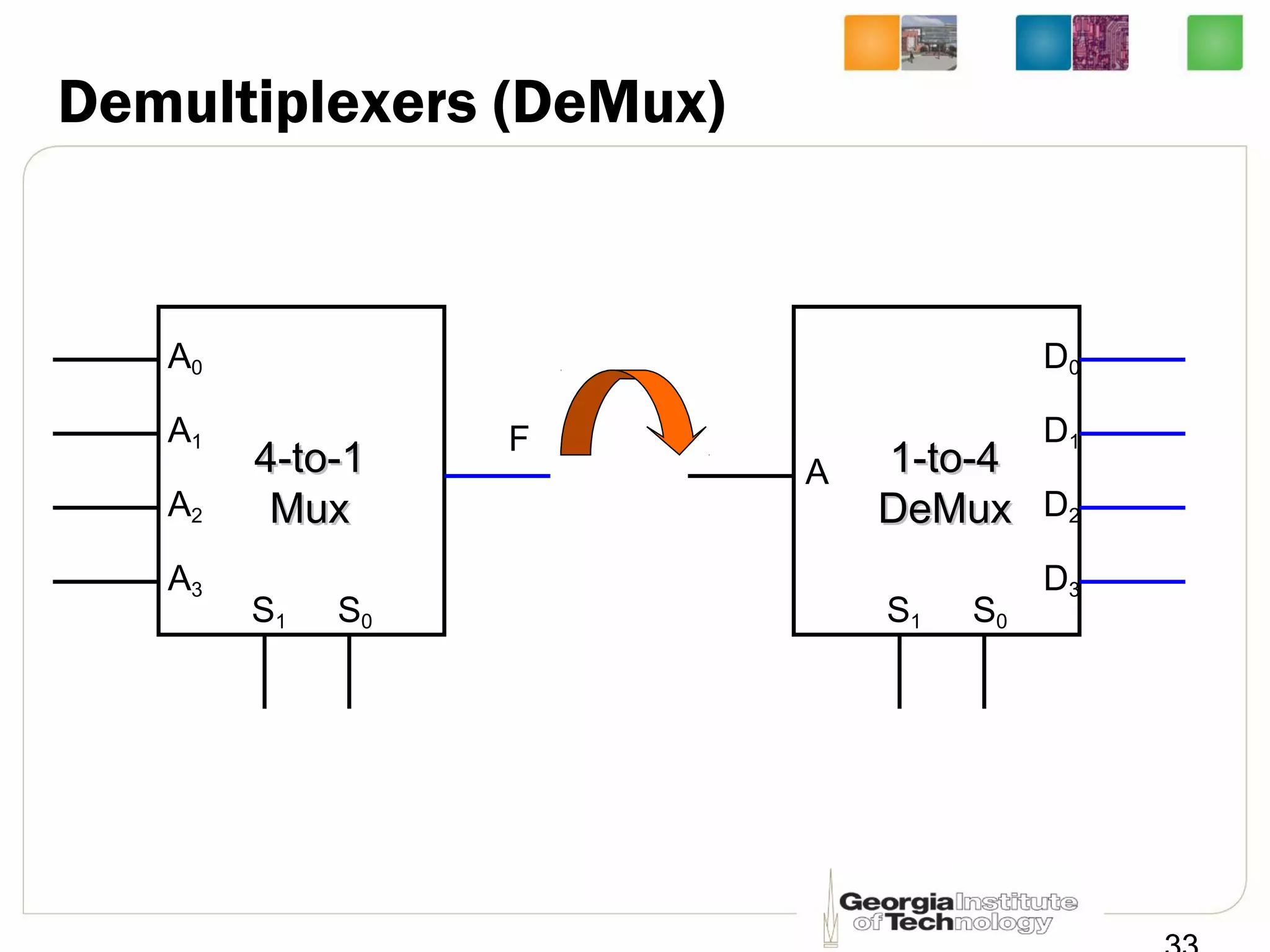

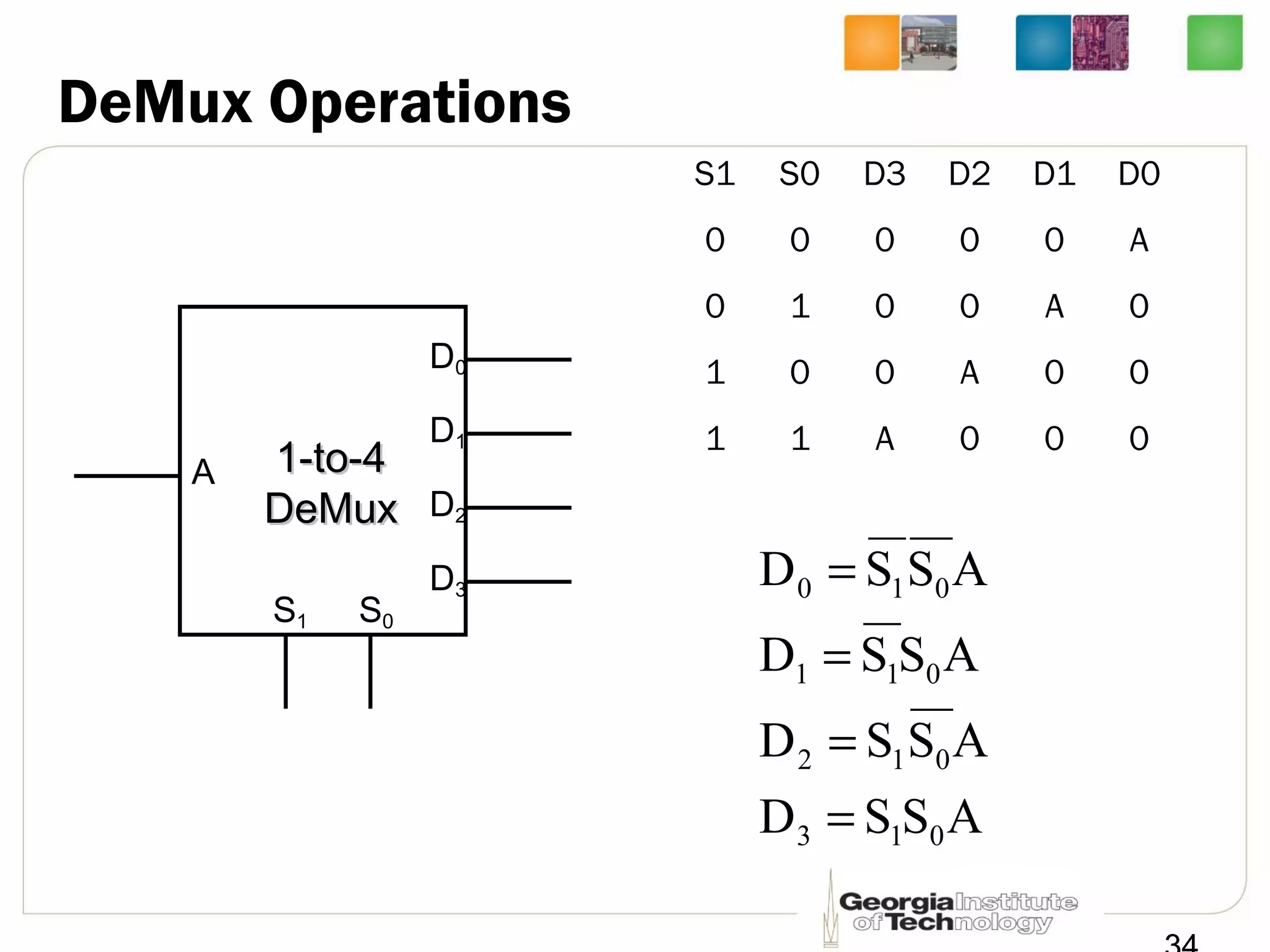

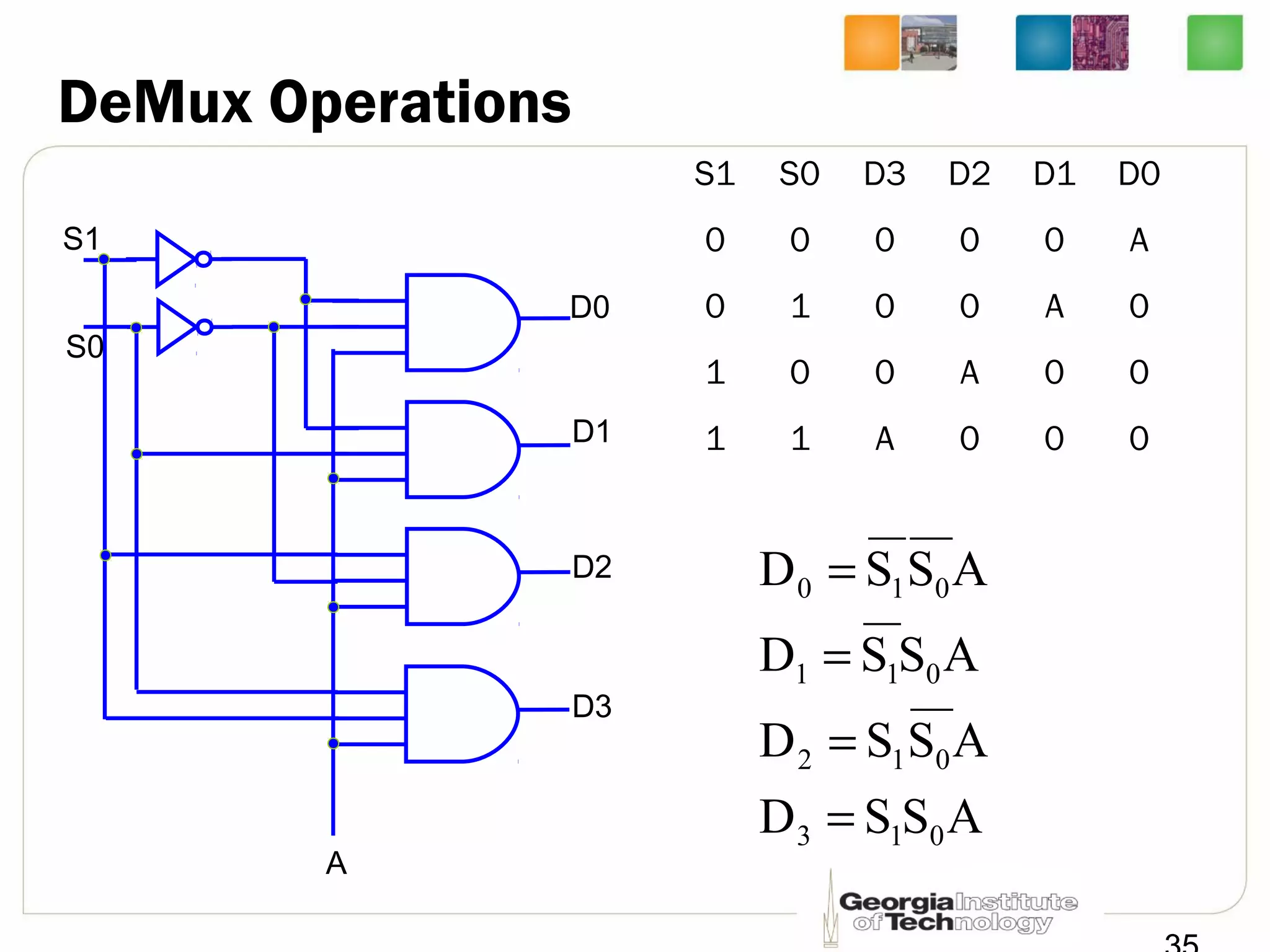

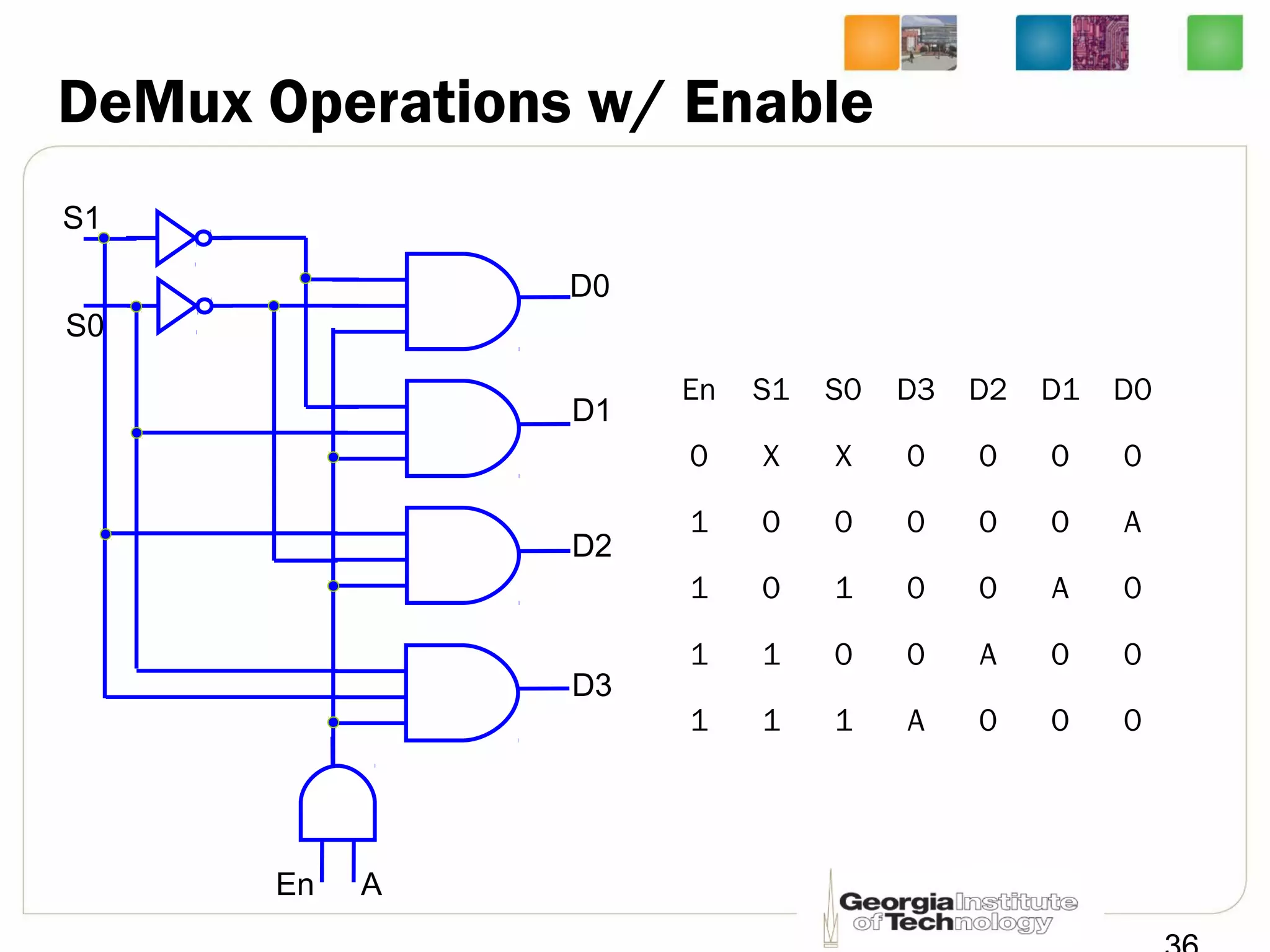

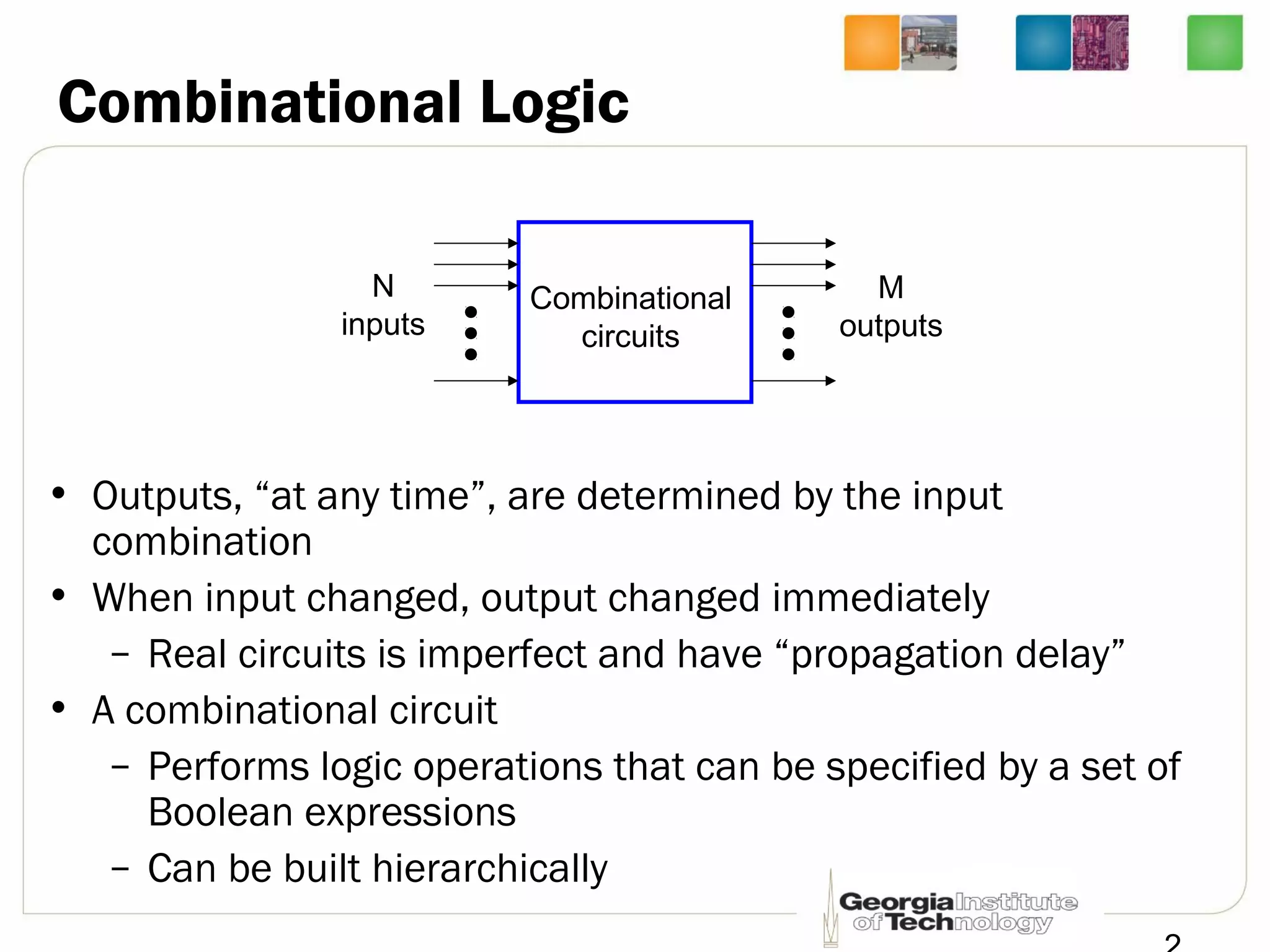

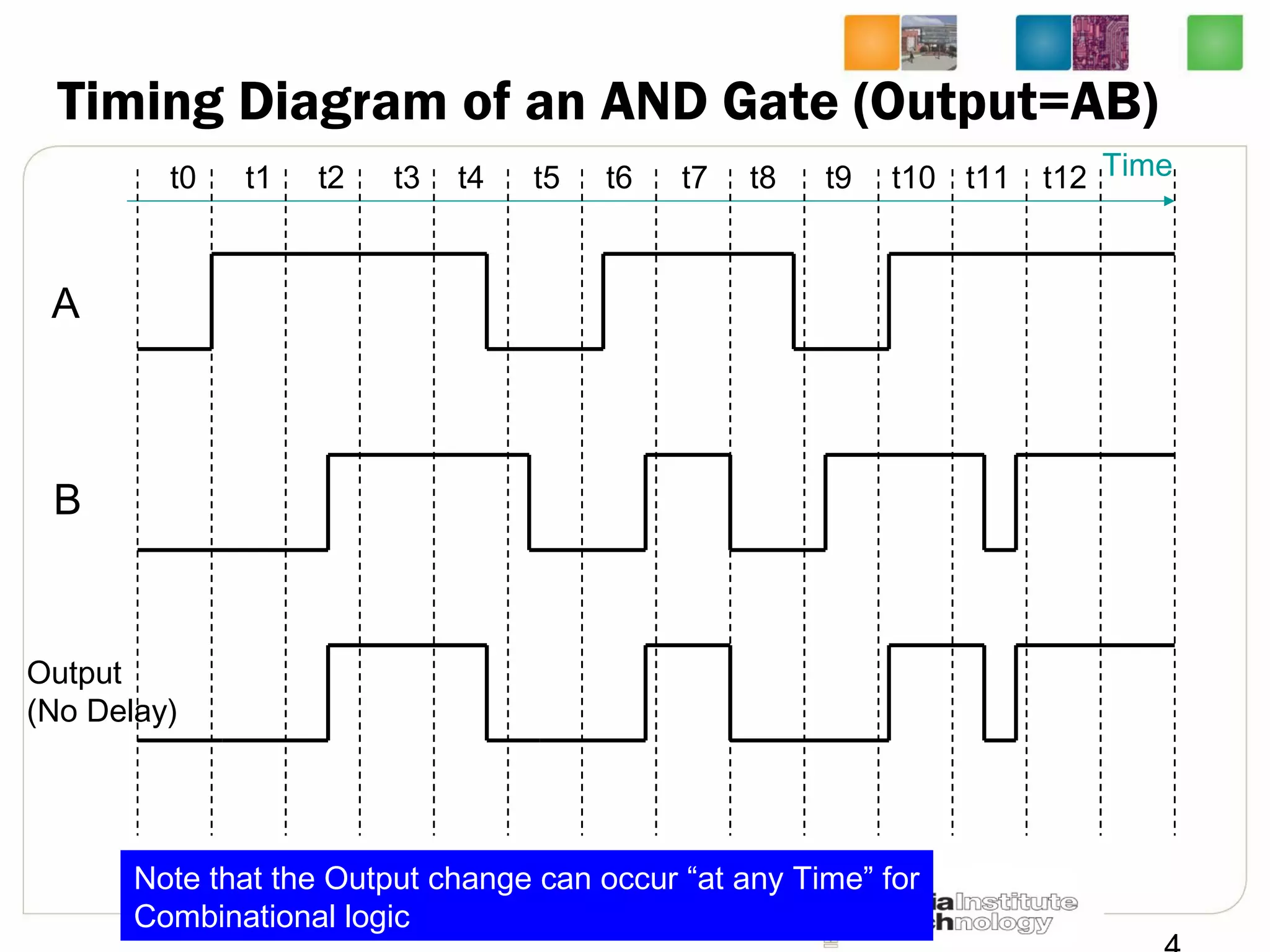

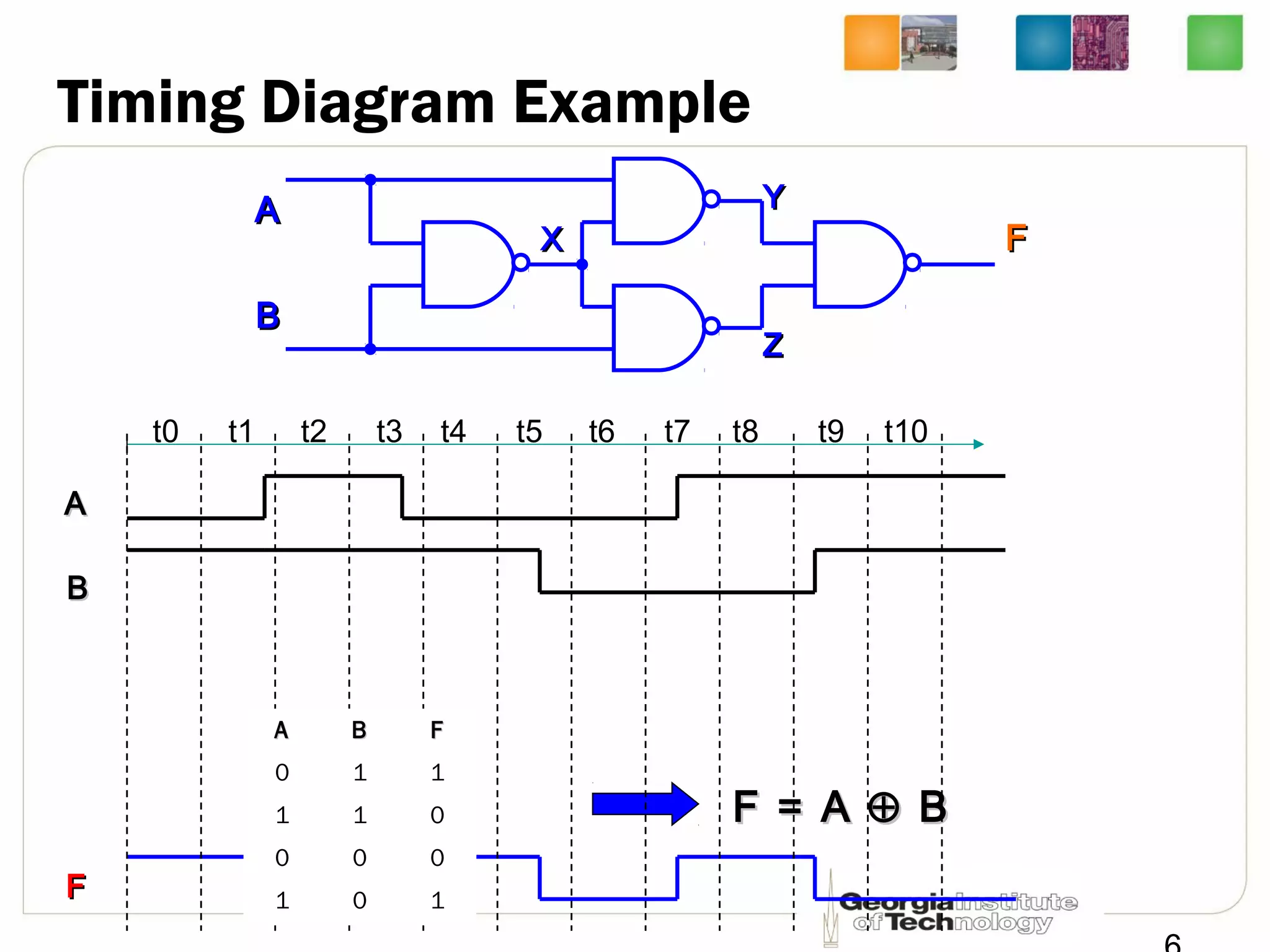

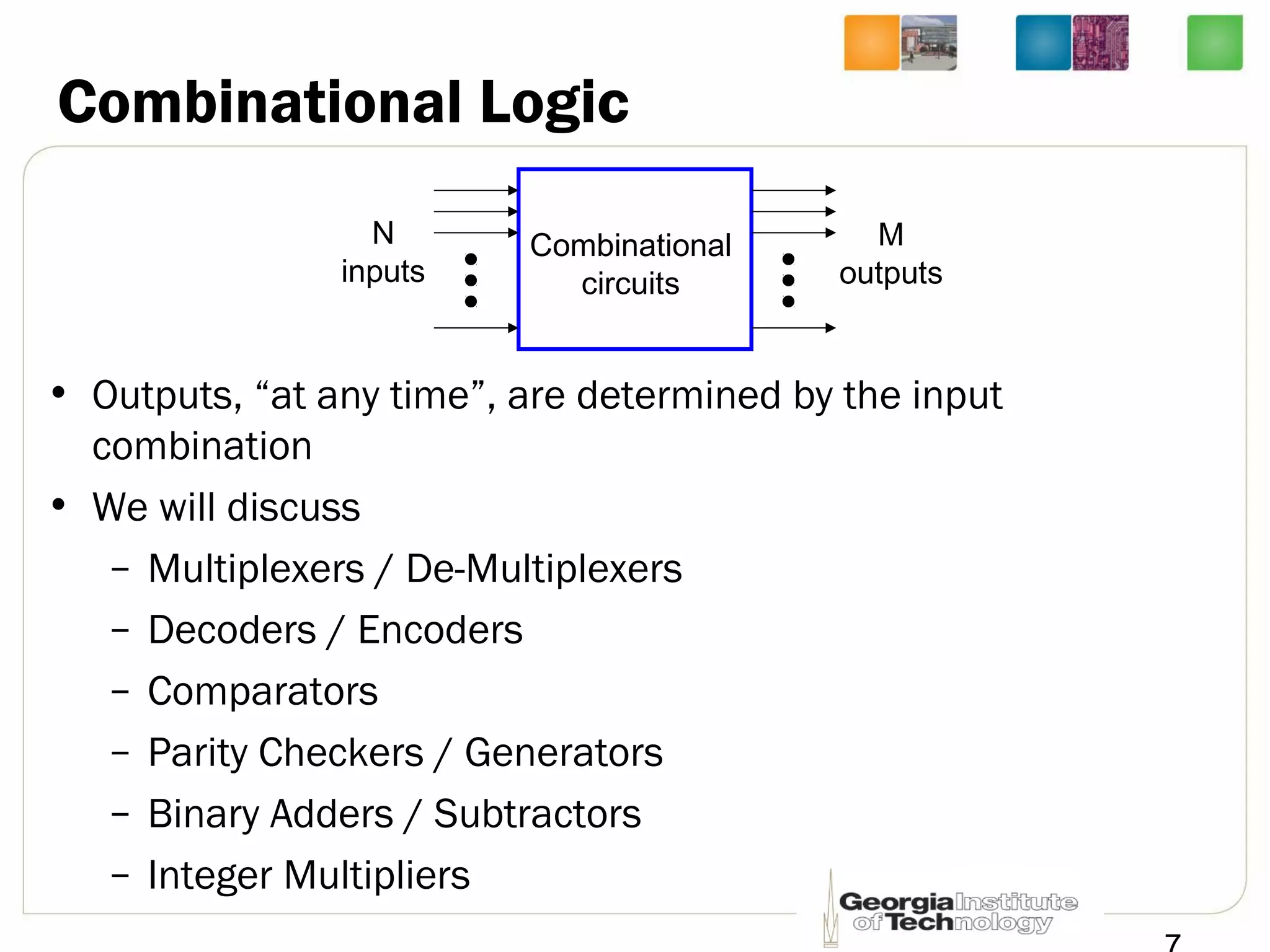

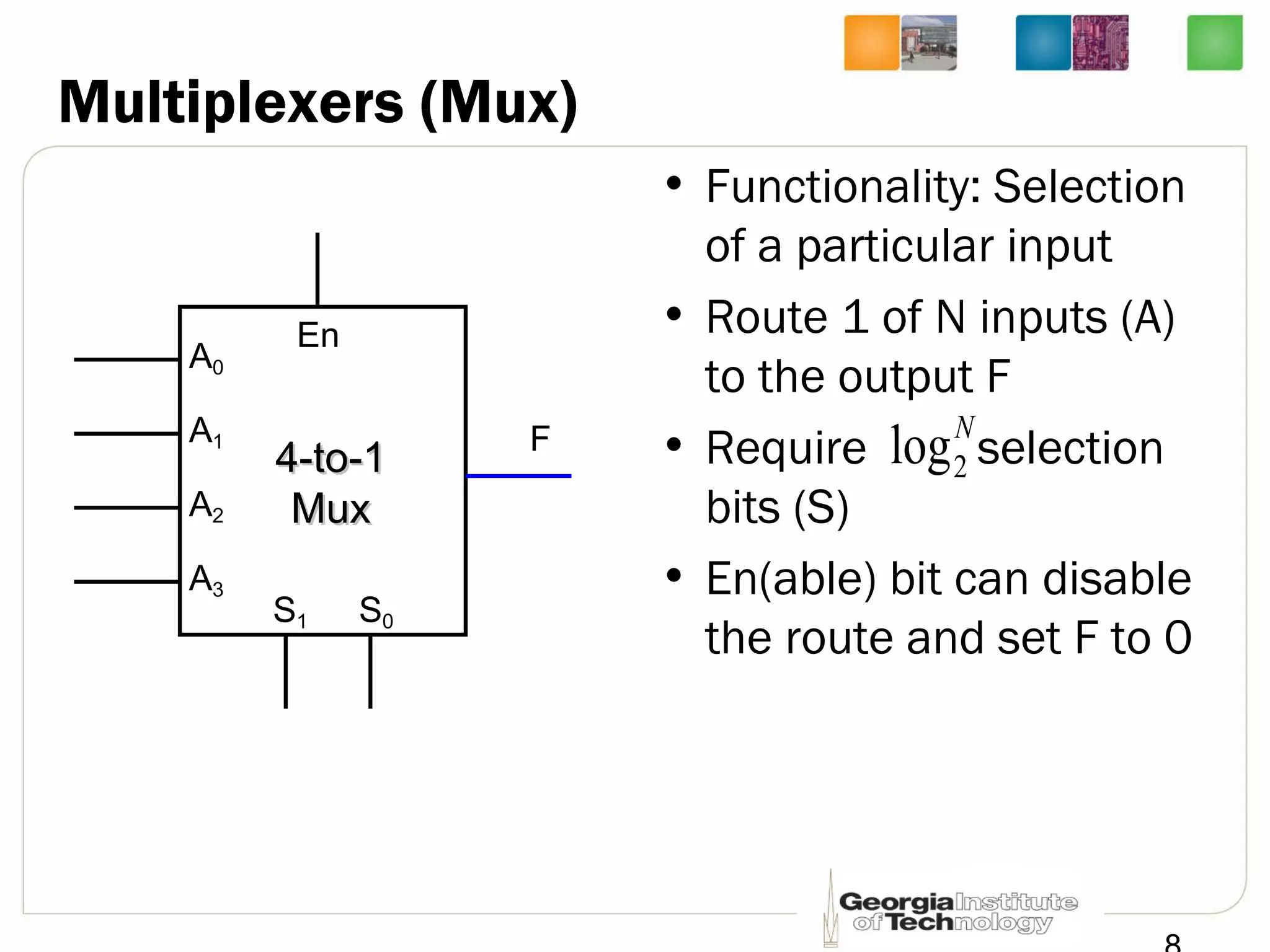

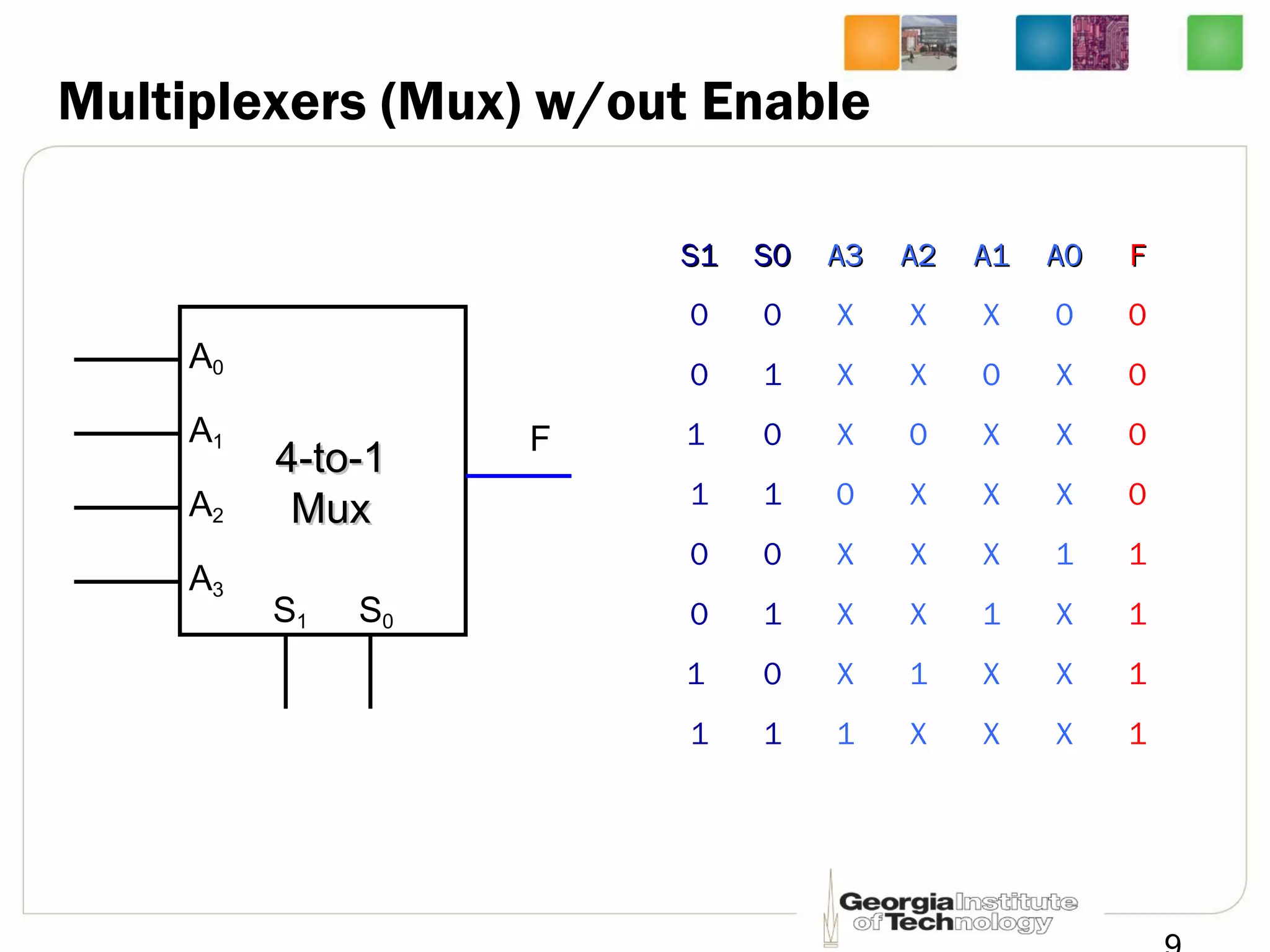

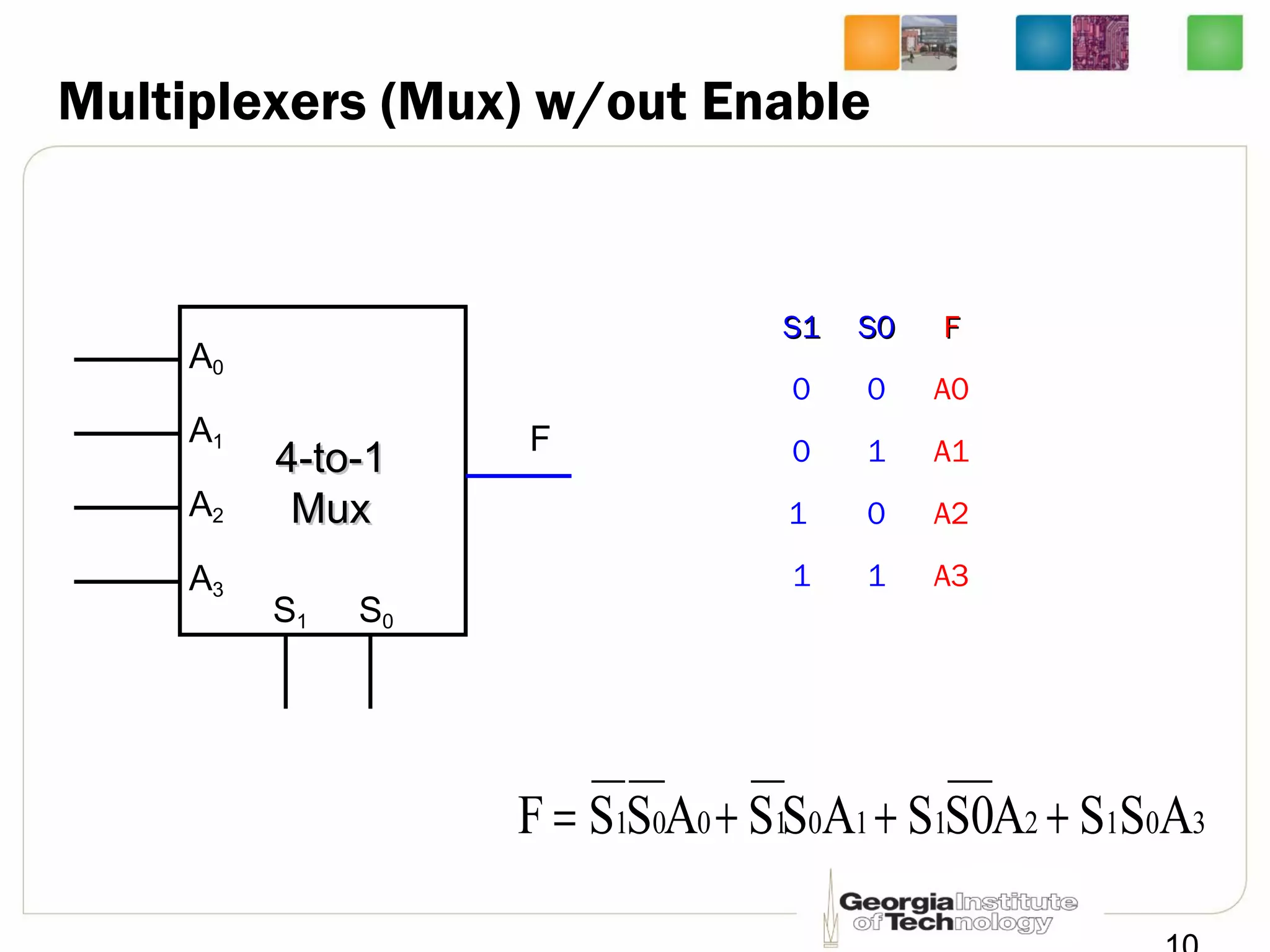

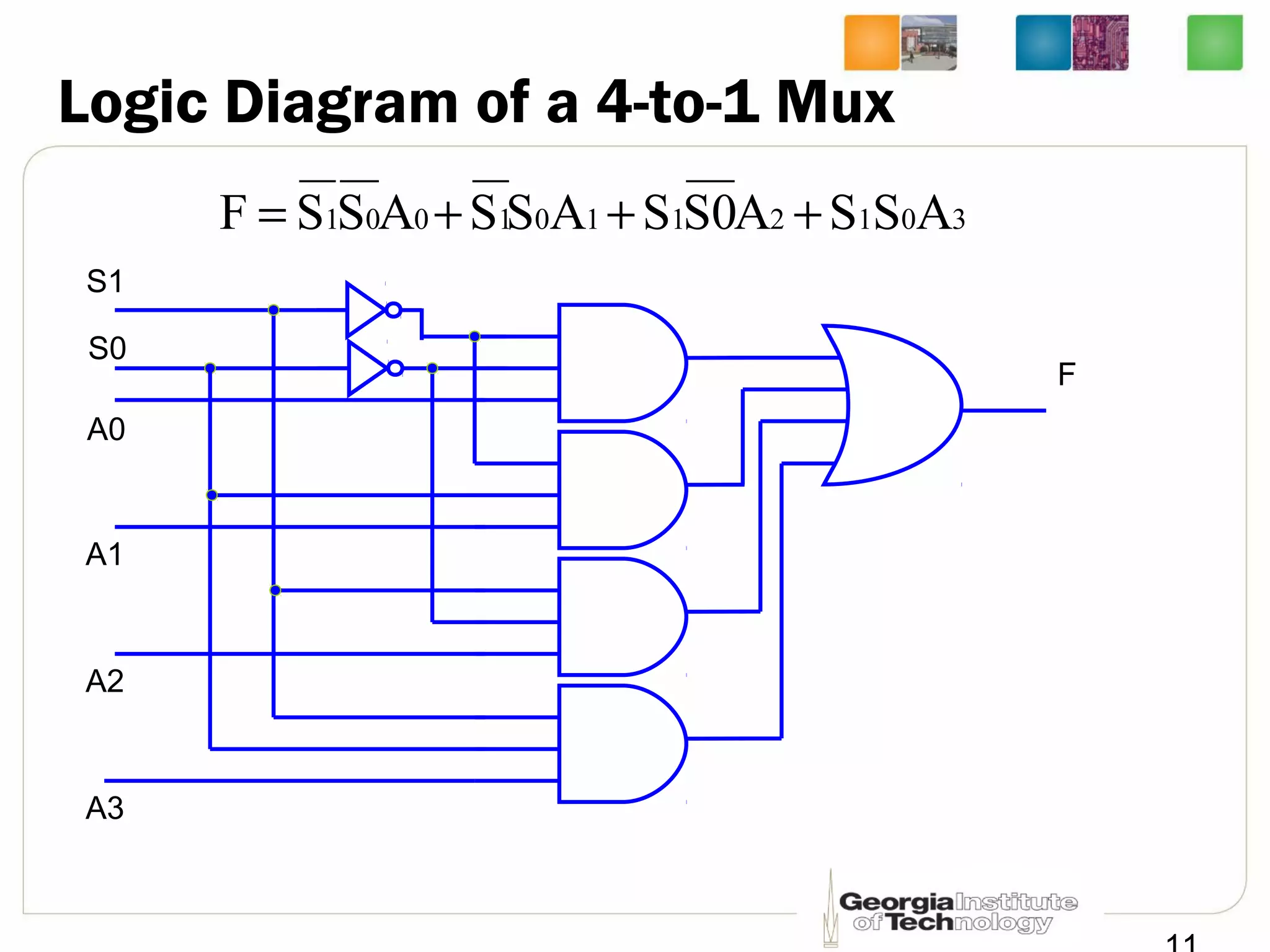

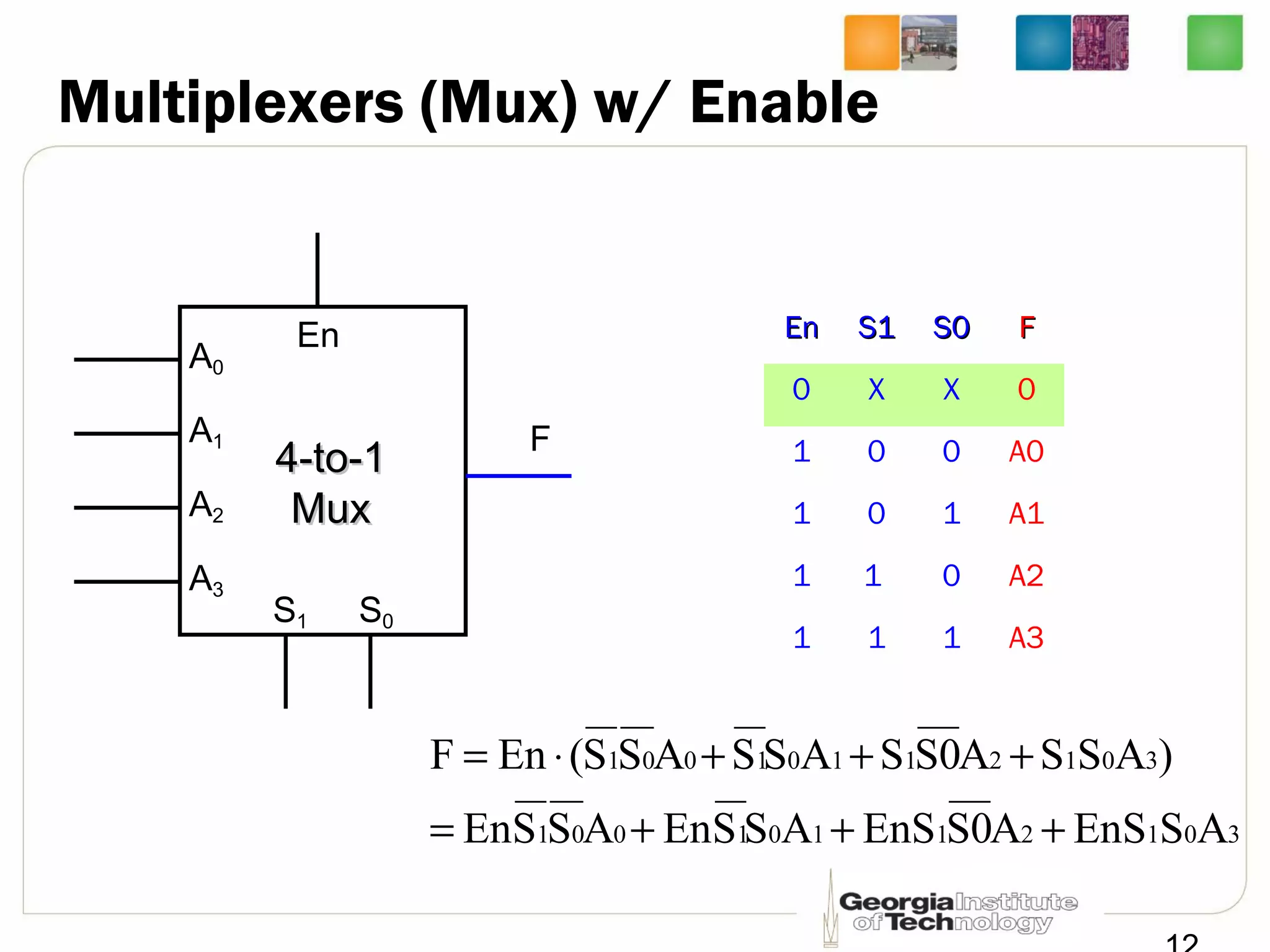

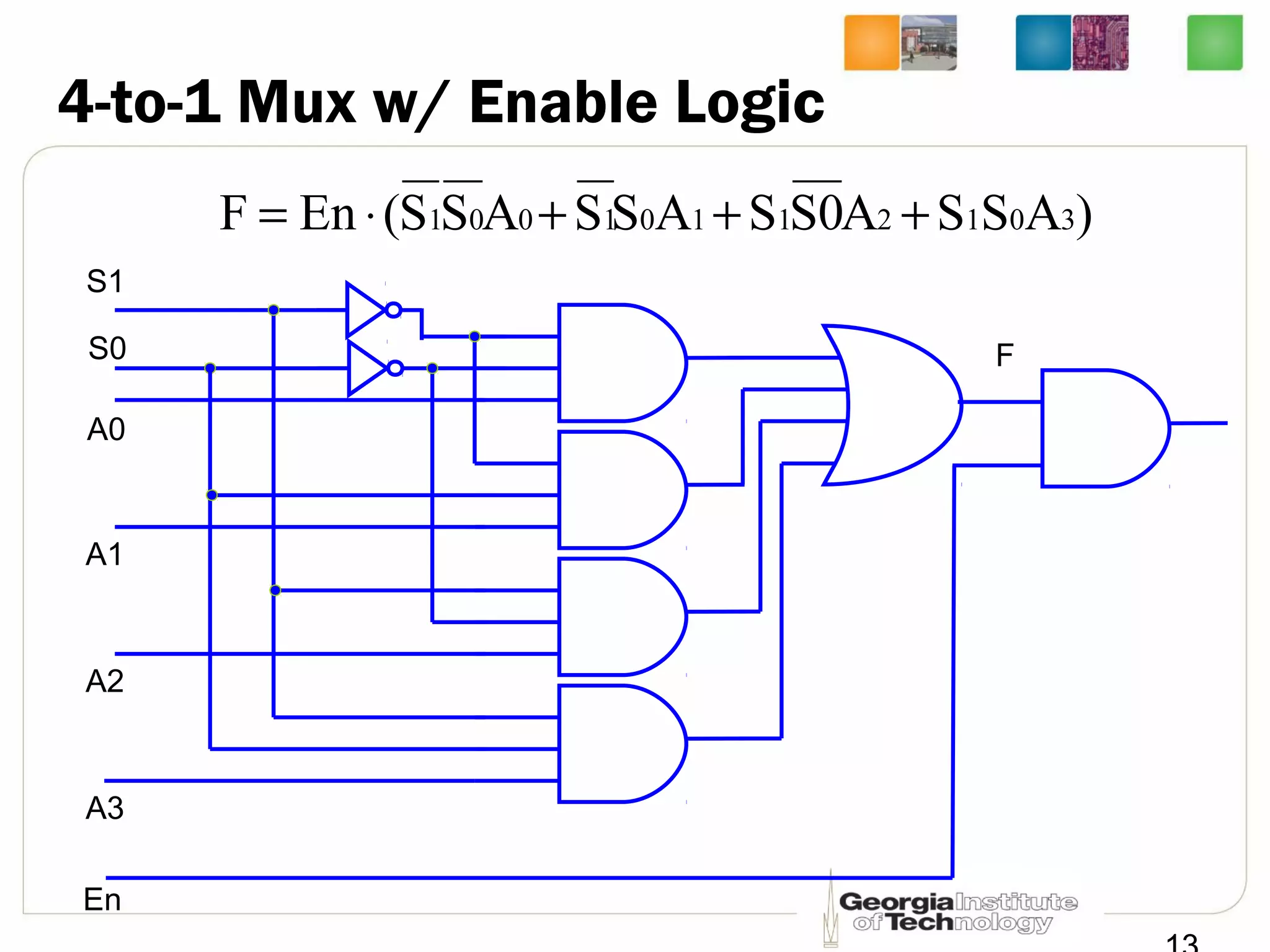

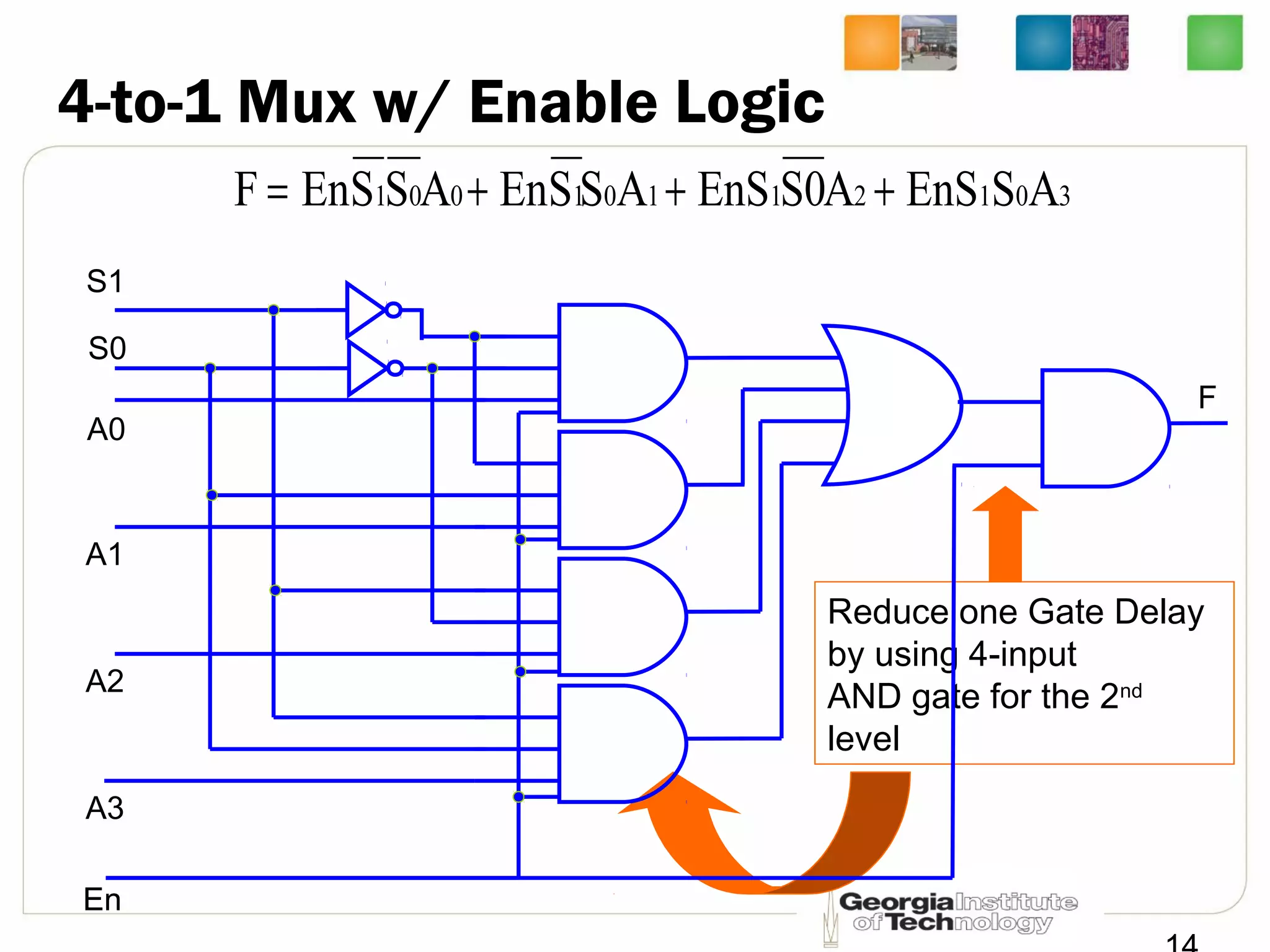

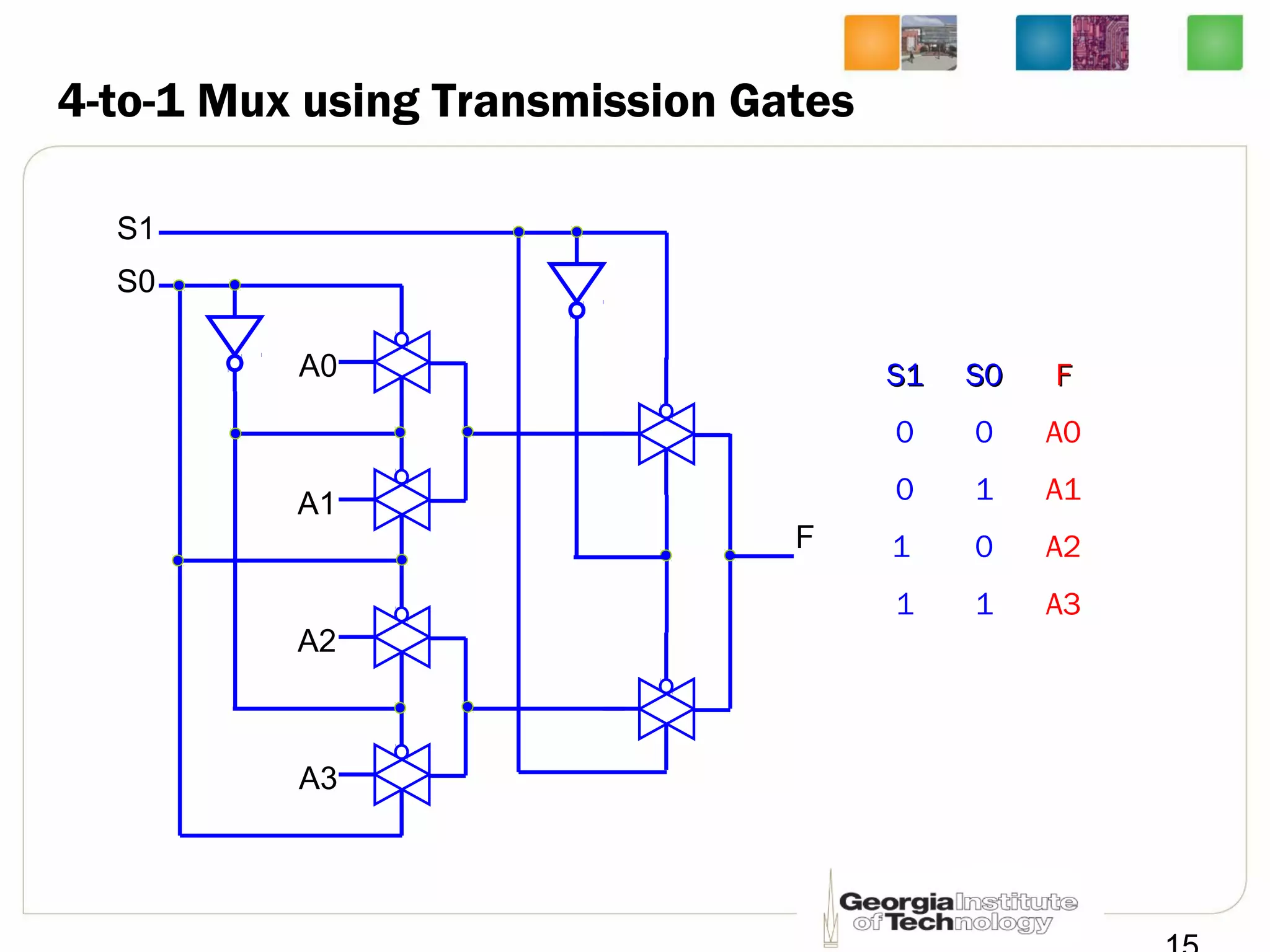

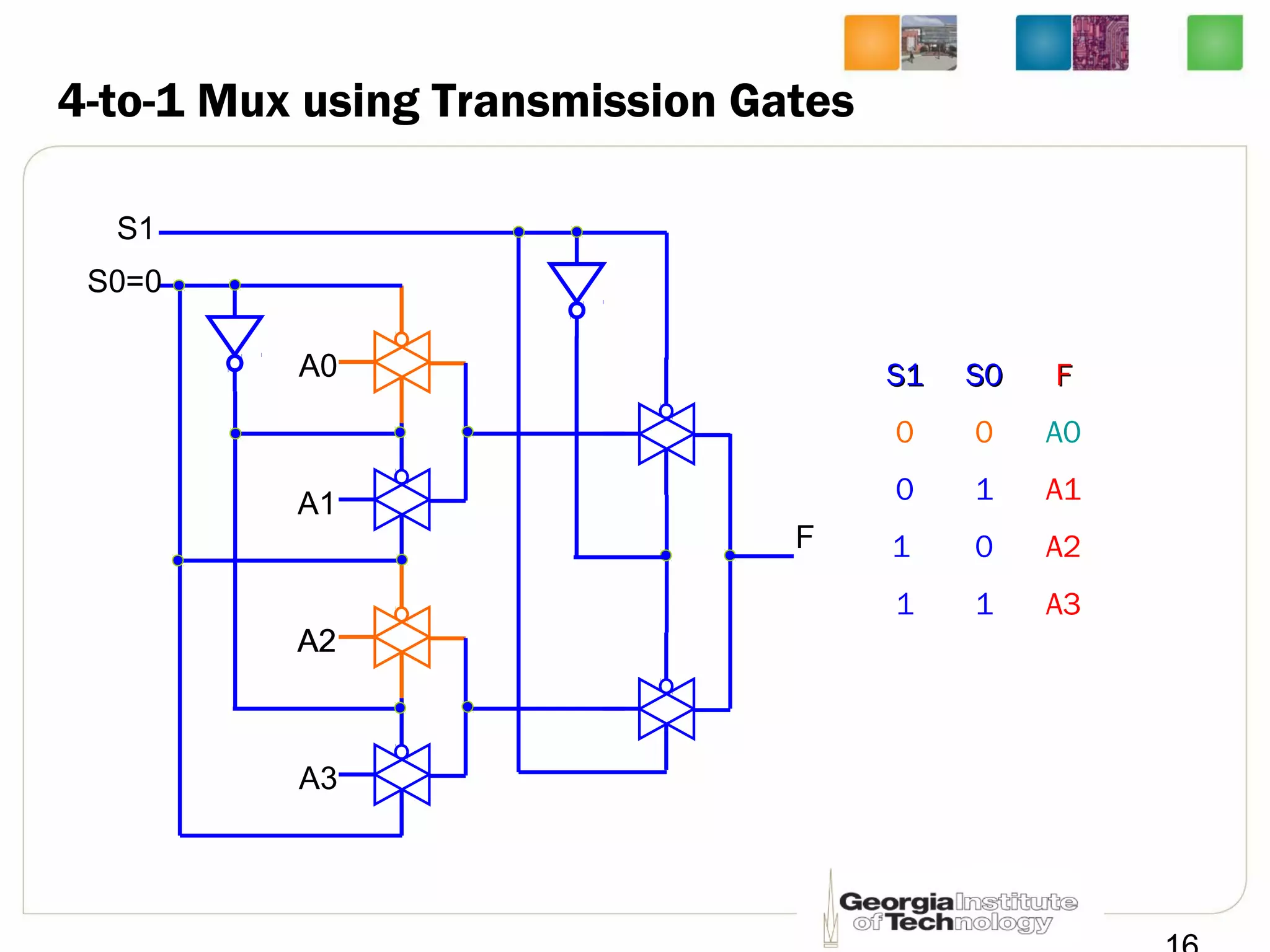

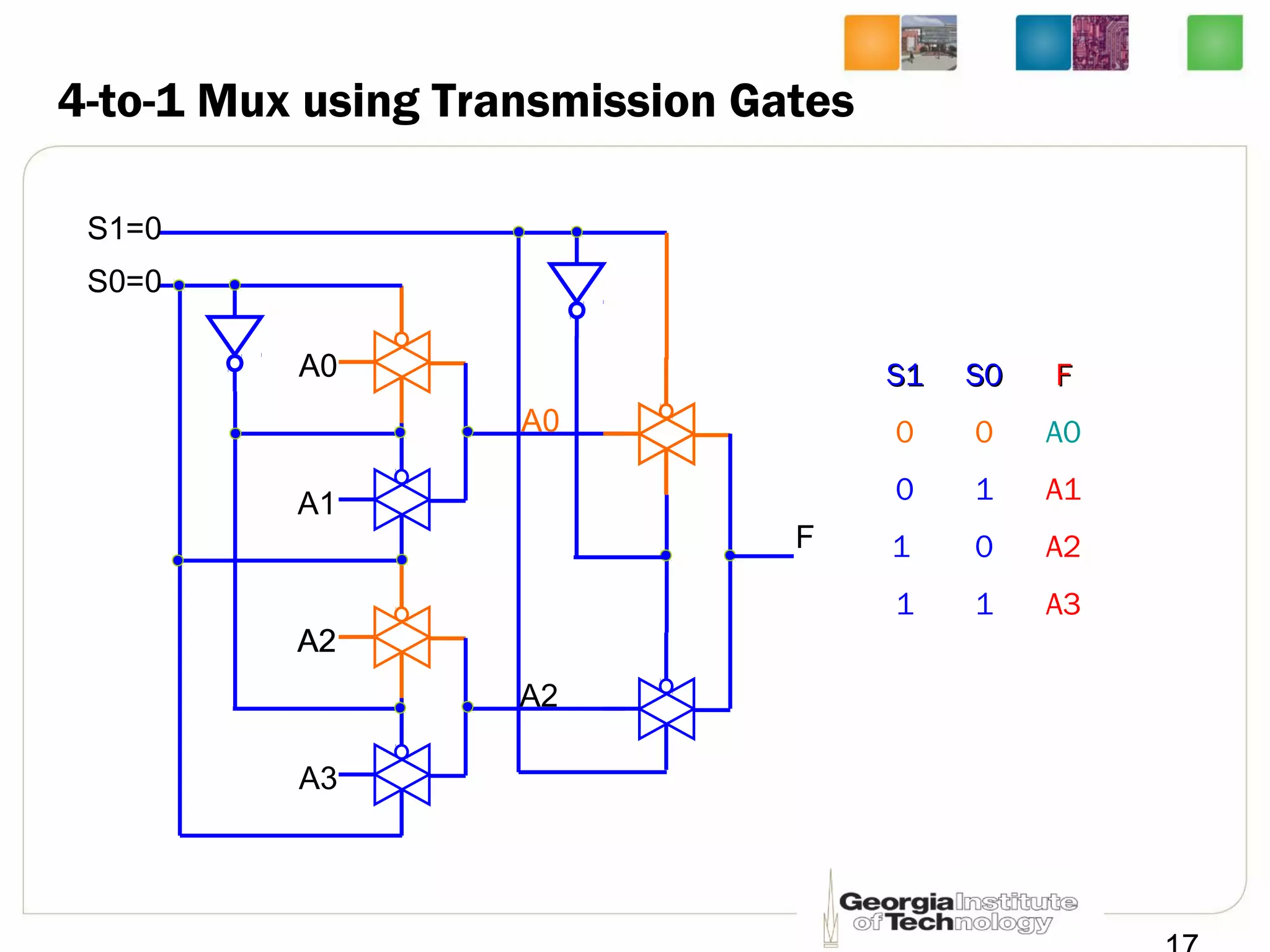

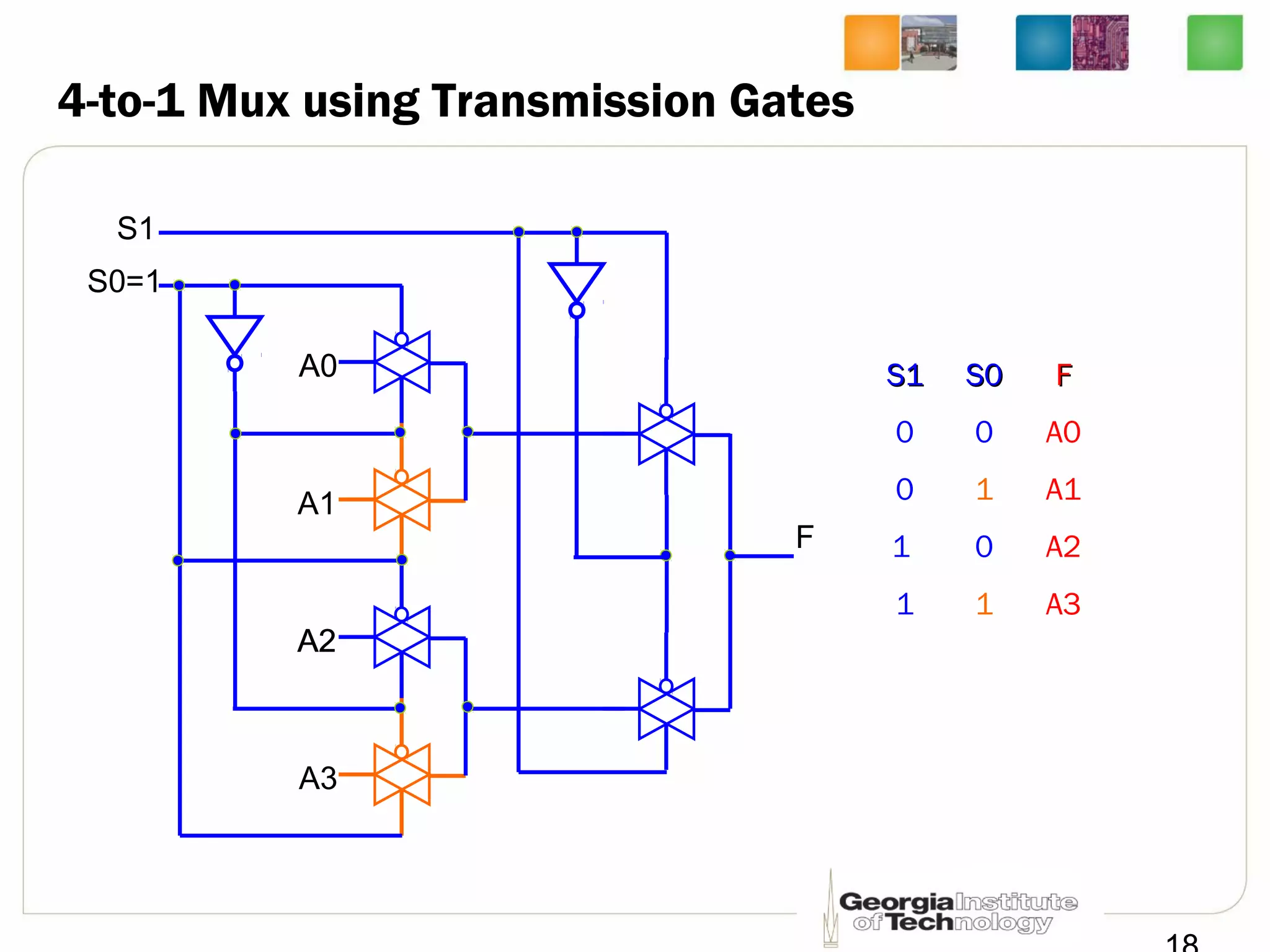

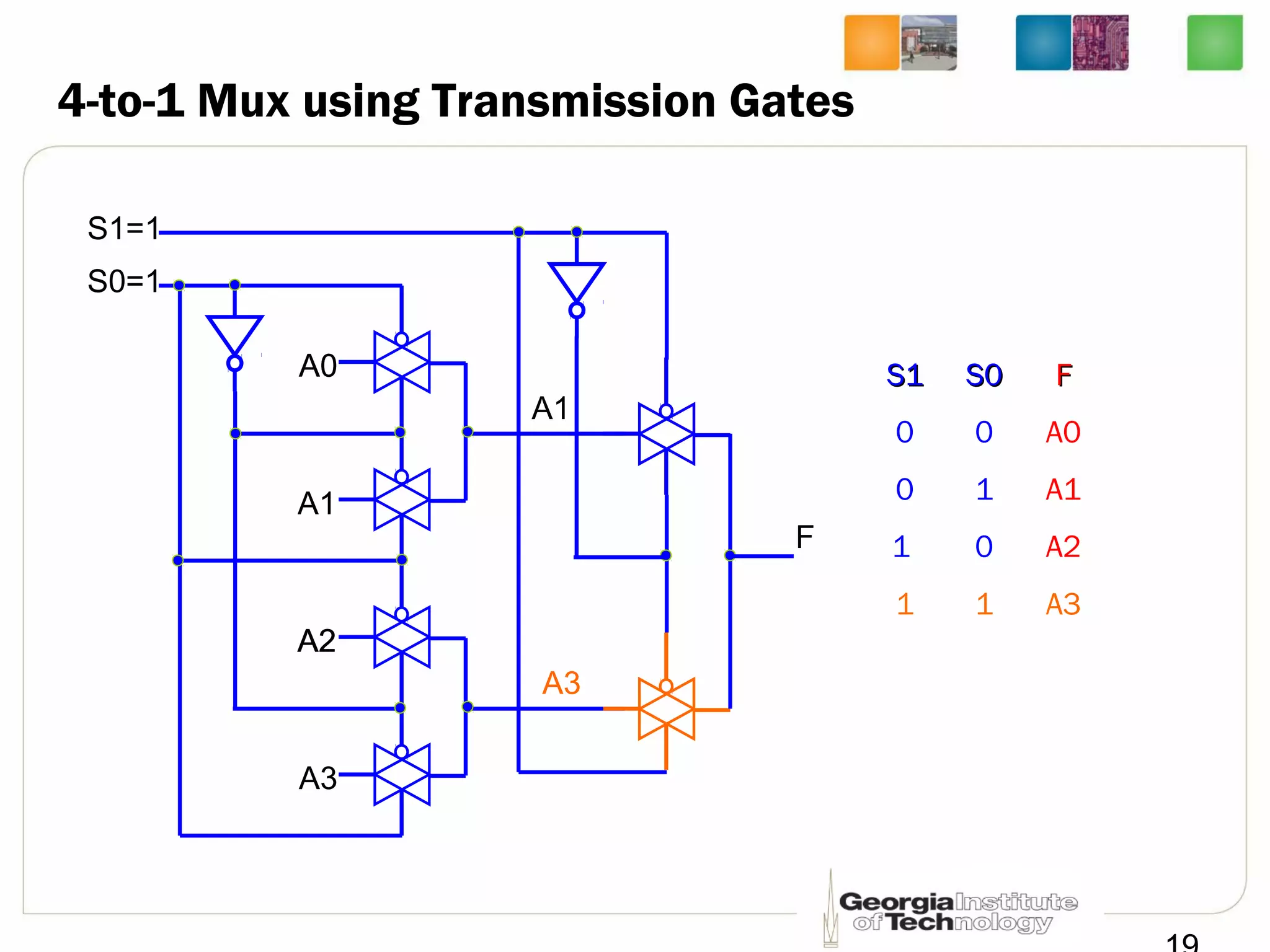

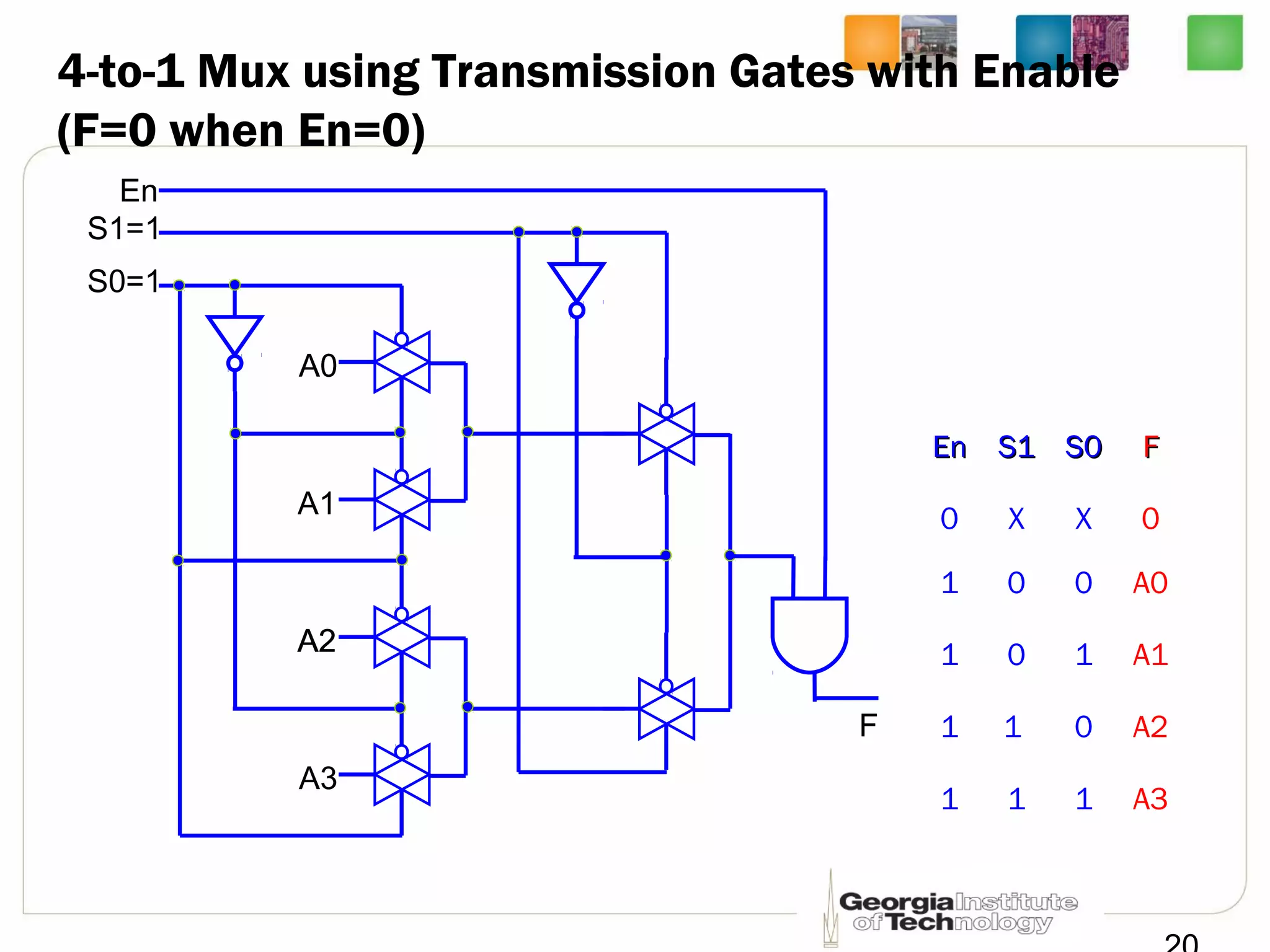

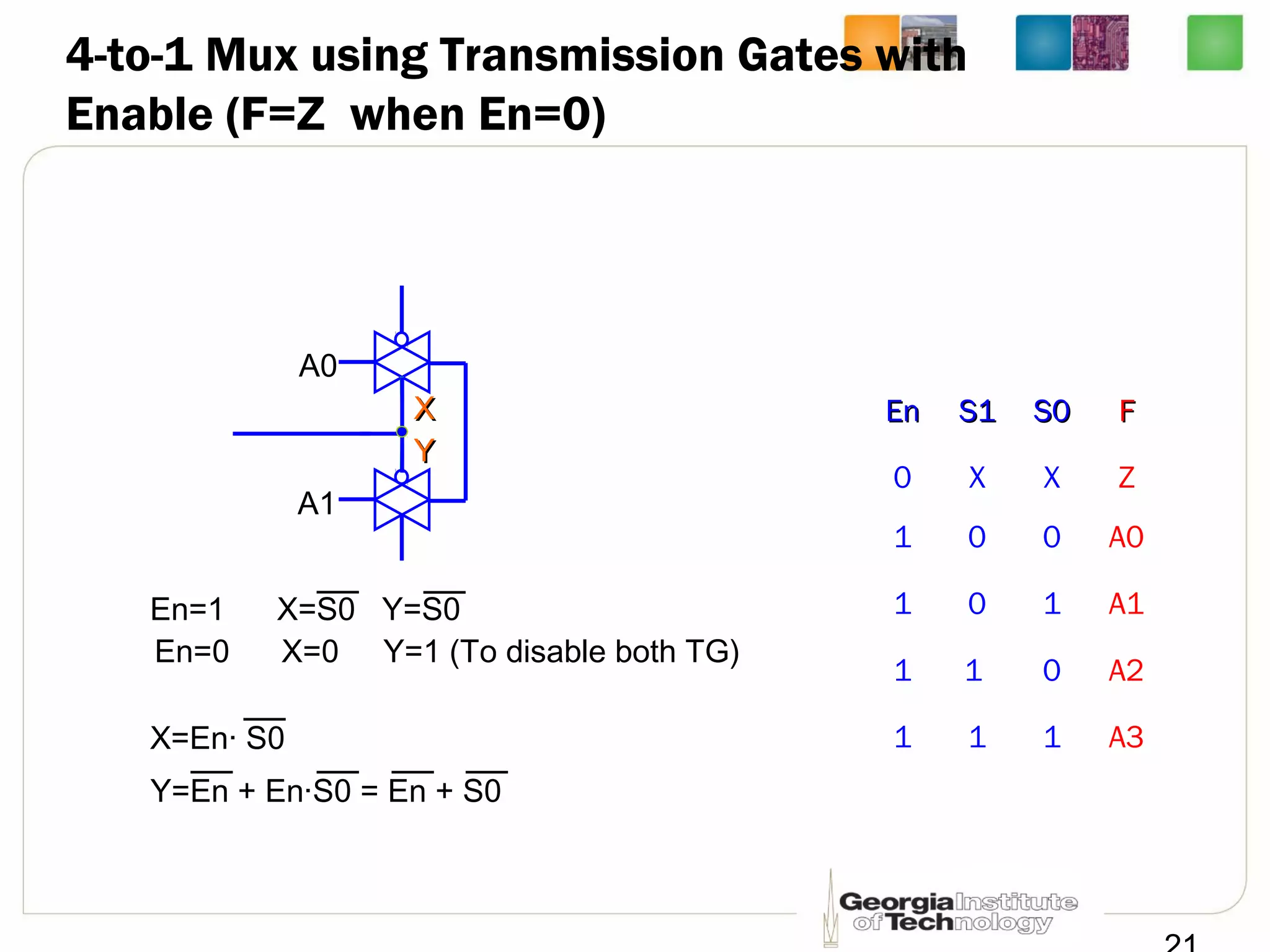

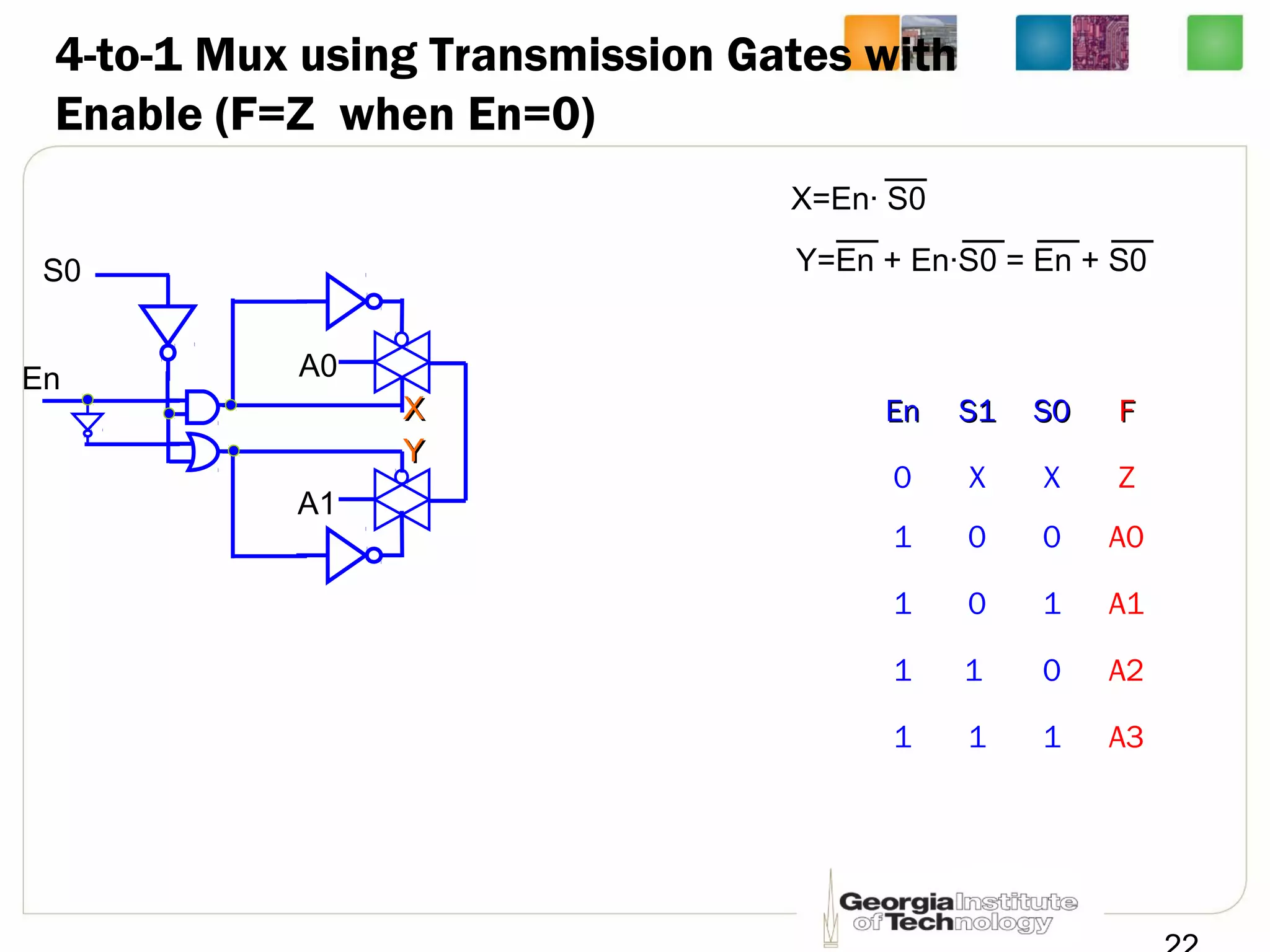

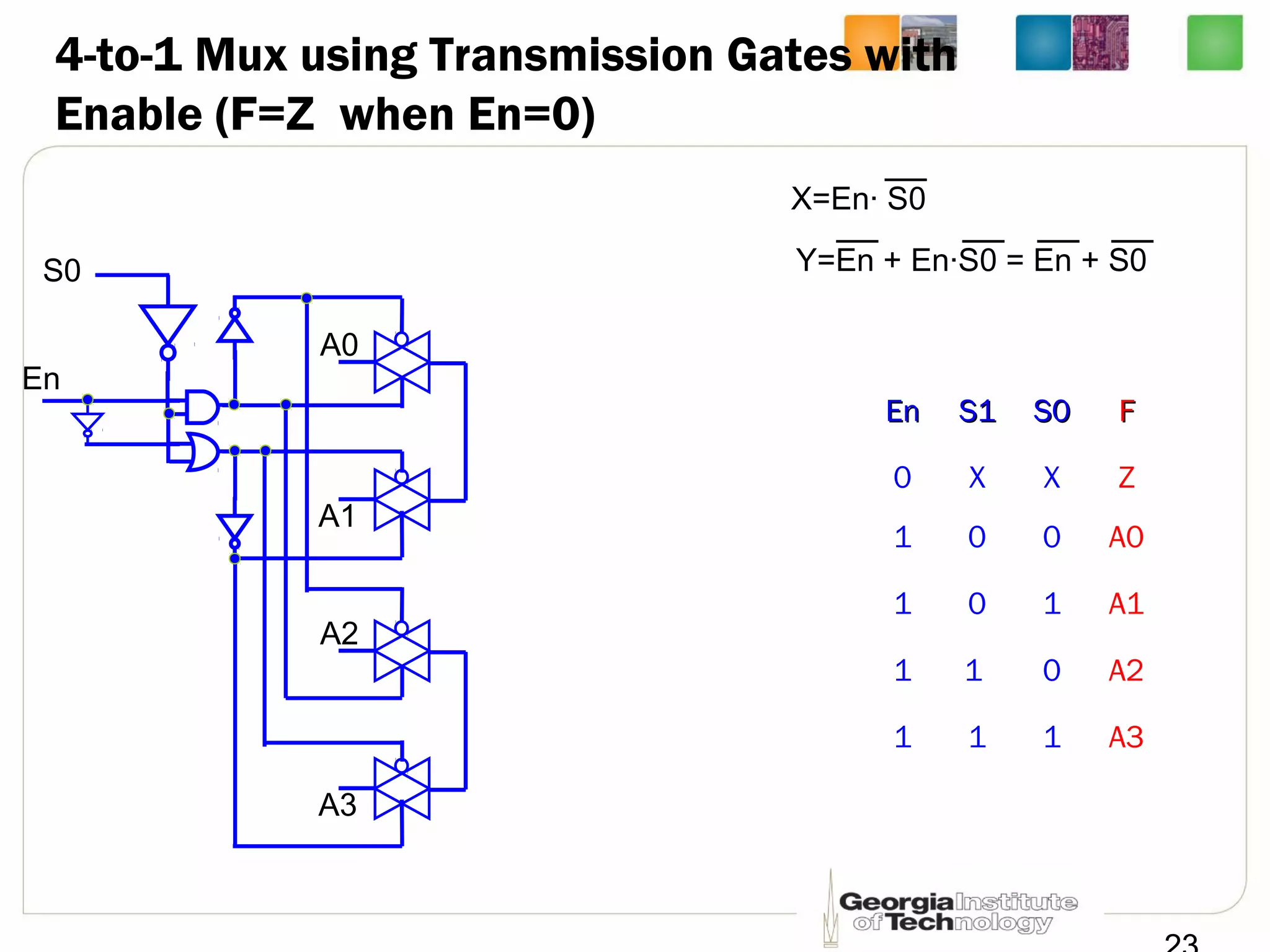

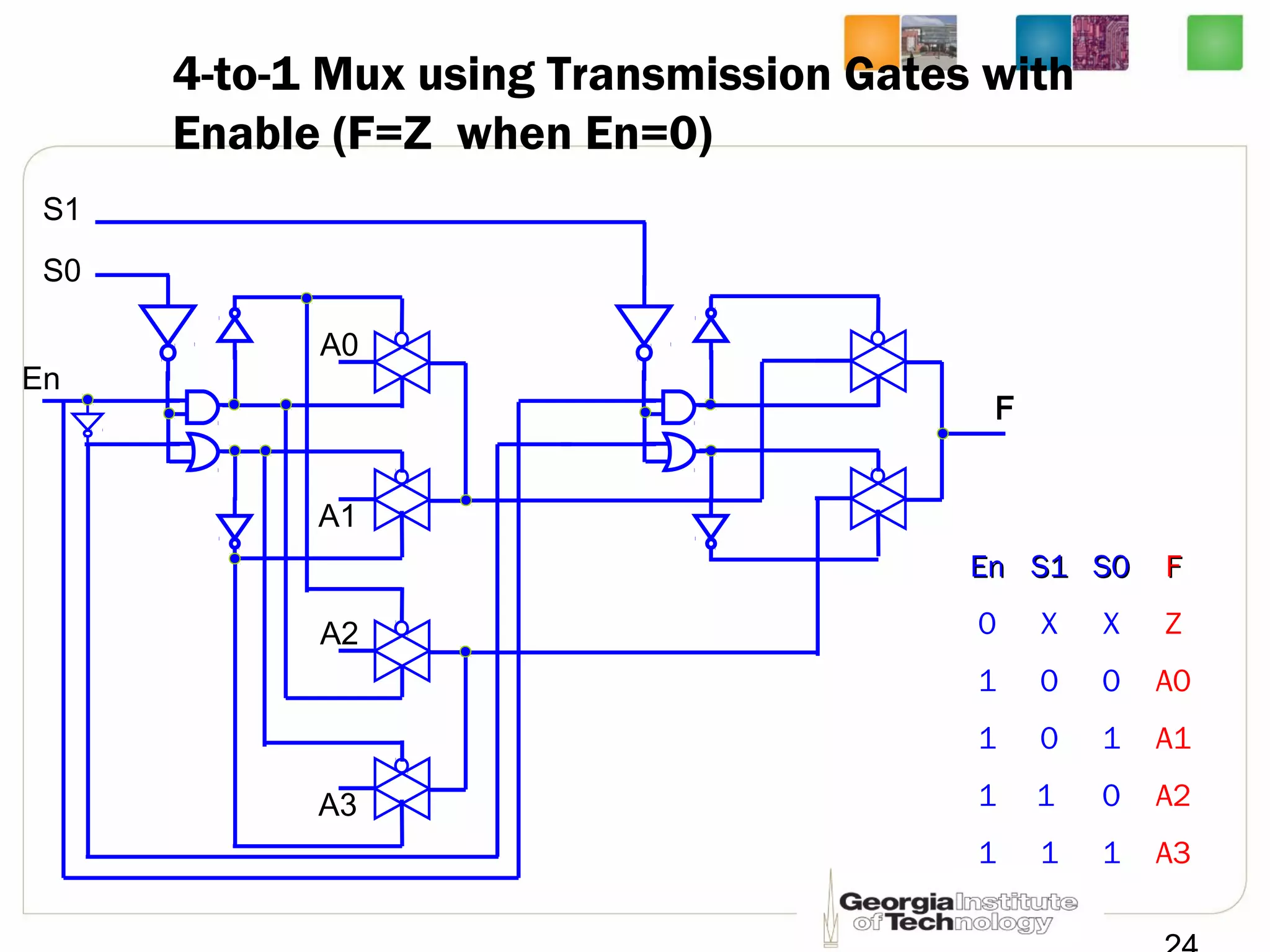

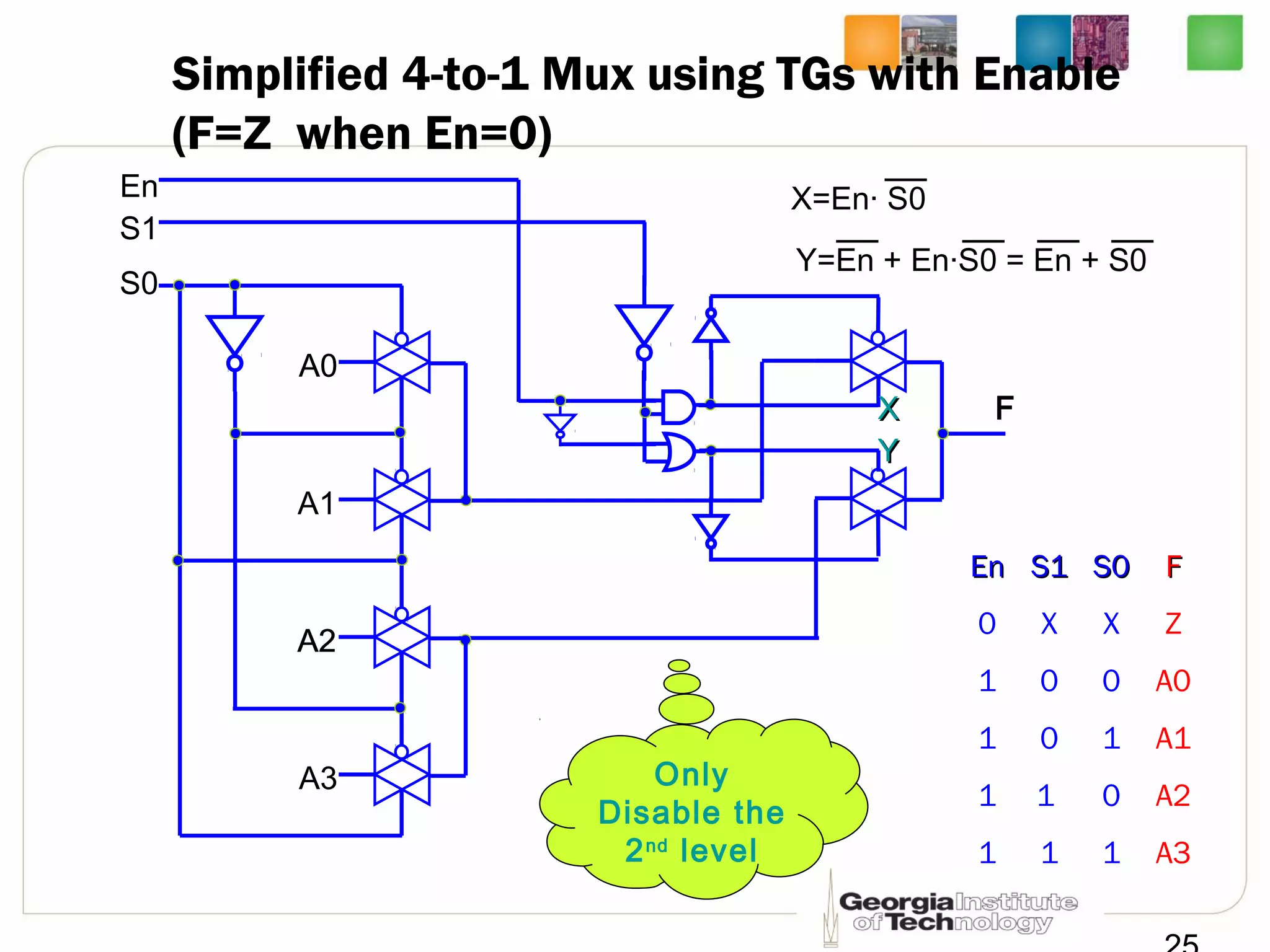

This document provides a summary of a lecture on building blocks for combinational logic, including timing diagrams, multiplexers, and demultiplexers. Timing diagrams are used to describe the functionality of logic circuits over time as a series of waveforms. Multiplexers are used to select one of several input signals to pass to the output based on selection bits. Demultiplexers are the inverse, distributing an input signal to one of several outputs based on the selection bits. Transmission gates can be used to implement multiplexers with enable inputs to disable the output.

![Quadruple 2-to-1 Line Mux

F[3:0]

SEL

En

2-to-12-to-1

MuxMux

(4-bit bus)(4-bit bus)

A3..0

B3..0

A[3:0]

B[3:0]

EnEn SELSEL F[3:0]F[3:0]

0 X 0000

1 0 A[3:0]

1 1 B[3:0]](https://image.slidesharecdn.com/lec10-mux-150829105741-lva1-app6891/75/Lec10-Intro-to-Computer-Engineering-by-Hsien-Hsin-Sean-Lee-Georgia-Tech-Multiplexors-26-2048.jpg)

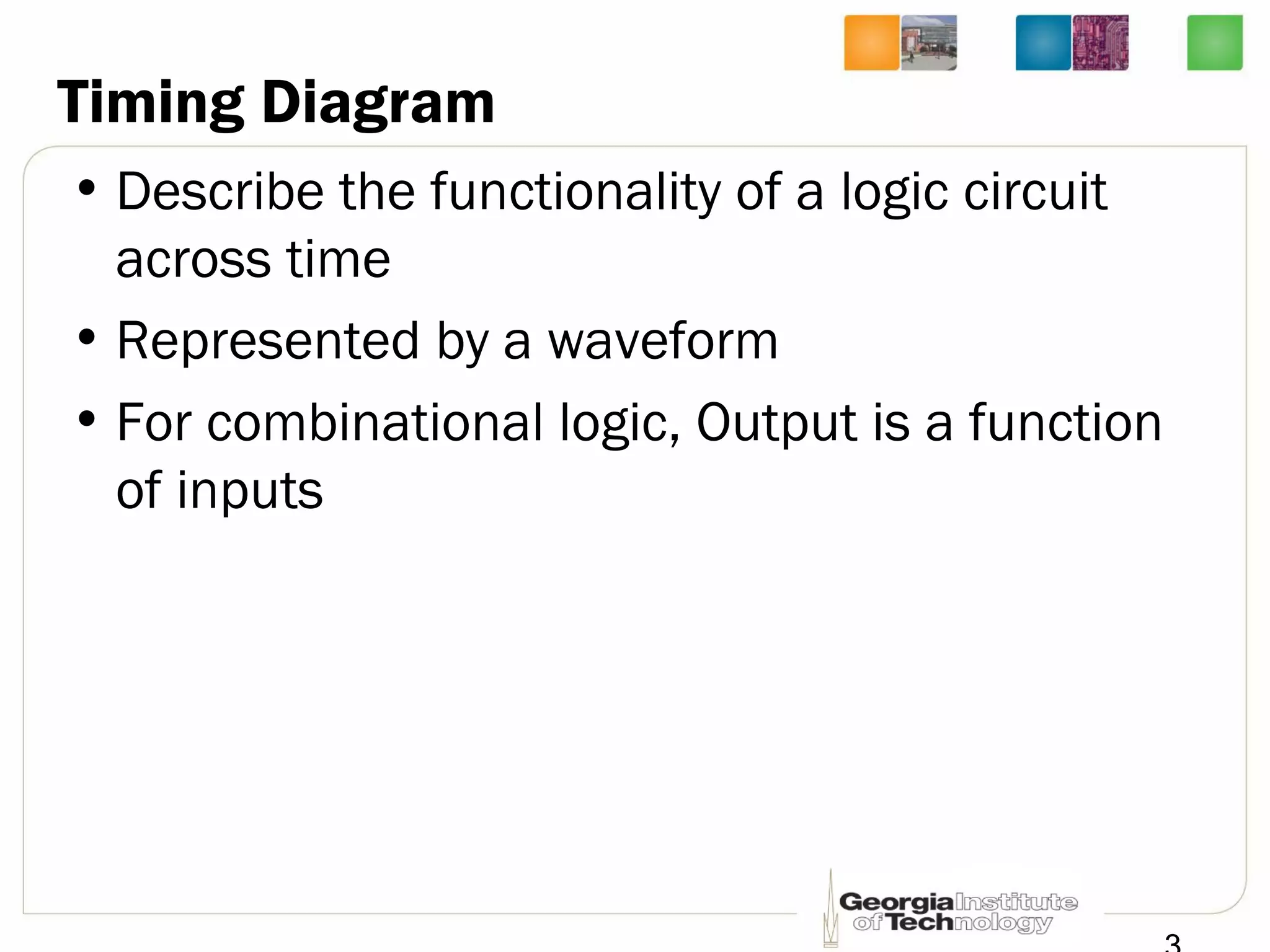

![Quadruple 2-to-1 Line Mux

EnEn SELSEL F[3:0]F[3:0]

0 X 0000

1 0 A[3:0]

1 1 B[3:0]

SEL

B0

A0

F0

B3

A3

F3

B1

A1

F1

B2

A2

F2

En

Fx=Ax·En·SEL+Bx·En·SEL](https://image.slidesharecdn.com/lec10-mux-150829105741-lva1-app6891/75/Lec10-Intro-to-Computer-Engineering-by-Hsien-Hsin-Sean-Lee-Georgia-Tech-Multiplexors-27-2048.jpg)