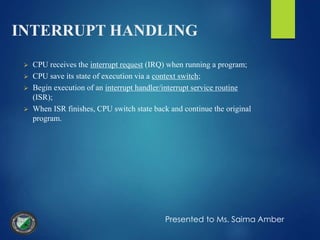

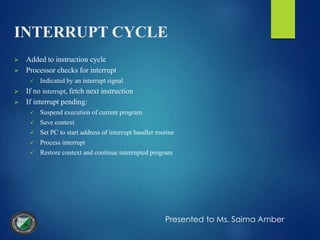

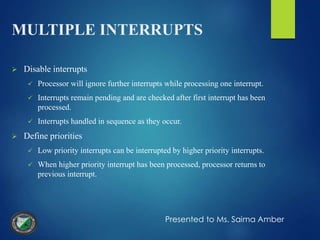

Interrupts are signals that cause the computer's main program to stop and handle the interrupt request. There are different types of interrupts including program errors, timers, and I/O devices. When an interrupt occurs, the CPU saves its state, executes the interrupt handler, then restores its state and continues the original program. Interrupts allow external events and errors to be handled transparently without disrupting program execution.