This document describes the design of an integer and logic unit (ILU) for an 8-bit microprocessor. The ILU will perform arithmetic operations like addition and multiplication as well as logical operations like AND and OR. It will receive input from the memory unit and perform operations as directed by the control unit. To optimize for speed, the ILU will use a carry save adder and Booth multiplier. The ILU will include data, address, and control buses to interface with other units. Its operation will be controlled by control signals from the control unit to perform different functions in single clock cycles.

![Group P

6Mini Project on Integer and Logic Unit

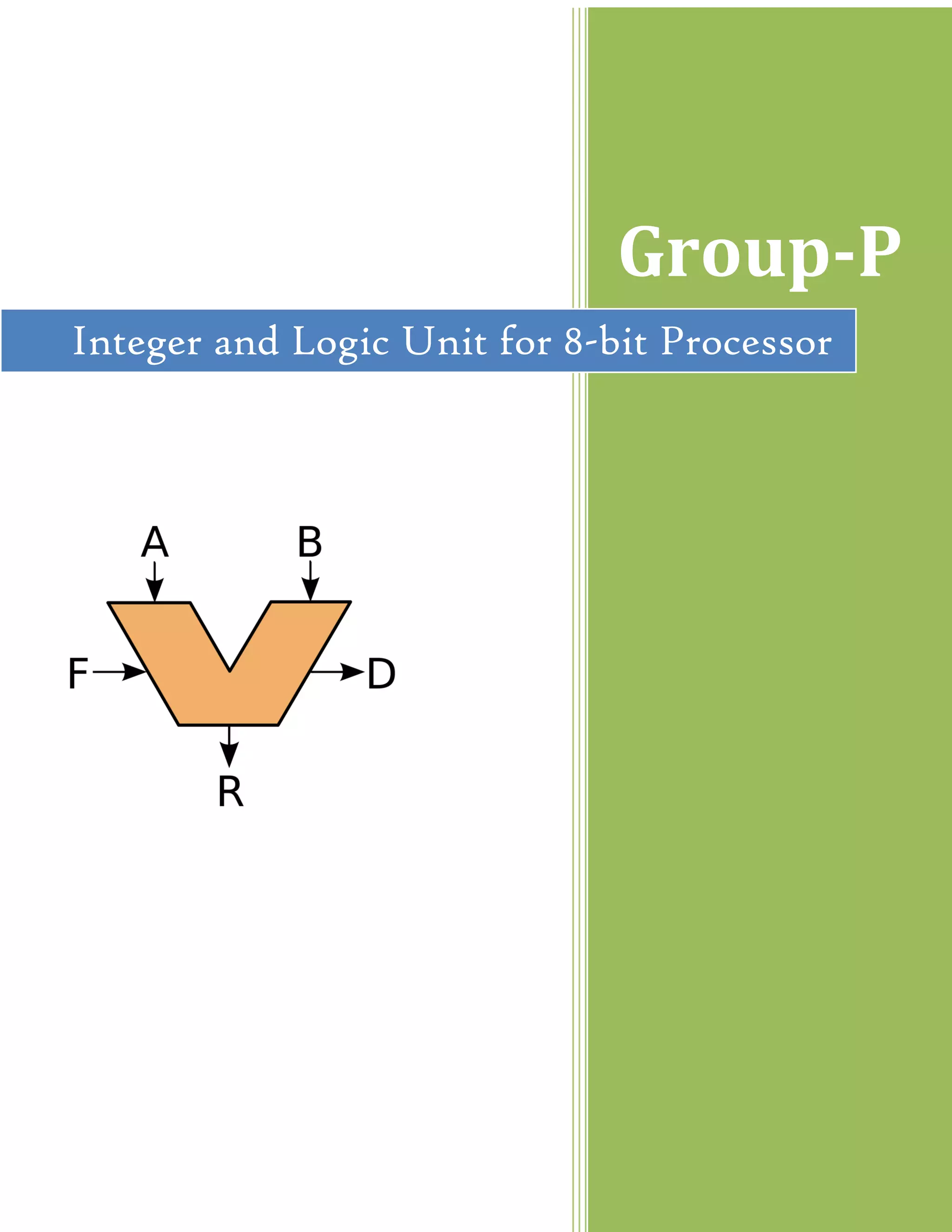

Implementation of Booth Multiplier is relying upon the Wallace tree.

A simple Wallace tree for 4 bit mult is given below for understanding. In our project we will be using a 8

bit Wallace tree.

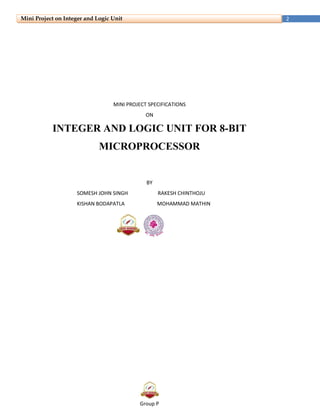

Bus Signals:

Bus signals on ILU are…

3’h0 - Do nothing, complete present operation if any and stay idle

3’h1 – Add signal [1 clock cycle] 3’h2 – Multiply signal [4 clock cycles]

3’h3 - Store the data coming from the data bus into temp 1 register (operand 1) [1 CC]

3’h4 - Store the data coming from the data bus into temp 2 register (operand 2) [1CC]](https://image.slidesharecdn.com/grouppacadvdspec1-140411003419-phpapp02/85/Group-p-6-320.jpg)

![Group P

7Mini Project on Integer and Logic Unit

3’h5 - Read flag register [1CC] (As soon as the control signal in the same clock cycle the flag status is put

on the one bit bus between ILU and CU.)

3’h6 - Put the data of the result on the data bus. [1 cc]

3’h7-Logical OR operation.[1cc]

3’h8-Logical AND operation.[1cc]

*Timing Diagram of ILU*

Note: This timing diagram is only for MUL operation.](https://image.slidesharecdn.com/grouppacadvdspec1-140411003419-phpapp02/85/Group-p-7-320.jpg)