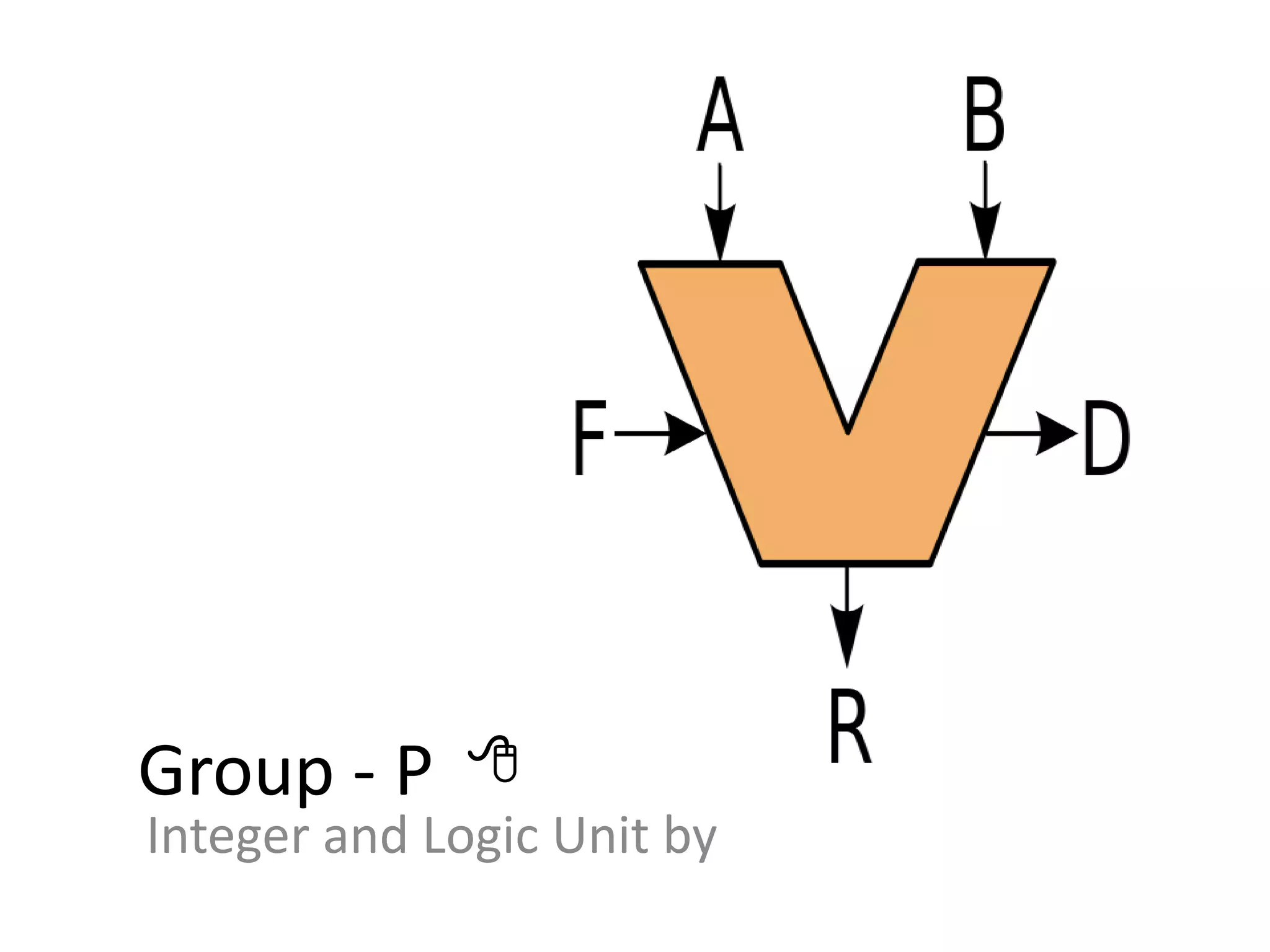

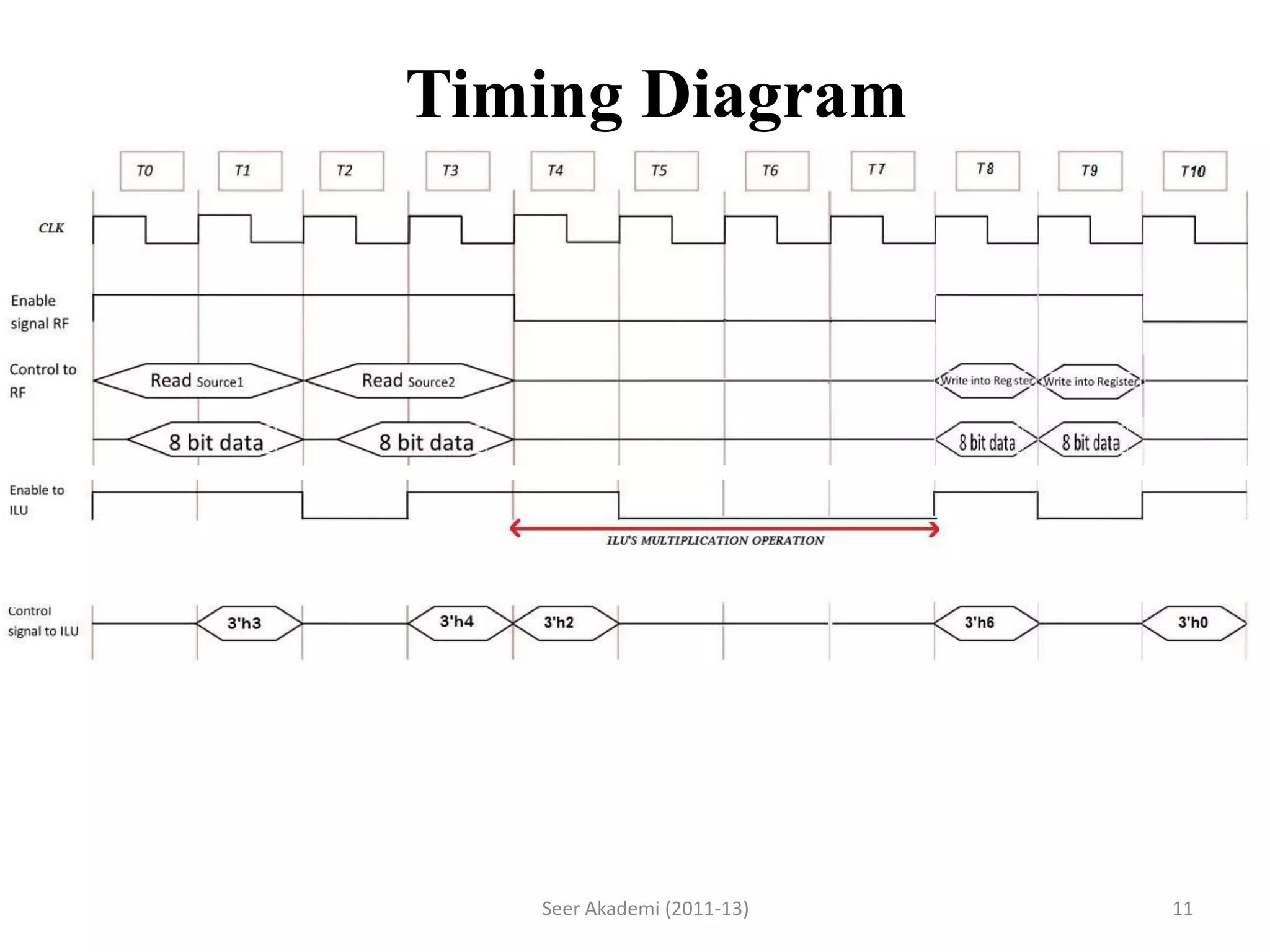

The document discusses an integer and logic unit used in microprocessors. It describes how the unit performs integer and logic operations like addition, multiplication, OR, and AND. It specifically mentions using a carry save adder for addition with 3 inputs and a Booth multiplier for high-speed multiplication. The document also provides details on an arithmetic logic unit (ALU), bus concept, input/output representation, interaction with other units, carry save adders, Booth multipliers, logic gates, and timing diagrams.