More Related Content

PPTX

PPTX

PDF

Misc for edge_devices_with_fpga PDF

OSC 2012 Hokkaido でのプレゼン資料 PDF

モバイル(エッジ)向け ニューラルネットワーク推論エンジンの紹介 PDF

FPGAによる津波シミュレーション -- GPUを超える高性能計算の手法 PDF

PDF

What's hot

PDF

110709 3rd SyoueneIT Workshop ARMServer PDF

ディープラーニングの社会実装の鍵となるエッジコンピューティング PDF

Ncnn a universal and efficient neural network inference with vulkan PPTX

PDF

Gpu deep learning community設立について0913 PDF

LTE-M/NB IoTを試してみる nRF9160/Thingy:91 PDF

PDF

PDF

PDF

PDF

モバイル向けニューラルネットワーク推論エンジンの紹介 PDF

2015年度GPGPU実践基礎工学 第15回 GPGPU開発環境�(OpenCL) PPTX

PDF

PPTX

Windowsの節電 .NETラボ勉強会 2011/4/23 PPTX

Abstracts of FPGA2017 papers (Temporary Version) PDF

2015年度GPGPU実践基礎工学 第14回 GPGPU組込開発環境 PDF

Automatic Mixed Precision の紹介 PDF

2015年度GPGPU実践基礎工学 第1回 学際的分野における先端シミュレーション技術の歴史 PDF

Viewers also liked

PDF

PDF

IEICE technical report (RECONF), January 2013. PDF

CMPP 2012 held in conjunction with ICNC’12 PDF

3bOS: A flexible and lightweight embedded OS operated using only 3 buttons PDF

A survey of how to efficiently implement application-specific hardware on an ... PDF

FACE: Fast and Customizable Sorting Accelerator for Heterogeneous Many-core S... PDF

FPGAを用いた世界最速のソーティングハードウェアの実現に向けた試み PDF

多数の小容量FPGAを用いた スケーラブルなステンシル計算機の開発 PDF

FPGAベースのソーティングアクセラレータの設計と実装 PDF

PDF

A High-speed Verilog HDL Simulation Method using a Lightweight Translator Similar to Fully-Functional FPGA Prototype with Fine-Grain Programmable Body Biasing (FPGA2013)

PPTX

PDF

PDF

PDF

PPTX

PPTX

研究者のための Python による FPGA 入門 PDF

2値ディープニューラルネットワークと組込み機器への応用: 開発中のツール紹介 PDF

PDF

ACRi_webinar_20220118_miyo PPTX

PPTX

PDF

FPGAをロボット(ROS)で「やわらかく」使うには PPT

PDF

PDF

Synthesijer.Scala (PROSYM 2015) PPTX

Androidとfpgaを高速fifo通信させちゃう PDF

High-speed Sorting using Portable FPGA Accelerator (IPSJ 77th National Conven... PDF

PDF

PPTX

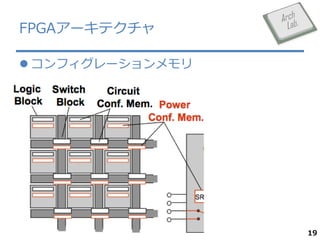

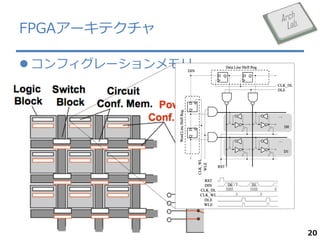

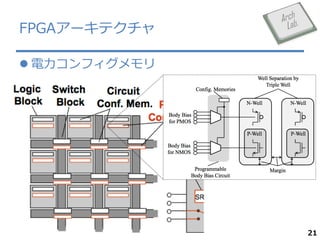

Fpga programming introduction Fully-Functional FPGA Prototype with Fine-Grain Programmable Body Biasing (FPGA2013)

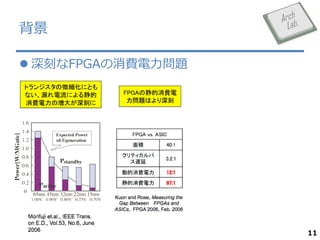

- 1.

2014年1月25日 14:30 –15:00

FPGA2013論文紹介@東工大

Fully-Functional FPGA Prototype

with Fine-Grain Programmable

Body Biasing

著者:Masakazu Hioki(産総研), et al.

発表者:小林諒平(東工大)

- 2.

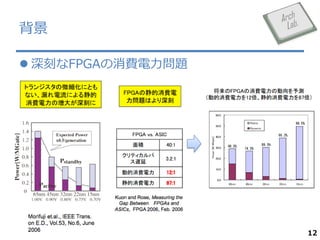

- 3.

- 4.

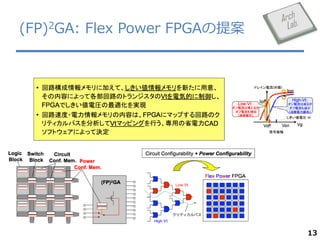

- 5.

- 6.

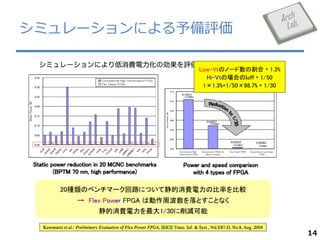

- 7.

- 8.

- 9.

- 10.

- 11.

- 12.

- 13.

- 14.

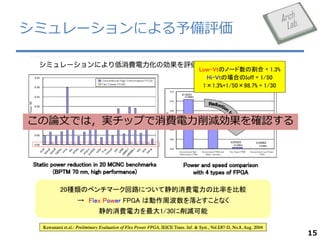

- 15.

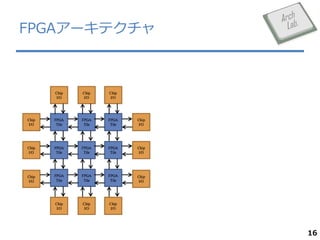

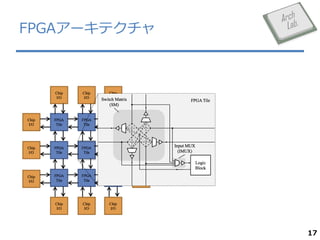

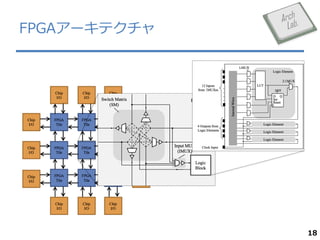

- 16.

- 17.

- 18.

- 19.

- 20.

- 21.

- 22.

- 23.

- 24.

- 25.

- 26.

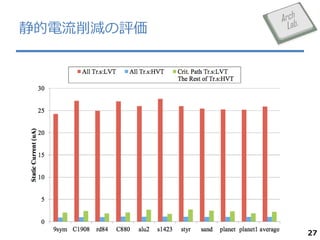

- 27.

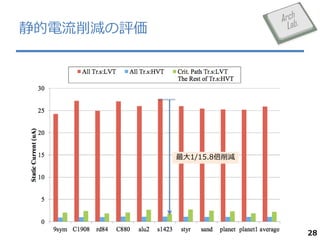

- 28.

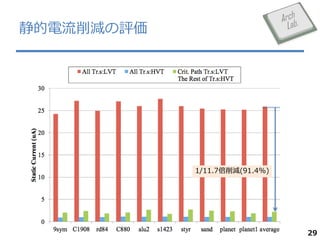

- 29.

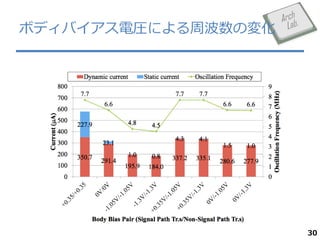

- 30.

- 31.

- 32.

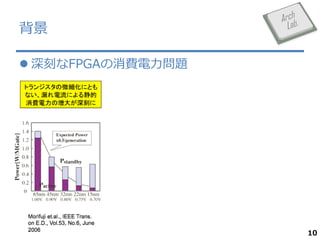

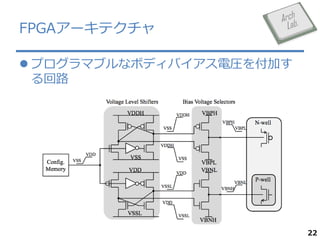

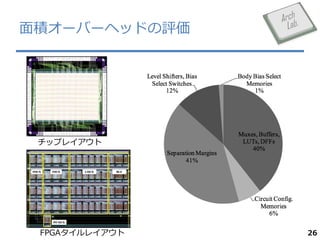

結論

Flex PowerFPGAを実チップに起こして評価し

た

静的消費電力を大幅に削減:平均91.4%

ボディバイアス電圧のペアが(+0.35V/-1.3V)の時,

全体の電流はたった8%の増加に対して周波数は17%

向上(0V/0Vと比べて: すべてのMOSFETをHVTにし

たとき)

31